Werbung

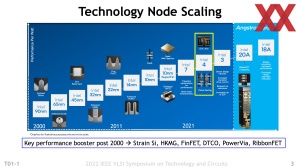

Auf dem 2022 IEEE VLSI Symposium hat Intel einen Vortrag zur Fertigung in Intel 4, dem 4-nm-Prozess, gehalten. Intel 4 wird für zahlreiche kommenden Prozessoren zum Einsatz kommen, allen voran Meteor Lake. Der Nachfolger Intel 3 wird designkompatibel zu Intel 4 sein, so dass für Intel 4 vorgesehene Produkte auch auf Intel 3 umgezogen werden können. Für Granite Rapids und Sierra Forrest wird Intel genau dies tun, denn zumindest Granite Rapids war einmal für Intel 4 vorgesehen, wird nun aber in 2024 in Intel 3 gefertigt werden.

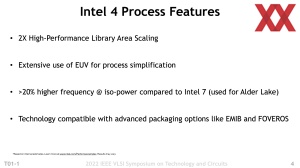

Die Kerndaten für Intel 4 sind:

- Skalerierung der Transistordichte für High-Performance-Bibliotheken um den Faktor zwei

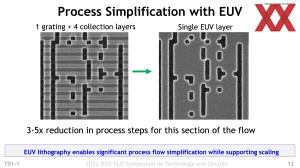

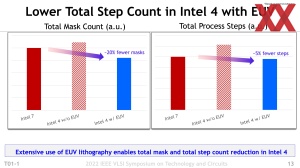

- Nutzung von EUV für fast alle Prozessschritte, um deren Anzahl zu reduzieren

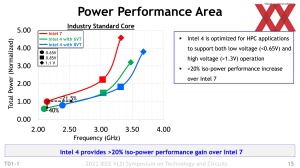

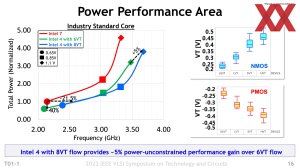

- bei gleicher Leistungsaufnahme soll Intel 4 um 20 % höhere Taktraten im Vergleich zu Intel 7 ermöglichen

- Intel 4 ist vom Grunde der Entwicklung her gesehen für die Nutzung von EMIB und FOVEROS vorgesehen

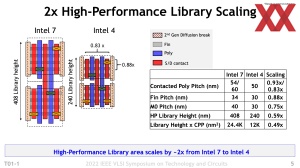

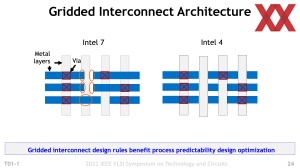

Zunächst einmal erläutert Intel, wie man die höhere Transistordichte erreicht. Natürlich gelingt dies durch kleinere Bauelemente und geringere Abstände zwischen diesen. Für eine HP-Bibliothek wird die Höhe dieser von 408 auf 240 nm reduziert. In der Breite schrumpft diese von 60 auf 50 nm (Poly Pitch). Die HP-Bibliothek in Intel 7 kommt demnach auf 24.480 nm², in Intel 4 sind es 12.000 nm². In der HP-Bibliothek selbst sind die Abstände ebenfalls reduziert worden. Der Fin Pitch wird von 34 auf 30 nm reduziert und der Metal Pitch für M0 von 40 auf 30 nm. Fin Pitch und Metal Pitch sind nun identisch, was in der Fertigung zahlreiche Vorteile haben soll.

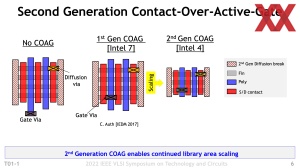

Mit Intel 7 führte Intel eine Technik namens Contact over active Gate (COAG) ein. Mit Intel 4 wird man eine zweite Generation einsetzen. Der Gate-Kontakt wird hier von außerhalb des aktiven Transistorbereichs in eben diesen versetzt (Darstellung des Gate Via im ersten Schaubild). Die zweite Generation von COAG skaliert mit Intel 4 in die geringeren Abstände in der HP-Bibliothek.

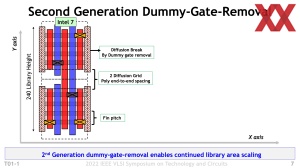

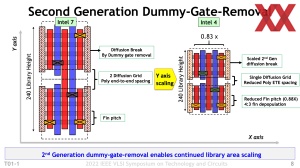

Da in einem Prozessor mehrere HP-Bibliotheken nahe zusammen sitzen, muss zwischen diesen eine Trennung erfolgen können. Entsprechend sind Diffusionsunterbrechnungen zwischen den HP-Bibliotheken und in der zweigeteilten HP-Bibliothek selbst, vorgesehen. Diese Diffusionsunterbrechnungen wird in Intel 7 mittels eines Dummy Gates realisiert. Mit Intel 4 setzt Intel diese Technik fort, kann in der Zelle als Trennung aber auf zwei dieser Diffusionsunterbrechnungen verzichten und setzt nur noch eine ein.

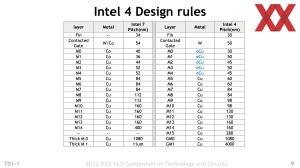

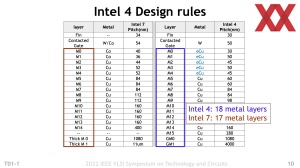

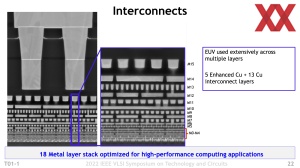

Ein Prozessor ist aus mehreren Schichten aufgebaut, die von den Kontakten, die nach außen in das Package geführt werden, bis hin zu den einzelnen Transistoren führten. Intel 7 setzt auf 17 Metallschichten, Intel 4 auf 18. In der Tabellen oben sind der Fin Pitch und der Contacted Gate Pitch aufgeführt. Als Füllmaterial (Contact Fill) kommt bei Intel 7 Wolfram-Kobalt zum Einsatz, für Intel 4 sieht Intel reines Wolfram vor.

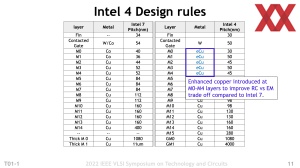

Die einzelnen Metallschichten sind als M0 bis M14, bzw. M15 beschrieben. Hinzu kommen noch die letzten Kontaktschichten. Für Intel 7 setzte Intel in den ersten fünf Schichten (M0 bis M4) auf Kobalt und Kupfer. Für Intel 4 wird hier auf Enhanced Copper gewechselt, dessen Charakteristiken sich besser eigenen sollen.

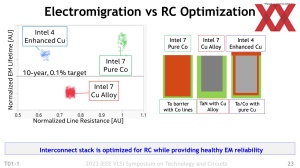

Bei der Materialwahl (Kupfer, Kupferlegierungen, Kobalt, etc.) muss Intel schon immer einen Kompromiss aus dem Leitungswiderstand und der Elektromigration eingehen. Reines Kobalt hat gute Eigenschaften für die Elektromigration, aber auch einen relativ hohen Leitungswiderstand. Die Kupferlegierungen können diesen reduzieren, dafür fällt die Elektromigration schlechter aus. Mit Enhanced Copper will will Intel das Beste aus beiden Welten zusammenführen.

Der Aufbau der Leiter sieht wie folgt aus:

Intel 7: Kupfer

- Leiterbahn aus Kupfer mit Außenschicht aus Tantal, welche die Elektromigration reduzieren soll

Intel 7: Kupferlegierung

- Leiterbahn aus Kupferlegierung und Außenschicht aus Tantalnitrat, welche die Elektromigration reduzieren soll

Intel 4: Enhanced Copper

- Außenschicht aus Tantal und Kobalt mit der Leiterbahn aus Kupfer

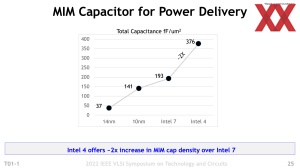

Intel 4 ist als Prozess auf die Herstellung von Chips im Bereich des High-Performance Computing ausgelegt. Entsprechend sind Spannungen von 0,65 bis 1,3 V vorgesehen. Im Vergleich zu Intel 7 will Intel um 20 % höhere Taktraten bei gleicher Leistungsaufnahme erreichen und liefert dazu die entsprechenden Metriken. Bei gleicher Frequenz kann die Leistungsaufnahme um 40 % reduziert werden.

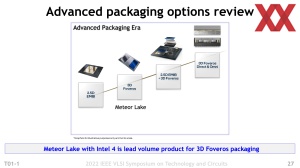

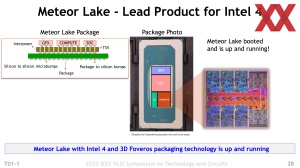

Das wichtigsten Produkt, für welches Intel die Fertigung in Intel 4 verwenden wird, ist Meteor Lake. Bisher ist noch nicht allzu viel über Meteor Lake bekannt. Meteor Lake besteht aus einem Compute-Tile mit den CPU-Kernen, einem I/O-Tile, einem SoC-Tile und einem GFX-Tile. Via 3D FOVEROS werden die einzelnen Chips gemeinsam auf einem Interposer betrieben. Im April bestätigte Intel, dass man Meteor Lake erfolgreich habe betreiben können.

In den Folien gibt es den Compute-Tile zu sehen, den Intel in Intel 4 fertigen will. Der GFX-Tile wird vermutlich von TSMC kommen, die SoC- und I/O-Tiles wird Intel wohl selbst fertigen, allerdings nicht in Intel 4, sondern einem größeren Fertigungsprozess, der dazu besser geeignet ist.

Der Die-Shot zeigt ein 6+8-Layout für Meteor Lake. Sprich, hier sind sechs Performance-Kerne und 2x 4 Efficiency-Kerne zu sehen. Dies dürfte eine der möglichen Ausbaustufen von Meteor Lake mit dem Tile-Design und verschiedenen Compute-Tiles sein.