Werbung

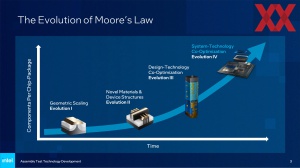

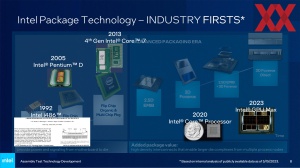

Bereits vielfach hatten wir darüber berichtet, dass nahezu alle Halbleiterhersteller einerseits die Entwicklung immer weiter optimierter Fertigungsgrößen mit immer feineren Strukturen vorantreiben und andererseits auch das Packaging zu einem immer wichtigeren Faktor wird. Die Chipentwicklung selbst bewegt sich immer an der Grenze des aktuell möglichen. Das Packaging eröffnet neue Möglichkeiten – sei es das Zusammenführen mehrere Compute-Chips oder die Einbindung neuer Speicher-Technologien und vieles mehr.

Intel hat ein Update seiner "Advanced Packaging"-Strategie verkündet, welches wir an dieser Stelle einmal zusammenfassen wollen. Teilweise hat man diese Pläne bereits vor Monaten und Jahren so in dieser Form angekündigt. Die erneute Bestätigung der weiterhin geplanten Ausführung ist in Zeiten zahlreicher Roadmap- und Produkt-Änderungen bei Intel ein gutes Zeichen. Zudem verrät Intel ein paar Details über nicht nur immer kleinere Strukturen, sondern auch die Nutzung komplett neuer Materialien wie dem Glas-Substrat, welches neue geometrische Formen im Chiplet-Design ermöglicht.

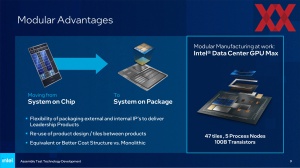

Intel setzt bereits heute in weiten Teilen seiner Produktlinie auf weiterentwickelte Packaging-Technologien. Die Xeon-Prozessoren der vierten Generation verwenden EMIB um vier Compute-Tiles und bei Xeon Max den HBM2e zusammen zu bringen. Die Data Center GPU Max "Ponte Vecchio" stellt mit ihren 47 Tiles aktuell die Speerspitze in Intels Packaging-Umsetzung dar. Währenddessen sind die Endkunden-Prozessoren und GPUs noch immer monolithische Designs, die natürlich ebenfalls hinsichtlich ihrer Fertigung und dem Packaging hochentwickelt sind, die aber noch nicht vollständig den Chiplet-Ansatz verfolgen, was vor allem auch mit den damit verbundenen Kosten zu begründen ist.

An dieser Stelle sei natürlich auch erwähnt, dass neben Intel auch Samsung, IBM und vor allem TSMC in den Packaging-Technologien die Zukunft sehen und hier viel Entwicklungsarbeit verrichten. Als Kunden nutzen dann AMD, NVIDIA und viele weitere die Expertise für ihre Chips. Zukünftig will auch Intel über sein IFS-Angebot externe Kunden gewinnen – entweder für die komplette Fertigungsstrecke vom Chip bis zum gesamtem Package oder aber auch nur für das Packaging. Dazu aber später noch etwas mehr.

Der aktuelle Stand bei Intel

Aktuell sieht Intels Packaging-Angebot für die eigenen Produkte wie folgt aus:

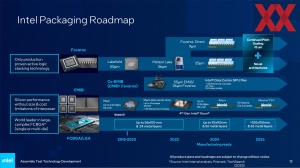

EMIB (Embedded Multi-die Interconnect Bridge) mit einem Bump-Abstand von 55 µm kommt in der vierten Xeon-Generation alias Sapphire Rapids zum Einsatz. Verwendet wird EMIB hier um vier Compute-Tiles und optional auch vier HBM2e-Speicherchips miteinander zu verbinden. Foveros wird für Meteor Lake eingesetzt werden und kommt hier auf einen Bump-Abstand von 36 µm. Auf einem Base-Tiles werden gleich mehrere Tiles zusammengebracht, die dann ein gemeinsames Package bilden. EMIB mit 55 µm und Fovers mit 36 µm sind gemeinsam für die Data Center GPU Max alias Ponte Vecchio im Einsatz. Allesamt sind diese Technologien in diesem Jahr im Einsatz.

Auch wenn die Zukunft im 2.5D- und 3D-Packaging liegt, so will Intel seine 2D- und MCP-Technologien (Multi Chip Packaging) weiterentwickeln, weil auch diese weiterhin gefragt sein werden. Aktuell erreicht man für ein FCBGA und FCLGA Bumb-Abstände von etwa 100 µm und kann Chips mit 92 x 92 und 100 x 100 mm an Fläche verarbeiten. Zukünftig will man über diese 100 x 100 mm hinausgehen können und auch der Bump-Abstand soll unter 90 µm vorangetrieben werden.

Bei EMIB hat man in der Vergangenheit bereits über nun erneut geäußerte Weiterentwicklungen gesprochen, führt diese aber nun noch einmal genauer aus. So sind geringere Bump-Abstände von 45 und 36 µm geplant, die dann auch mit TSVs (Through-Silicon Via) ausgestattet sein können. Die TSVs können zur Versorgung des darüberliegenden Chips verwendet werden und auch die Unterstützung von HBM ist über die TSVs gewährleistet. Per EMIB verbunden werden können aktuell Chip-Äquivalente mit einer Gesamtgröße von 4,5x Reticle. Ein Reticle beschreibt die maximale Größe eines Musters, das auf einem Wafer dargestellt werden kann – im die maximale Größe eines monolithischen Chips. Aktuell liegt das Maximum bei etwa 26 x 33 mm oder 858 mm². Mit dem Einsatz von High-NA EUV wird die Größe auf etwa 26 x 16,5 mm oder 429 mm² zusammenschrumpfen, was mit der amorphe Linsenanordnung zusammenhängt, die hier zum Einsatz kommt.

Die Weiterentwicklung von EMIB soll es aber ermöglichen, Chip-Äquivalente zu fertigen, die sechsfach so groß sind, wie das Reticle-Limit. Ob damit das aktuelle EUV-Limit von 850 mm² oder das neue von 430 mm² gemeint ist, ist nicht bekannt.

Für Foveros sieht Intel eine Weiterentwicklung von 36 µm (wie bei Meteor Lake eingesetzt) zu 25 µm. Foveros Direct ist eine Technik zur Verbindung mehrere Chips nicht mehr über die µBumps, sondern eine Kupfer-zu-Kupfer-Verbindung, wie sie TSMC bereits für Apples M1 Ultra anbietet oder wie sie auch für den zusätzlichen SRAM auf den Ryzen- und EPYC-Prozessoren mit 3D V-Cache zum Einsatz kommt. Foveros Direkt steigt dabei mit einem Bump-Abstand von 10 µm ein, dieser soll aber schnell auf bis zu 5 µm verringert werden.

Glas-Substrate sind robuster und flexibler

Noch bis 2012/13 setzte man beim Chip-Packaging auf keramische Trägermaterialien. Darauf folgten die heute noch verwendeten organischen Trägermaterialien, die bis heute für die Multi-Chip-Designs zum Einsatz kommen. Der nächste Schritt sollen nun Glas-Substrate sein.

Glas-Substrate zeichnen sich besonders durch einen geringeren Ausdehnungskoeffizienten aus und sind ingesamt stabiler als die organischen Substrate. Damit ermöglichen sie neue geometrische Formen im Aufbau eines Multi-Chip-Package. Die Stabilität bezieht sich auf die Fertigung, denn ein organisches Substrat kann sich durch die Erwärmung beim Aufbringen der Chips zum Beispiel verformen, was bei der gewünschten Präzision natürlich hinderlich ist.

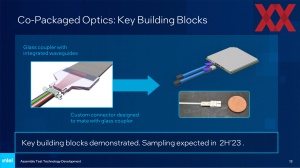

Durch die Nutzung von Glas-Substraten können aber auch neue I/O-Funktionen in die Packages eingebunden werden. Diese ermöglichen dann optische Verbindungen mit bis zu 448G. Glas-Substrate sind ab 2025 zu erwarten und aktuell wird noch evaluiert, ab welchem Punkt ihr Einsatz wirtschaftlich Sinn macht.

An Silicon Photonics arbeitet Intel bereits seit Jahrzehnten. Auch andere Hersteller forschen hier kräftig. Optische I/O-Tiles stehen aber offenbar inzwischen bereits – zumindest für eine der zukünftigen Chip-Generationen. Bis wir Glas-Substrate im Einsatz sehen werden, wird es noch einige Zeit dauern. Intel spricht von der zweiten Hälfte dieses Jahrzehnts.

Test-Expertise ist Intels Aushängeschild

Häufig ist bei der Fertigung der Chips die Rede von der Ausbeute. Bei unserem Besuch der Fab 28 in Israel konnten wir einen Eindruck gewinnen, welchen Aufwand Intel betreibt, damit die Ausbeute möglichst hoch ist. "Every Die wants to live" ist das Motto der Fab 28 in Israel und diesem hat man sich bei Intel weltweit verschrieben.

Schaut man sich nun ein Package wie das von Ponte Vecchio mit 47 aktiven Chips aus fünf verschiedenen Fertigungs-Techniken an, dürfte die Wichtigkeit einer guten Ausbeute offensichtlich werden. Ist auch nur einer der verwendeten Chips defekt, kann das gesamte Package nicht mehr verwendet werden. Also müssen alle Chips vorher zu 99,999 % auf ihre Funktionstüchtigkeit hin getestet werden und darin sieht Intel seine Stärken, weil man in diesem Segment schon jahrzehntelange Erfahrungen gemacht hat.

Es sind Einzeltest für Dies und Subsets von Dies möglich. Bei Ponte Vecchio wird in mehreren Schritten getestet, wenn die einzelnen Chips nacheinander zusammengebracht werden. Das Aufbringen der Chips auf die organischen Substrate ist ebenfalls nicht trivial und setzt eine große Kontrolle in den verwendeten Techniken voraus, damit die vielen tausende Kontaktpunkte zwischen dem Chip und dem Substrat auch funktionieren – nur um ein Beispiel zu nennen.

Packaging in Intels Foundry Services

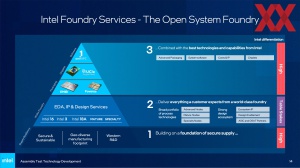

Neben der Weiterentwicklung seiner eigenen Chips sieht Intel die Zukunft in den Intel Foundry Services. Chip-Entwickler sollen sich an Intel wenden, wenn es um die Fertigung der Chips, das Testing oder das Packaging geht. All das sollen Services werden, die von Intel angeboten werden.

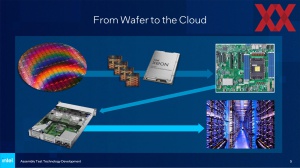

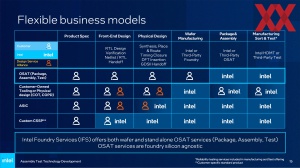

In der Wafer Foundry angeboten werden sollen zunächst Intel 16, Intel 3 und Intel 18A – über EDA (Electronic Design Automation), Intels IP und die dazugehörigen Design Services hinweg. An Packaging-Technologien angeboten werden sollen sowohl EMIB als auch Foveros. Das Angebot seitens Intel soll nahezu allumfassend sein. So kann ein Kunde zu Intel kommen, hat eine Produktspezifikation vorliegen und beauftrage Intel mit dem Front-End-Design, der Fertigung des Wafer, dem Packaging und dem Testing, bis hinten ein finalen Produkt herauskommt. Der Kunde kann seine Chips aber auch bei TSMC fertigen und bei Intel in einem Packaging mit EMIB oder Foveros zusammenbringen lassen. Auch nur das Testing ist möglich.

Die OSAT-Services sind Foundry-agnostisch. Packaging, Assembly und Testing finden hier bei Intel statt. Die Wafer können von jedem anderen Auftragsfertiger stammen – seien es TSMC oder Samsung. Intel nutzt dieses Prinzip bereits für Ponte Vecchio und wird es auch für Meteor Lake zum Einsatz bringen, wo einige der Chiplets nicht bei Intel gefertigt werden, sondern von TSMC stammen und dann bei Intel zu einem Package zusammengesetzt werden.

In den kommenden Jahren wird Intel seine Packaging-Techniken also immer weiter vorantreiben und dies wird parallel mit der Weiterentwicklung der Fertigung laufen, die zumindest bis Intel 18A schon konkret vorliegt. Aus der Erfahrung der Vergangenheit muss Intel nun beweisen, dass man diese Pläne auch umsetzen kann. Während es beim Packaging hier weniger Probleme gab, ist man für die Fertigung gerade dabei den Zug wieder auf die Schienen zu stellen. Intel 7, Intel 4, Intel 3, Intel 20A und Intel 18A sollen im Jahresrythmus umgesetzt werden. Bisher scheint man im Zeitplan zu sein.

Letztendlich werden Erfolgsmeldungen aus den Bereichen der Fertigung und des Packaging auch dazu führen, dass Kunden auf die IFS aufmerksam werden und diese auch nutzen. Intel möchte der größte Auftragsfertiger werden. Aktuell sitzt TSMC mit weitem Abstand in Führungsposition und auch dort wird die Entwicklung sicherlich nicht stillstehen.