Werbung

Auf seinem Datacenter-Event "Data Center and AI Technology Premiere" hat AMD heute eine Reihe Neuerungen bzw. weitere Details bekanntgegeben. Zu Beginn der Veranstaltung berichtete AMD aber zunächst über die Erfolge der aktuellen Genoa-Generation, die als General-Purpose-Prozessoren auch bei AWS zum Einsatz kommen.

Aber nun zu den Neuigkeiten. Final vorgestellt wurden die EPYC-Prozessoren auf Basis des Bergamo-Designs. Dabei handelt es sich um die SP5-kompatiblen Serverprozessoren mit angepassten Zen-4c-Kernen. Welche Anpassungen AMD hier gegenüber Genoa (Zen 4) gemacht hat, haben wir bereits in der vergangenen Woche beschrieben. Folgende Maßnahmen hat AMD vorgenommen:

- Halbierung des L3-Caches für einen Core Complexes (CCX) von 32 auf 16 MB

- pro CCD sind nun zwei CCX mit jeweils acht Kernen vorhanden

- auf Durchkontaktierungen (TSVs) für den 3D V-Cache wird verzichtet

- taktoptimiertes Design macht weniger Transistoren notwendig

- neue 6T-SRAM-Zellen

Durch diese Maßnahmen schrumpft AMD den Bereich, den ein Kern belegt, um 35 % zusammen. Ein Zen-4c-Kern kommt auf 2,48 mm², während es bei Zen 4 core 3,84 mm² sind.

Neben der Anzahl der Kerne pro Sockel, die nun bei 128 liegt, sind die einzelnen Kerne und der gesamte Prozessor auch effizienter. Anwendungen, die vom höheren Takt der Genoa-Prozessoren oder von einem größeren Cache profitieren, sind nicht die Zielgruppe für Bergamo. Hier kommt dann ich Genoa-X mit 3D V-Cache ins Spiel, aber dazu gleich mehr.

Drei Bergamo-Modelle wird es zunächst geben:

| Modell | Kerne / Threads | Basis / Boost-Takt | L3-Cache | TDP |

| EPYC 9754 | 128 / 256 | 2,25 / 3,1 GHz | 256 MB | 360 W |

| EPYC 9754S | 128 / 128 | 2,25 / 3,1 GHz | 256 MB | 360 W |

| EPYC 9734 | 112 / 224 | 2,2 / 3,0 GHz | 256 MB | 360 W |

128 und 112 Kerne haben die Bergamo-Modelle zu bieten. Beim EPYC 9754S ist das SMT abgeschaltet, was je nach Anwendung sinnvoll sein kann.

Gegenspieler der Bergamo-Prozessoren werden die Sierra-Forrest E-Core-Xeons sein, die Intel im kommenden Jahr auf den Markt bringen wird.

Genoa-X mit 3D V-Cache

Wie erwartet, wurden auch die Genoa-Prozessoren nun mit 3D V-Cache kombiniert und kommen als Genoa-X auf den Markt. Vier Modelle wird es geben, die von 16 bis 96 Kerne reichen. Bei 12 CCDs mit jeweils 96 MB an L3-Cache kommt ein solcher Prozessor auf 1.152 MB an L3-Cache – mehr als ein Gigabyte.

Die Genoa-X-Prozessoren können ihre Vorteile vor allem dort ausspielen, wo Daten im großen Cache landen und somit schneller zur Verfügung stehen. Neben EDA-Werkzeugen sind dies auch Simulationen und viele Anwendungen im HPC-Bereich.

| Modell | Kerne | Basis / Boost-Takt | L3-Cache | TDP |

| EPYC 9684X | 96 | 2,25 / 3,7 GHz | 1.152 MB | 400 W |

| EPYC 9384X | 32 | 3,1 / 3,9 GHz | 768 MB | 320 W |

| EPYC 9184X | 16 | 3,55 / 4,2 GHz | 768 MB | 320 W |

Die ersten Cloud-Instanzen mit Genoa-X sind von Microsoft im Rahmen des Azura-Angebots ab sofort verfügbar (HBv4 und HX VMs).

CPUs werden von Netzwerk-Aufgaben befreit

Alle großen Player am Markt haben erkannt, dass die Rechenleistung eines Rechenzentrums längst nicht mehr nur von den Prozessoren und Beschleunigern kommt. Das Netzwerk spielt zunehmend eine wichtigere Rolle. NVIDIA kaufte das israelische Unternehmen Mellanox. AMD kaufte vor einiger Zeit den Netzwerk-Spezialisten Pensando.

DPUs, IPUs oder wie auch immer die Hersteller ihre intelligenten Netzwerk-Beschleuniger nennen, sind bereits in vielen Bereichen im Einsatz. AMD stellt heute die D4 DPU vor. Zusammen mit intelligenten NICs und Switches will AMD so etwa 30 % an Rechenleistung von den CPUs nehmen, die ansonsten das Management des Netzwerk übernehmen müssten.

150 Milliarden US-Dollar Potenzial in AI

Natürlich will AMD auch vom aktuellen AI-Trend profitieren und tut dies bereits, denn einige der Supercomputer mit AMD-Hardware werden bereits dazu verwendet, um LLMs zu trainieren. Bisher sieht NVIDIA wie der größte Gewinner in diesem Bereich aus. AMD schätzt den Markt auf ein Volumen von 150 Milliarden US-Dollar und davon will man natürlich auch ein möglichst großes Kuchenstück abhaben.

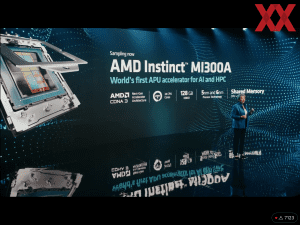

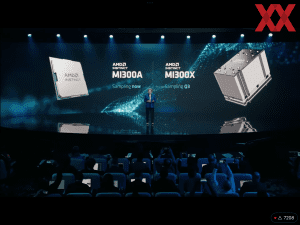

Bereits zur CES erstmals präsentiert wurde der Instinct MI300A. Dabei handelt es sich um den ersten APU-Beschleuniger von AMD, der 24 Zen-4-Kerne mit Compute-Chiplets mit CDNA-3-Architektur kombiniert. Gefertigt werden die Chiplets in 5 und 6 nm. Insgesamt kommen 13 Chiplets zum Einsatz: 3x Zen 4 und 10x CDNA 3. Den CPU-Kernen und den CDNA-3-Recheneinheiten stehen 128 GB an HBM3 zur Seite. Die Gesamtkomplexität des Chips beläuft sich auf 146 Milliarden Transistoren. Zum Vergleich: Eine H100-GPU von NVIDIA kommt auf 80 Milliarden Transistoren. Intels Ponte Vecchio soll auf über 100 Milliarden kommen.

Ein weiteres Instinct-Modell ist die MI300X. Dabei handelt es sich um eine Version, bei der die drei Zen-4-Chiplets entfernt und mit zwei CDNA-3-Chiplets ersetzt werden. Das Package besteht also aus 12 Chiplets und kommt auf 153 Milliarden Transistoren. Die Ausstattung an HBM3 steigt auf 192 GB. Die Speicherbandbreite liegt bei 5,2 TB/s. Auch hier wieder ein Vergleich zu NVIDIA: Der H100-Beschleuniger bietet 80 GB an HBM3, die mit 3,35 TB/s an gebunden sind.

AMD hat mit dem Sampling des Instinct MI300A bereits begonnen. Der MI300X soll im dritten Quartal in die Sampling-Phase übergehen. Im vierten Quartal sollen beide dann verfügbar sein.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen