Werbung

Bereits mit dem ersten Tag des diesjährigen IEEE International Electron Devices Meeting (IEDM 2023) haben wir über die Bemühungen von Intel und TSMC hinsichtlich der Materialforschung gesprochen, um Strukturbreiten von 2 nm und weniger in der Fertigung zu erreichen. Fokus der diesjährigen Konferenz ist aber sicherlich das Thema Backside Power Delivery Networks (BSPDN) – auch dazu hatten wir einen ausführlichen Bericht.

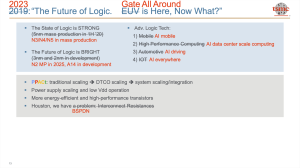

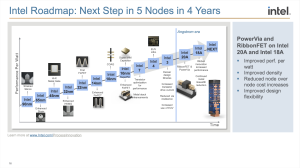

In einem sogenannten Evening Panel, bei dem auch Vertreter von Applied Materials, NVIDIA, TSMC, Synopsis und IBM vertreten waren, sprach der taiwanische Auftragsfertiger TSMC auch erstmals über das, was nach dem N2-Prozess kommen soll. Darauf gestoßen sind die Kollegen von ComputerBase. Mit dieser Veröffentlichung bekommt die Forschung in diesem Gebiet erstmals von TSMC einen Namen. Intel nennt seine Prozess der Angtrom-Era entsprechend Intel 20A sowie Intel 18A.

Der N2-Prozess soll 2025 bei TSMC in die Massenproduktion gehen. Der A14-Prozess befindet sich aktuell in der Entwicklung.

Zwischen 2027 und 2030 plant TSMC die Einführung der Fertigung in A14 und A10. Dies wird aber sicherlich auch davon abhängen, wie gut die Entwicklung der Fertigungsprozesse voranschreitet.

Aktuell kommen monolithische Chips auf etwa 80 Milliarden Transistoren auf einer Fläche von 814 mm². Für die Fertigung in N2 geht TSMC von mehr als 100 Milliarden Transistoren pro Chip und mehr als 500 Milliarden Transistoren im Package aus. Bis 2030 sollen es laut TSMC dann mehr als 200 Milliarden Transistoren für einen einzelnen Chip sein. Im 3D-Packaging wird voraussichtlich die Marke von einer Billion Transistoren geknackt.