Werbung

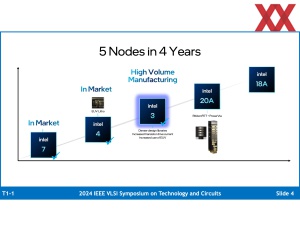

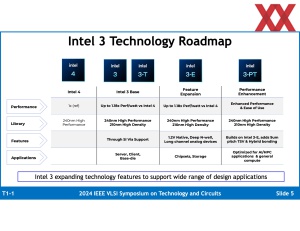

Im vergangenen Jahr veröffentlichte Intel zur Eröffnung der Fab 34 im irischen Leixlip einige Details zur Fertigung in Intel 4, die dort in der Folge stattgefunden hat. Auf dem VLSI Symposium sprach Intel nun über Intel 3, den nächsten Schritt in der eigenen Fertigung. Intel 3 kommt vor allem für die Xeon-6-Prozessoren zum Einsatz – sprich die reinen E-Kern-Modelle alias Sierra Forest und die klassischen P-Kern-Modelle Granite Rapids.

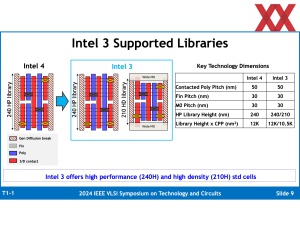

Für Intel ist der Prozess in Intel 3 ein wichtiger, auch wenn es "nur" die Xeon-Prozessoren sein werden, die darin gefertigt werden. Für Intel ist aber gerade dieser Umstand ein extrem entscheidender, denn die Serverprozessoren sind kein unwichtiges Produkt. Zudem strebte Intel mit Intel 3 sogenannten Full-Node-Verbesserungen an. Bei gleicher Leistungsaufnahme will man ein Leistungsplus von 18 % erreicht haben. Zudem bietet Intel 3 im Vergleich zu Intel 4 neue Standardzellen mit einer Höhe von 210 nm.

Aber Intel 3 nutzt auch die 240 nm hohen Zellen aus der Fertigung in Intel 4, zumindest für besonders effiziente Designs wie eben die E-Kern-Xeon-Prozessoren.

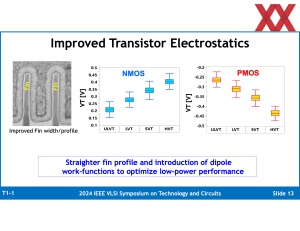

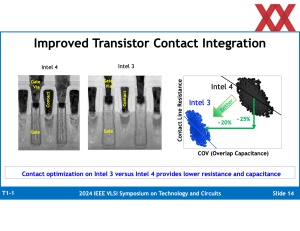

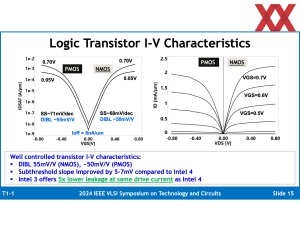

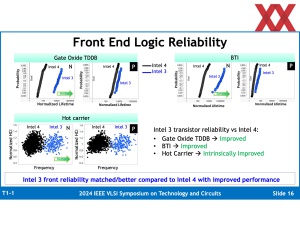

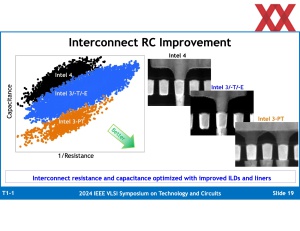

Die Verbesserungen werden durch verschiedene Maßnahmen erreicht: Verbesserte Kurzkanaleffekte (Short Channel Effects, SCE), eine Transistoransteuerung mit mehr Spannung bei einer vorgegebenen Leckage, eine geringere Kontaktkapazität, einen reduzierten RC-Wert der Interconnect-Verbindungen und zusätzliche Metallschichten für ein besseres Routing.

Für den Schritt von Intel 7 auf Intel 4 reduzierte Intel die Höhe einer High-Performance-Bibliothek von 408 auf 240 nm, nun sind es bis zu 210 nm. In der Breite (Poly Pitch) bleibt sie mit 50 nm unangetastet. Die HP-Bibliothek in Intel 7 kommt auf 24.480 nm², in Intel 4 sind es 12.000 nm² und nun in Intel 3 eben 10.500 nm².

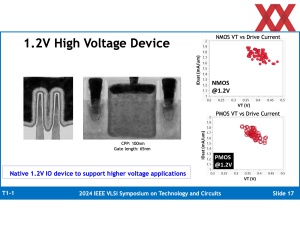

Für die I/O-Verbindungen hat Intel einige Verbesserungen eingebaut, die auch eine bessere Anbindung analoger Elemente ermöglicht.

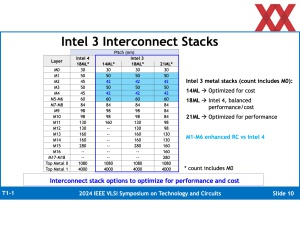

| Lage | Material in Intel 7 | Pitch in Intel 7 | Material in Intel 4 | Pitch in Intel 4 | Material in Intel 3 | Pitch in Intel 3 (12+2) | Pitch in Intel 3 (16+2) | Pitch in Intel 3 (19+2) |

| Kontakt-Gate | Wolfram/Kobalt | 54 nm | Wolfram | 50 nm | Wolfram | 50 nm | 50 nm | 50 nm |

| M0 | Kobalt | 40 nm | verb. Kupfer | 30 nm | verb. Kupfer | 30 nm | 30 nm | 30 nm |

| M1 | Kobalt | 36 nm | verb. Kupfer | 50 nm | verb. Kupfer | 50 nm | 50 nm | 50 nm |

| M2 | Kupfer | 44 nm | verb. Kupfer | 45 nm | verb. Kupfer | 42 nm | 42 nm | 42 nm |

| M3 | Kupfer | 52 nm | verb. Kupfer | 50 nm | verb. Kupfer | 50 nm | 50 nm | 50 nm |

| M4 | Kupfer | 52 nm | verb. Kupfer | 45 nm | verb. Kupfer | 42 nm | 42 nm | 42 nm |

| M5 | Kupfer | 84 nm | Kupfer | 60 nm | Kupfer | 60 nm | 60 nm | 60 nm |

| M6 | Kupfer | 84 nm | Kupfer | 60 nm | Kupfer | 60 nm | 60 nm | 60 nm |

| M7 | Kupfer | 84 nm | Kupfer | 84 nm | Kupfer | 84 nm | 84 nm | 84 nm |

| M8 | Kupfer | 112 nm | Kupfer | 84 nm | Kupfer | 84 nm | 84 nm | 84 nm |

| M9 | Kupfer | 112 nm | Kupfer | 98 nm | Kupfer | 98 nm | 98 nm | 84 nm |

| M10 | Kupfer | 160 nm | Kupfer | 98 nm | Kupfer | 98 nm | 98 nm | 84 nm |

| M11 | Kupfer | 160 nm | Kupfer | 130 nm | Kupfer | 160 nm | 130 nm | 98 nm |

| M12 | Kupfer | 160 nm | Kupfer | 130 nm | Kupfer | - | 130 nm | 98 nm |

| M13 | Kupfer | 160 nm | Kupfer | 160 nm | Kupfer | - | 160 nm | 130 nm |

| M14 | Kupfer | 400 nm | Kupfer | 160 nm | Kupfer | - | 160 nm | 130 nm |

| M15 | - | - | Kupfer | 280 nm | Kupfer | - | 280 nm | 160 nm |

| M16 | - | - | - | - | - | - | - | 160 nm |

| M17 | - | - | - | - | - | - | - | 280 nm |

| M18 | - | - | - | - | - | - | - | 280 nm |

| (G)M0 | Kupfer | 1.080 nm | Kupfer | 1.080 nm | Kupfer | 1.080 nm | 1.080 nm | 1.080 nm |

| (G)M1 | Kupfer | 11 µm | Kupfer | 4 µm | Kupfer | 4 µm | 4 µm | 4 µm |

In den Metalllagen kann Intel 3 genau wie Intel 4 auf ein 16+2-Design setzen oder aber auf zusätzliche drei Lage (19+2). Auch ein Design mit 14 Metalllagen gibt es, welches auf besonders niedrige Kosten ausgelegt ist. Die zusätzlichen Lagen des 19+2-Designs ermöglichen ein optimierteres Routing, sorgen im Fertigungsprozess aber auch für weitere Komplexität. In den ersten fünf Schichten (M0 bis M4) kommt weiterhin eine Kupferlegierung zum Einsatz, die Intel als "Enhanced Copper" bezeichnet. Für die 16+2-Designs in Intel 3 ändern sich in M2 und M4 die Abstände von 45 auf 42 nm. Darüber hinaus gibt es hier keinerlei Änderungen.

Anders sieht dies für die 19+2-Designs mit drei zusätzlichen Lagen aus. Hier sind M0 bis M10 zum 16+2-Design identisch, für M11 bis M15 verkleinert Intel die Abstände der Interconnects von 130 auf 98 nm, von 160 auf 130 nm und von 280 auf 160 nm. M16 bis M18 kommt dann die Abstände, die für Intel 4 bzw. Intel 3 im 16+2-Design für die Schichten M13 bis M15 vorgesehen waren. Keinerlei Änderungen gibt es bei den obersten Metalllagen.

Für alle Intel-3-Prozesse will Intel für den Einsatz von EUV-Schritten im Vergleich zu Intel 4 erhöht haben. Um welchen Prozentsatz der Einsatz von EUV steigt oder für welche Lagen Intel diese zum Einsatz kommt, erläutert man im Detail allerdings nicht.

+18% ISO-Power

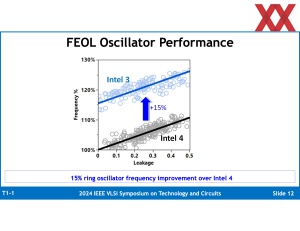

All die Veränderungen an den Layern und der HP-Bibliothek sollen natürlich für eine verbesserte Transistorleistung sorgen. Bei gleicher Leakage soll Intel 3 eine um 15 % höhere Frequenz möglich machen im Vergleich zu Intel 4.

Die Back-End-Verbindungen weisen eine Kapazitätsreduzierung von bis zu 8 % pro Schicht auf. Dies wird mittels EUV-Patterning und verbesserten Ultra-Low-K-Dielektrika ermöglicht. Die parasitären Kapazitäten der Verbindungen werden durch Verbesserungen bei der Metallfüllung mittels Barriere- und Liner-Optimierungen in den unteren Schichten (M0 bis M6) weiter reduziert.

Intel 3 bietet zudem eine gleiche oder bessere Vmin und ISO-Fläche für 0,024 μm² High-Density-Cell (HDC) und einer 0,030 μm² High-Current-Cell (HCC). Die untenstehenden Diagramme vergleichen Intel 4 und Intel 3 in dieser Hinsicht.

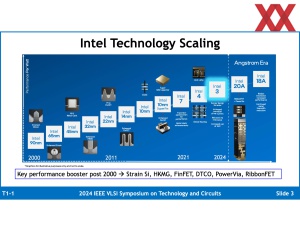

Es ist nur ein kurzer Überblick dessen, was Intel für Intel 3 an Änderungen gewählt hat. Intel 3 ist zudem der letzte Prozessschritt vor Intel 20A, wo dann auch ein Wechsel auf die RibbonFETs und PowerVia vollzogen wird. Letztendlich hat Intel durch Verbesserungen in den Bereichen Transistoren, Interconnects und dem Design erreicht, die zu +18% ISO-Power geführt haben. Bei gleicher Leistungsaufnahme wird ein Leistungsplus von 18 % erreicht.

Intel 3 ist aber auch flexibel genug um leistungsfähige und hochdichte Designs fertigen zu können. Auch die Einbindung von analogen und Mixed-Signal-IP-Designs ist möglich. Bei den nun neuen Xeon-6-Prozessoren verwendet Intel die Fertigung in Intel 3. Consumer-Chips wie Arrow Lake hingegen werden bereits auf Intel 20A setzen.