Werbung

Eigentlich schon für den aus Kostengründen eingesparten Entwicklungsschritt Intel 20A geplant, wird PowerVia als rückseitige Stromversorgung der Transistoren in den Chips für Intel ab Intel 18A zu einem wichtigen Thema werden. Auch TSMC wird die Technik zum Einsatz bringen, allerdings erst ab der A16-Fertigung und auch Samsung hat mit SF2Z entsprechende Pläne in der Roadmap.

Bei Intel als PowerVia bezeichnet, nennt TSMC die Technik Super Power Rail (SPR) – gemeint sind immer Backside Power Delivery Networks (BSPDN), aber im Detail in unterschiedlichen Ausführungen.

Durch die rückseitige Versorgung wird die Stromzufuhr zu den Transistoren als Konkurrenz um den Platz mit Signalleitungen beseitigt, wodurch niedrigere elektrische Widerstände erreicht werden. Dies führt zu effizienterer Stromversorgung und weniger Energieverlust. Da Signal- über das Frontside Power Delivery Network (FSPDN) und Stromleitungen über das Backside Power Delivery Networks (BSPDN) physisch getrennt sind, gibt es weniger elektromagnetische Interferenzen, was die Signalqualität und Taktraten verbessert. Geringere Verluste und wenige Störungen wirken sich positiv auf die Eigenschaften der Chips aus.

Da die Vorderseite des Chips nicht mehr für die Stromversorgung genutzt wird, steht mehr Raum für Signalleitungen und Transistoren zur Verfügung. Dies ermöglicht eine höhere Packungsdichte und Skalierung.

Aber nicht nur Vorteile

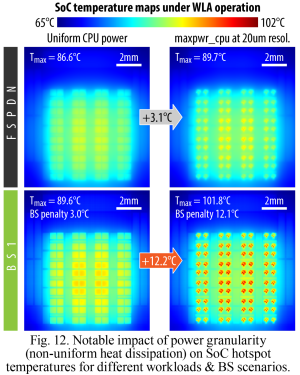

Die Umsetzung des BSPDN hat jedoch nicht nur Vorteile. Durch die Verlagerung der Stromversorgung auf die Rückseite werden thermische Hotspots potenziell besser verteilt, was die Wärmeableitung optimieren kann. Auf der IEDM-Konferenz präsentierte das imec (Interuniversity Microelectronics Centre) ein wissenschaftliches Papier, in dem von stärkeren thermischen Hotspots die Rede ist.

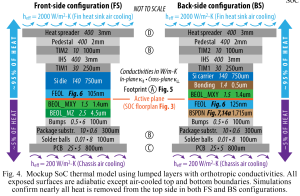

Ermittelt hat man dies über eine Simulation eines SoCs mit 80 Kernen sowie DDR-, PCIe- und I/O-Controllern. Verschiedene Workloads wurden simuliert, die von einer Gesamtleistungsaufnahme von etwa 57 bis 83 W ausgehen. Für den Schichtaufbau bestehend aus dem Back-End of Line (BEOL), dem Front-End of Line (FEOL), dem eigentlichen Chip sowie dem Bumps und Bonding-Schichten ist das imec von üblichen Stärken ausgegangen.

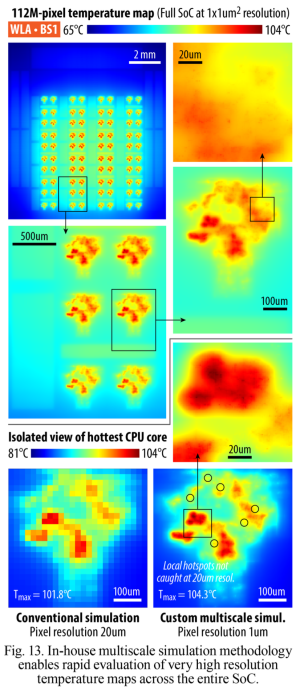

Das Ergebnis der Simulationen ist, dass BSPDN-basierte Designs um bis zu 14°C höhere Hotspot-Temperature als FSPDN-Designs erzeugen. Der Grund dafür sollen zusätzliche thermische Widerstände sein. Verursacht werden diese unter anderem durch Wafer-Bonding-Lagen, durch welche die Abwärme abgeführt werden muss. Diese höheren Hotspot-Temperaturen laufen natürlich entgegen den Ankündigungen zum BSPDN.

Das imec liefert allerdings auch Lösungen. So soll das Hinzufügen einer Masseebene unterhalb des BSPDN für eine bessere Wärmeabfuhr sorgen. Dünnere Wafer-Bonding-Lagen wirken sich ebenfalls positiv aus. Zudem zeigt Forschung an neuen Materialien wie Aluminium-Nitrid einen positiven Effekt. Zwischen 1 bis 6,5 °C niedrigere Hotspot-Temperaturen sind durch einzelne Maßnahmen möglich. Kombiniert man einige der Maßnahmen, sollen es im Durchschnitt 8,7 °C sein.

Das imec schlussfolgert, dass ein BSPDN bei hoher oder nicht-uniformer Leistungsdichte problematisch sein kann. Über fein granulare Leistungsanalysen ist es möglich, die potenziellen Hotspots zu simulieren und diesen entgegenzuwirken. An entsprechenden Lösungen dürften die Chiphersteller wie Intel, Samsung und TSMC bereits arbeiten, bzw. gearbeitet haben. Dass ein BSPDN neben der höheren Komplexität in der Fertigung weitere Nachteile hat, ist sicherlich ein interessanter Aspekt.