Werbung

Auf der CES stellten AMD die Ryzen-AI-Max-Prozessoren mit bis zu 16 Zen-5-Kernen und einer starken integrierten GPU vor, zu denen es nun weitere Informationen gibt. Die Kollegen von Chips and Cheese führten ein Interview mit Mahesh Subramony, einem Senior Fellow von AMD, der als SoC-Architektur an der Entwicklung von Strix Halo beteiligt war.

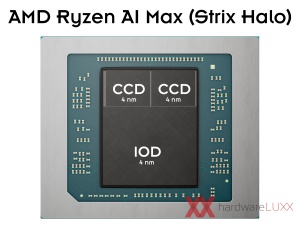

Der Aufbau von Strix Halo ist dem der Desktop-Modelle ganz ähnlich: Es gibt zwei CCDs mit jeweils bis zu acht Zen-5-Kernen und einen IOD, der die I/O-Funktionen und vor allem die integrierte Grafikeinheit enthält. AMD lässt die CCDs bei TSMC in N4, also nominell 4 nm, im Grunde aber einem optimierten 5-nm-Prozess, fertigen. Während die IODs bei den Ryzen-Prozessoren aber weiterhin in 6 nm (N6) gefertigt werden, kommt für die Ryzen-AI-Max-Prozessoren ebenfalls eine Fertigung in 4 nm zum Einsatz. Dies wäre damit trotz aller Ähnlichkeiten schon der erste Unterschied.

Die Zen-5-Kerne in den CCDs sind mit den Zen-5-Kernen der Desktop-Modelle identisch – inklusive der vollen Fließkommaeinheiten mit einer Breite von 512 Bit.

Neben der Fertigung des IOD gibt es einen weiteren Unterschied in der Anbindung der beiden CCDs mit dem IOD. Die CCDs haben ein physikalisches Interface für die Anbindung mit den weiteren Chiplets. Bei Granite Ridge (Ryzen-9000-Serie) setzt AMD auf einen SERDES (Serializer/Deserializer), der parallele Daten in serielle Daten umwandelt (Serialization) und am Zielort wieder zurück in parallele Daten (Deserialization). Das Ziel ist, die Anzahl der Verbindungen zwischen Sender und Empfänger zu reduzieren.

Eine solche Verbindung ermöglicht eine effiziente Übertragung über längere Distanzen, da serielle Signale weniger störanfällig und einfacher zu übertragen sind. Durch die serielle Übertragung können zudem höhere Datenraten pro Leitung erreicht werden. Weniger Verbindungen bedeuten aber auch weniger Platzbedarf.

Eine Anbindung mittels SERDES ermöglicht es, die Verbindung zwischen den Chips in verschiedene Leistungsmodi zu versetzen. Auf der anderen Seite bedeutet ein Wechsel in einen anderen Powermodus auch immer, dass ein Retraining der Verbindungen notwendig ist, was einen negativen Einfluss auf die Latenzen hat.

Ein Sea of Wires

Für Strix Halo setzt AMD aber auf einen Sea of Wires. Eine "Sea of Wires"-Anbindung bedeutet, dass Daten parallel über eine Vielzahl von Leitungen übertragen werden. Jede parallele Leitung repräsentiert typischerweise einen Bit- oder einen Datenkanal.

Im Unterschied zur Verwendung eines SERDES fallen die Latenzen in der Datenübertragung geringer aus, da die Daten gleichzeitig über parallele Leitungen übertragen werden. Es gibt keinerlei Verzögerungen durch die Serialisierung/Deserialisierung. Zudem bietet sich eine "Sea of Wires"-Anbindung bei derart engen Abständen zwischen den Chips an.

Allerdings nehmen die vielen parallelen Leitungen mehr Fläche auf der Leiterplatte des Packages ein. Zudem sind für die eine "Sea of Wires"-Anbindung mehr Pins für die Außenanbindung notwendig, so dass wir aktuell davon ausgehen, dass AMD kleinere Änderungen an den CCDs hat vornehmen müssen, bzw. es sich nicht um die identischen Chips handelt.

AMD hat sich für eine "Sea of Wires"-Anbindung entschieden, da darüber eine Anbindung mit niedriger Leistungsaufnahme möglich ist, die aber ebenfalls 32 Bytes pro Taktzyklus übertragen kann. Die Fertigung des Substrats ist wegen der Vielzahl an Verbindungen zwischen den Chips etwas aufwändiger und damit teurer. Für AMD war es aber wichtig Die Ryzen-AI-Max-Prozessoren in dieser Hinsicht zu optimieren und nicht einfach nur den leichtesten Weg zu gehen.

Nun dürfen wir gespannt sein, in welcher Form uns die ersten Systeme mit den Ryzen-AI-Max-Prozessoren erwarten und welchen Eindruck sie hinterlassen können.