Werbung

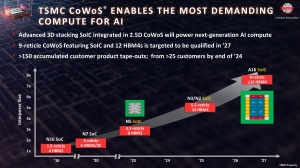

Auf dem Open Innovation Platform (OIP) Forum sprach TSMC über seine zukünftigen Pläne hinsichtlich des Packaging, genauer dem Chip-on-Wafer-on-Substrate (CoWoS) und definierte dabei die bisherigen Ziele zur Größe des verwendeten Interposer etwas genauer. Aktuell wird das CoWoS-Packaging im Bereich des dreifachen, des sogenannten Reticle-Limits limitiert, also der maximalen Größe, in der ein monolithischer Chips gefertigt werden kann.

In der aktuellen Fertigung mit EUV-Lithografie liegt dieses Limit bei 858 mm² und wird beispielsweise von NVIDIAs Blackwell-GPU fast ausgereizt. Zwei Blackwell-GPUs nebst acht HBM3E-Speicherchips finden auf einem von TSMC hergestellten Package ihren Platz. N5 SoIC (System-on-Integrated Chips) auf einem CoWoS-Package mit 3,3x Reticle-Limit sind das aktuelle Maximum für TSMC.

Für das kommende Jahr plant TSMC laut TomsHardware mit N3/N2 SoIC in einem Package mit einem Reticle-Limit mit Faktor 5,5. Die Compute-Chips dürften dabei nicht größer als aktuelle sein, was technisch auch nicht möglich ist (siehe das Reticle-Limit), dafür aber sollen sich bis zu 12 HBM4-Chips auf dem Package befinden.

Ab 2027 geht TSMC dann davon aus, dass die CoWoS-Technologie sich soweit weiterentwickelt hat, dass man das Package mit einem Reticle-Limit mit Faktor 9 herstellen kann und darauf auch eventuell mehr als zwölf HBM4-Chips unterbringt. Wie viele Compute-Chips darauf ihren Platz finden, hängt auch davon ab, was die Auftraggeber der Chips bis dahin an Design und Aufbau planen.

Die Compute-Chips sollen dann bereits in A16 gefertigt werden. Die große Frage wird sein, ob TSMC bis dahin auch die High-NA-EUV-Lithografie zum Einsatz bringen wird. Aktuell ist dies wohl erst mit A14 geplant. Neben der Größe des Substrats wird auch dem Interposer eine immer wichtigere Rolle zukommen. Auch daran wird aktuell kräftig geforscht – nicht nur bei TSMC (siehe Intels Forschung an Glassubstraten).

Immer größere Packages sind die eine Dimension in der Chipfertigung, die dritte ist die Höhe. Aktuell setzt TSMC für SoIC auf N6-on-N5, ab 2025 soll N3-on-N2 möglich sein und für 2027 geht man von A16-on-N2 aus. Das Packaging ist und bleibt damit eine technische Herausforderung und gleichzeitig Kernkomponente für die Steigerung der Rechenleistung.

High-NA EUV setzt neue Reticle-Limits

Aktuell orientiert sich das Reticle-Limit an den maximalen 858 mm² der EUV-Lithografie. Mit High-NA EUV wird sich durch die numerische Aperture die Fläche pro Belichtungsvorgang halbieren. Begründet ist dies durch den Aufbau der Belichtungs-Masken. Jede EUV-Maske besteht aus einem mehrschichtigen Stapel an Schichten (MoSI, Monosilizium-Multilayer) und diese verursachen Reflexionen. Über anamorphe Linsen bleibt man unter gewissen Limits für den Belichtungswinkel. Dies hat dann jedoch zur Folge, dass man für die typischen 6-Zoll-Masken keine Vollfeld-Belichtung (Full Field) mehr vornehmen kann, sondern auf halbe Felder (Half Field) gehen muss.

Das Rectile-Limit, also die maximale Größe der Chips, die gefertigt werden können, wird damit von den aktuellen 26 x 33 mm (858 mm²) auf 26 x 16,5 mm (429 mm²) halbiert. Soll ein Chip größer als diese 429 mm² sein, muss ein sogenanntes Stiching angewendet werden. Dabei werden die beiden Hälften des Chips getrennt voneinander belichtet und zusammengesetzt. Das Stiching kann aber fehleranfällig sein und reduziert die Ausbeute.

Weitere Informationen zur High-NA-EUV-Lithografie findet ihr in einem gesonderten Artikel.