Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.486

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Ah its only written on the ICs sadly.Is there anything i can post for you to check the Class of the dimms? I dont even know what is that

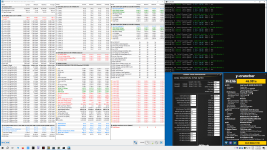

So 5 loops of VST/VT3 and full 25 loops of TM5?

This will take some time...so lets start!

Early we had RamMon by Passmark.

but they updated it and now it doesnt display correctly the JEDEC binning of the ICs.

Some bad ICs are JEDEC 4800 binned although follow A-Die 120ns RFC cap instead ~135-140ns M-Die.

The ICs Branding next to the manufacturing date 2xxA, 2xxV, 300A, 300V

A is Class A, V are the lower tier of cheaper to produce ICs. With slight disadvantage on primaries, RTP and RFC.

Well the biggest is their clock limit. Most cap near 7800 where afterwards they want a lot of voltage.

Real class-A can easily go higher without having to tighten down primaries soo much

In the current buying state, everything from 5600-7800 kits can be ClassV

Its difficult.

Else if your TeamGroups are - TG silk, vs SK Hynix branded ~ they are 3xx versions and pretty much ClassV.

Ellse they wouldnt have a reason to buy cheap and to also hide it.

I dont have any tight profile for A-Dies sadly

Except low clock.

Shouldnt be too badSo 5 loops of VST/VT3 and full 25 loops of TM5?

This will take some time...so lets start!

5 loops to verify our change doesnt break anything on cpu side

And then full TM5, yes ~ but that takes for you around 90min too. 1:30-1:50h

Might take near that 1:45-1:50 mark, as you run HT off.

Let me know if RTT, especially PARK side refuses to boot.

ASUS is known to reinvent the wheel, especially on RTTs + Board design , so lets see.

Same usually for G.Skill PCBs

Change should "just work".

RTTs for both channel are identical and not compatible with 24GB dimms.

Beitrag automatisch zusammengeführt:

I will try the insta crash test, just I am in a project right now.

still investigating ODT issues, of samples.

But i'm curious how much of it was user-error to begin with.

Happy ppl start to listen to me on PMIC side and VDDQ off side

Just taken, soon ~2? years.

Happy everyone starts to listen with limiters too.

Maybe slowly things change. But very slowly.

Zuletzt bearbeitet: