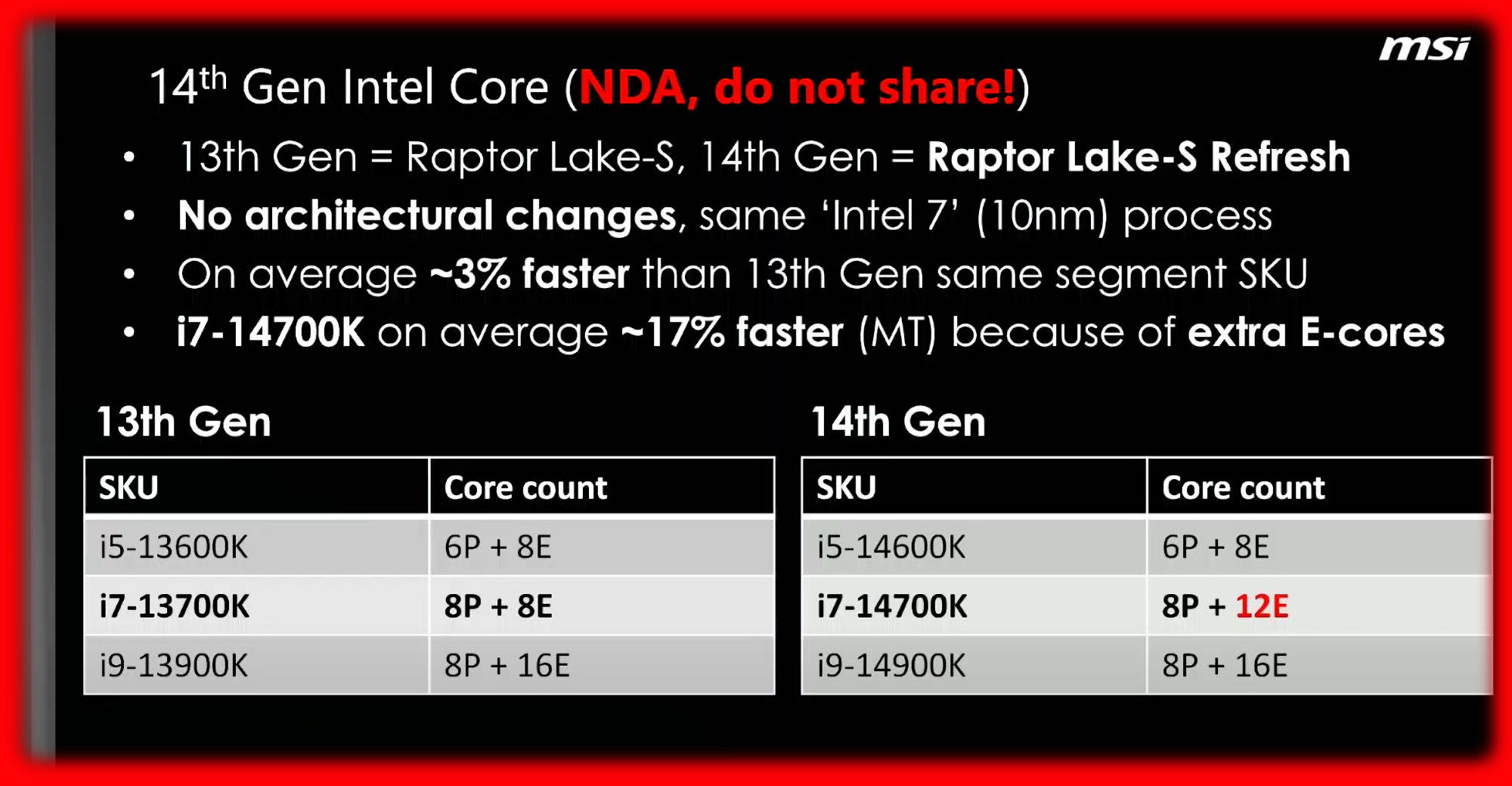

Es geht aber um Vollasteffizienz. Die E-Cores können deutlich effizienter arbeiten, so dass bei gleichem Stromverbrauch mehr parallele Rechenleistung zur Verfügung steht. Die P-Cores sind nur bei Single-Thread-Aufgaben besser, und für einige Workloads bei denen sich die Aufgaben nur schlecht parallelisieren lassen. Mit anderen Worten es lässt sich parallelisieren, aber nur mit wenigen Cores da sonst der Code eher langsamer läuft. Dann hat man Vorteile vom P-Cores Ansatz. Für alle anderen Workloads sind die E-Cores besser, da sie effizienter Leistung zur Verfügung stellen. Das ist salopp formuliert der Ansatz der Beschleuniger Karten von AMD oder nVidia, bei denen ebenfalls mit recht simplen Einheiten und dafür sehr vielen die hohe Rechenleistung erzielt wird. AMD hat bei den neuen Zen 4c allerdings geschafft relativ komplexe Cores in Massen in die CPU (EPYC aktuell bis zu 128 Cores) zu verbauen. Man wird sehen, ob die Zen 4c Cores auch in die Desktop Plattform von AMD Einzug hält.

Und was ist dann der Unterschied zu HT und SMT? (Mir das schon klar, wie das geht, mehr Alus und so, wirkt sich nicht so toll aus usw...)

Also ich versteh schon.

Aber wenn ich mich an den Task Manager aus 2003 mit dem Northwood erinnere, waren das auch schon 2 "Kerne".

Provokante, bissl scherzhafte Frage:

Verkauft intel nen P Core als 2 E Cores?

Ich mein vom Windows aus kann ich den Unterschied nicht erkennen, in die DIE schauen kann

ich nicht.

... jetzt fliegen gleich die Steine nach mir

...

Aber hey, so abwegig ist das nicht.

Wo P-Cores gefragt ist (Singlethread) ist das Intel Zeug ganz gut (auch der I5), beim Rest so najaaa... pro Watt dann eher meh.

Für mich sieht dieses E-Core Zeug eher nach so nem Alibi für "Guck mal, wir haben auch ganz viele Cores!!111einself" aus, weil 5900x, 5950x und Nachfolger halt schon unbequem sind.

Macht sich gut, wenn man 20 Core und 24 Core aufn RGB Kacknoob PC im Kaufhaus schreiben kann.

AMD kann dann Bulldozerlike zurückschießen und den 16 core mit SMT als 32 e-core ohne SMT verticken, lol, sind eben E cores, die sind aus Effizienzgründen in 1 Core zusammengefasst, blablub, irgend ein pseudotechnischer Marketingbullshit lässt sich schon herbeischwurbeln, wo dann Leute wie der Holzi ganz hart werden davon.

Roast me...

edit:

... und wäre an dem E-Core Zeug viel mehr dran als Snakeoil, würde es doch tiefer in die Architektur greifen, den Scheduler... wenn das doch so eine große Sache wäre, das doch nicht so unauffällig zwischendurch in der Modellpflege zu implementieren... oder doch?

Ich mein nur... bei so großen Dingen hat man ja doch gern die Namen der Produkte gewechselt, von Pentium auf Core, auf Core-i, ihr wisst schon.

In der Praxis sehe ich halt die Bedeutungslosigkeit der E-Cores... den Sinn kann man sich ja einreden, theoretisch ist das ja auch super praktisch, in der Praxis, hm...