Werbung

Ein Prozessor muss aber nicht nur aus einem dieser Module bestehen, sondern es können bis zu vier Bulldozer-Module zusammengesetzt werden. Im Resultat ergeben sich Prozessoren mit zwei bis acht der neuen Kerne. Jeder dieser Kerne wird dem OS als logischer Prozessor angezeigt, ähnlich wie es auch bei Intels HyperThreading-Technologie der Fall ist. Eine CPU, die aus vier Bulldozer-Modulen besteht, wird also als ein 8-Kern-Prozessor im Windows Task Manager auftauchen. AMD will mit dieser Idee einen guten Kompromiss zwischen einem Single-Core mit SMT (HyperThreading), der eben eigentlich ein Single-Core ist, und einem Dual-Core, der oftmals unnötig viele Ressourcen brachliegen lässt, gefunden haben. Mit der Einführung des AMD Phenom hatten viele bereits mit starken Änderungen in der Architektur gerechnet, doch AMD blieb dem K8-Design treu, und so konnte Intel in der Performance pro Takt immer weiter davon ziehen. Mit Bulldozer soll nun das Design erscheinen, auf das AMD-Nutzer schon etwas länger gewartet haben.

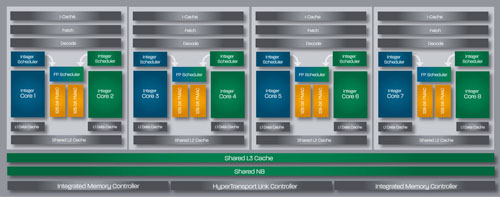

Der strukturelle Aufbau eines Bulldozer-8-Kern-Prozessors

Taucht man etwas tiefer in die Mikro-Architektur eines Bulldozer-Moduls ein, werden Gemeinsamkeiten mit Intels Westmere sichtbar. So ist das Modul wie beim Phenom zwar bei einem 64 kB L1-Cache des Instruction-Fetcher geblieben, dieser gibt Anweisungen aus zwei Threads aber an vier Decoder weiter und nicht mehr an nur drei. Aus dieser Decoder-Engine werden die Daten dann an drei unabhängige Scheduler weitergegeben: zwei Integer- und ein Shared-Floating-Point-Core. Jeder Integer-Core besitzt zwei AGU- und ALU-Engines. Während vielen ALU ein Begriff ist, sorgt AGU noch immer für Fragezeichen: AGU steht für "Adress Generation Unit". Dabei handelt es sich um eine Art Integer-Recheneinheit, welche sich um die Generierung von Speicheradressen sowie um das Lesen und Speichern kümmert. Dem Integer-Core stehen 16 kB L1-Cache zur Verfügung.

Neben den bereits bestehenden SIMD-Befehlssätzen und AES kennt Bulldozer nun auch die AVX-Instruktionen sowie XOP und FMA4. Allerdings ist die Unterstützung von FMA4 von Intel ungewiss, weshalb hier unklar ist, ob die Funktionen in der Masse eingesetzt werden.

Der Cache ist nach Threads aufgeteilt, sodass der Shared-Floating-Point-Core entscheiden kann, auf welchen Teil des Caches er zurückgreifen muss. Innerhalb des Shared-Floating-Point-Core befinden sich dann jeweils zwei 128 Bit FMAC- und 128 Bit Packed-Integer-Pipelines, die dafür sorgen, dass der Shared-Floating-Point-Core auf zwei Threads gleichzeitig arbeiten kann. Wie Intels kommende Sandy-Bridge-Prozessoren unterstützt AMDs Bulldozer-Modul SSE-Instructions-Sets bis zur Version 4.2 und ebenfalls Intels AVX-Instruktionen. 256-Bit-AVX-Operationen werden durch zwei 128-Bit-FMAC-Units ausgeführt. Jedes Bulldozer-Modul verfügt über seinen eigenen L2-Cache, den sich der Integer- und die zwei Shared-Floating-Point-Cores teilen.

Das komplette Die mit vier Bulldozer-Modulen besitzt eine Gesamtgröße von 315 mm² und insgesamt 2 Milliarden Transistoren:

Beim Kern sind zum einen die großen L2-Caches zu sehen (oberhalb

eines Bulldozer-Moduls), zum anderen auch die gemeinsamen L3-Caches,

die sich in der Mitte befinden.

Alle Bulldozer-Module können unabhängig voneinander getaktet und mit der nötigen Spannung versorgt werden. So kann ein Bulldozer-Modul nun auch komplett abgeschaltet werden und verbraucht im Idle-Modus nicht einmal mehr Strom. Die dann eingesparte Leistung kann in anderen Modulen zusätzlich verbraucht werden. Intel macht dies in seiner Turbo-Boost-Technologie nicht viel anders. Da Takt und möglicher maximaler Verbrauch aber auf Ebene des Modules bestimmt werden und nicht auf Core-Ebene, sind doch entscheidende Unterschiede zu Intel vorhanden – AMDs Lösung könnte deutlich effizienter arbeiten als die Core-Turbo-Technologie von Intel. Im Unterschied dazu kommunizieren die Module nun nicht nur mehr über ein Taktsignal, sondern auch bezüglich der anliegenden Spannung miteinander. Weitere Details dazu sind auf der nächsten Seite zu finden.

AMD setzt für Bulldozer den 32-nm-Prozess von Globalfoundries mit Silicon-on-Insulator-Technik ein.