Werbung

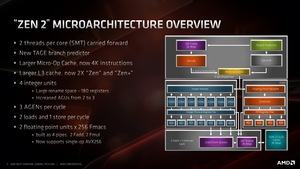

Intern heißt der Chip auf Basis der Zen-2-Architektur Valhalla. Ein Valhalla-Chip, auch als CCD (Core Complex Die) bezeichnet, besteht aus zwei Core Complexen (CCX) mit jeweils vier Kernen. Ein Valhalla-Chip kommt also auf maximal acht Kerne. Es bleibt weiterhin bei der Unterstützung von SMT, so dass zwei Threads pro Kern verarbeitet werden können.

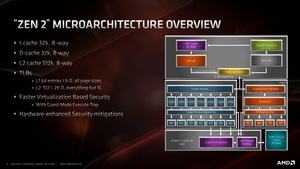

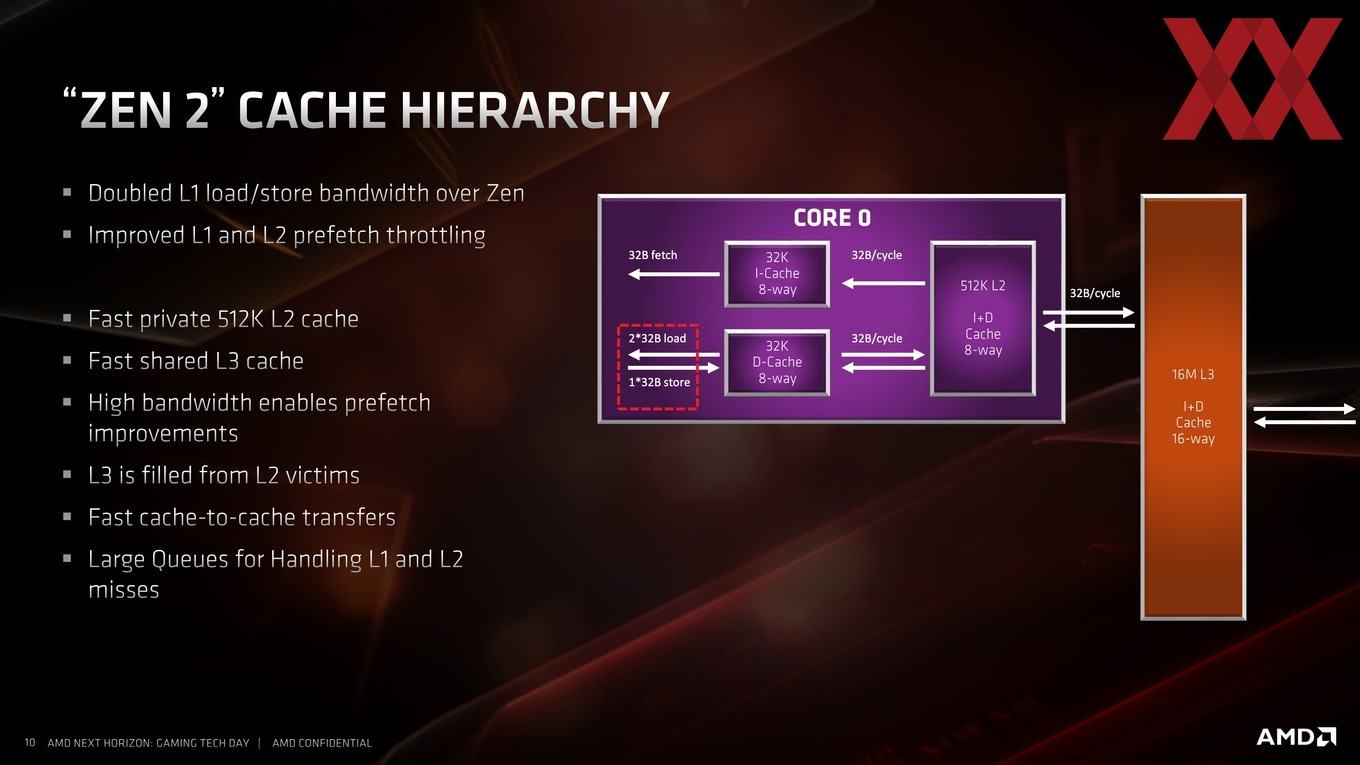

Jeder CCX hat einen 16 MB großen L3-Cache, der in vier Slices zu jeweils 4 MB aufgeteilt wird. Exklusiv zur Verfügung stehen jedem Kern 512 kB an L2-Cache. Der L1-Cache besteht aus 32 kB Instruction und 32 kB Data-Cache. Zudem hat AMD neue Cache-Instruktionen eingepflegt, die ebenfalls dazu beitragen sollen, dass Zugriffe im Cache schneller und effektiver abgearbeitet werden können.

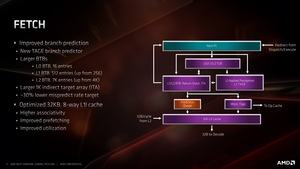

Einen Großteil der IPC-Verbesserungen fällt auf die Branch Prediction oder auf Deutsch Sprungvorhersage. Diese werden verwendet, um alle Stufen einer CPU-Pipeline möglichst immer und sinnvoll auszulasten. Dazu macht ein Prozessor aber Vorhersagen zu möglichen nächsten Schritten, die zutreffen können, aber nicht müssen. Entsprechend bestimmt die Qualität der Vorhersagen über die Effektivität. AMD verwendet mit Zen 2 nun eine TAGE Branch Prediction. TAGE beschreibt einen der möglichen Algorithmen, die in diesem Bereich eingesetzt werden können.

Eine TAGE Branch Prediction ist ein hybrider Ansatz des Verfahrens. Anstatt eines Pfades werden mehrere Pfade der Vorhersage verfolgt. Derjenige Pfad, der die zutreffendsten Vorhersagen gemacht hat, bekommt eine größere Priorität zugewiesen und dessen Pfad wird für die nächsten Berechnungen verfolgt. Eine TAGE Branch Prediction hat zudem eine relativ lange Historie, beachtet dabei aber nicht nur die eines Pfades, sondern von gleich mehreren. Dies macht eine TAGE Branch Prediction zum aktuell effektivsten Verfahren.

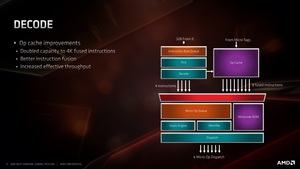

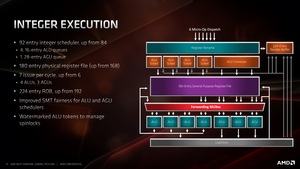

Der Micro Op Cache kann doppelt so viele Instruktionen fassen. Für Zen 2 sind es nun 4K, bei Zen und Zen+ sind es nur 2K. Die Anzahl der Adress Generation Units (AGU) hat AMD von zwei auf drei erhöht.

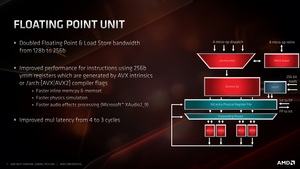

Von besonderer Bedeutung sind die zwei 256 Bit Floating Point Units, die AVX256-Befehlssätze verarbeiten können. Außerdem gibt es zwei Loads und einen Store pro Cycle, um die Daten doppelt so schnell in die Floating-Point-Engine zu bekommen.

Der L1-Cache kann 32 Byte/Cycle mit dem L2-Cache austauschen. Dies gilt in eine Richtung für den Instructions-Cache, der Data-Cache kann ebenfalls 32 Byte/Cycle in den L2-Cache übertragen oder aus diesem lesen. Der L2-Cache wiederum liest und schreibt 32 Byte/Cycle aus dem L3-Cache. Der L3-Cache wurde auch deswegen vergrößert, weil man zu viel Datentransfer über den Infinity Fabric minimieren wollte.

Doch nicht nur die Caches sind angewachsen, auch die dazugehörigen Register wurden vergrößert. So fasst der L1 BTB nun 512 anstatt nur 256 Einträge. Für den L2 BTB geht es von 4K auf 7K.

Auf Seiten der Fließkomma-Einheiten haben wir die beiden 256 Bit breiten Einheiten bereits erwähnt. Deren Mul-Latenz wurde zudem von vier auf drei Cycles reduziert.

Für Integer-Berechnungen gibt es ebenfalls noch weitere Verbesserungen. So ist der Integer Scheduler von 84 auf 92 Einträge vergrößert worden. Das physikalische Register File wird von 168 auf 180 Einträge erweitert. Anstatt sechs können nun sieben Issue pro Cycle verarbeitet werden. Dies teilt sich auf vier ALUs und drei AGUs auf.