Werbung

Die Fertigung in 7 nm und das Chiplet-Design macht es möglich, drei Chips (zwei CPU-Dies und einen I/O-Die) auf einem Pachage unterzubringen. War ein CCX bei Zen+ noch 60 mm² groß, sind es bei Zen 2 nur noch 31,3 mm². AMD bringt damit doppelt so viele Kerne im gleichen Package unter. Je nach Anwendung skalieren diese auch extrem gut. Geringe Speicherlatenzen und der Infinity Fabric sollen dabei die Hauptrolle spielen – aber dazu kommen wir noch.

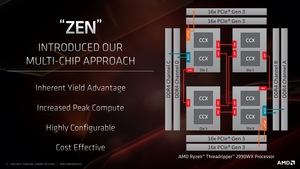

Die Topologie der Ryzen-Prozessoren sieht derzeit wie folgt aus:

Für die Ryzen-Prozessoren mit sechs und acht Kernen sieht AMD einen CCD (Core Complex Die) und einen I/O-Die vor. Über den Infinity Fabric wird ein Interconnect zwischen den beiden Chips hergestellt. Der Datenaustausch findet mit 32 Byte/Cycle in beiden Richtungen statt.

Die Ryzen-Prozessoren mit 12 oder 16 Kernen verwenden bei CCDs. Diese sind aber ebenfalls über einen Interconnect mit dem I/O-Die angebunden und kommen auf jeweils 32 Byte/Cycle.

Die Ryzen-Prozessoren der dritten Generation verwenden die zweite Generation des Infinity Fabric. Dieser stellte schon bei den Multi-Chip-Module-Prozessoren (MCM) das Rückgrat der Interconnect-Infrastruktur dar. Mit der zweiten Generation ist dessen Bus von 256 auf 512 Bit verdoppelt worden. Die Abfragen über den Infinity Fabric wurden in vielen Bereich beschleunigt. War der Takt des Infinity Fabric bisher an den Speichertakt gekoppelt, können diese nun entkoppelt werden. Ab einem Takt von DDR4-3733 setzt der Speicherteiler ein. Dann laufen der Infinity Fabric und der Speichertakt nicht mehr im 1:1 Mode, sondern im 2:1 Mode. Dies ermöglicht dann zwar höhere Speichertaktraten, erhöht aber auch die Latenzen.

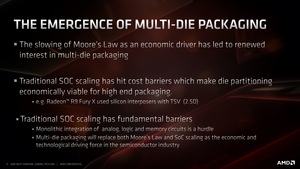

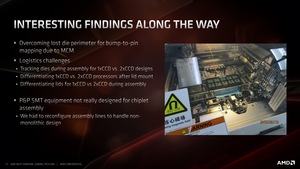

Packaging als weitere Herausforderung

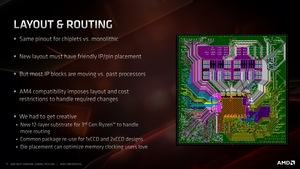

Zwei CPU-Dies in 7 nm, ein I/O-Die in 12 nm, schneller Speicher, PCI-Express 4.0 – dies alles hat Auswirkungen auf das Packaging. So besteht das Substrat auf dem die Chips sitzen nun aus zwölf Layern (die Hälfte davon für die Spannungsversorgung) – bisherige Prozessoren im MCM-Design hatten acht oder zehn Layer. Nur zwei Firmen können ein solches Package überhaupt fertigen. Beide sitzen in Japan und bei beiden ist AMD bereits längere Zeit für verschiedene Produkte Kunde.

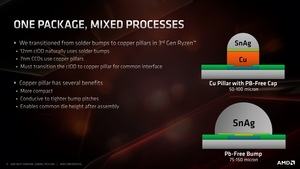

Änderungen gibt es außerdem in der Art und Weise der Kontaktierung zwischen den Chips und dem Substrat. So liegt der Bumb Pitch, also der Abstand zwischen den tausenden BGAs auf der Unterseite der Chips, bei den Dies, die in 12 nm gefertigt werden, bei 150 µm. Bei den neuen 7-nm-Dies sind es nur 130 µm. AMD, bzw. der Fertiger verwenden bei den neuen Prozessoren nun schmalere Kupfer-Pillars, die den Kontakt zwischen Chip und Substrat herstellen. Das Substrat ist bei allen Prozessoren – egal ob mit einem CCD oder zwei CCDs – identisch.

In der folgenden Galerie werden einige der oben erwähnten Details noch einmal genauer erläutert:

Der Kompatibilität des Sockels AM4 reicht von Excavator bis Matisse – also von 28 bis zu 7 nm, von einem monolithyischen Prozessor bis zum Chipet-Design, von PCI-Express 3.0 bis 4.0 und von DDR4-2600 bis DDR4-3200. Dies stellt natürlich besondere Herausforderungen an das Routing.

Eine gewisse Herausforderung stellt das Packaging auch dahingehend dar, als dass AMD die von TSMC gefertigten Chips noch selektiert und entsprechend zuordnen muss. Der Ryzen 9 3950X bekommt die besten Chips zugeteilt. Inwieweit die neuen EPYC-Prozessoren eine gewisse Zuteilung bekommen, wollte AMD nicht verraten.