Werbung

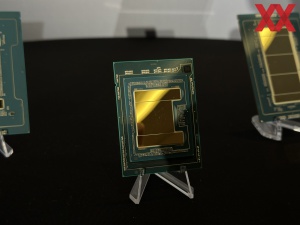

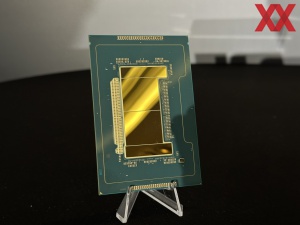

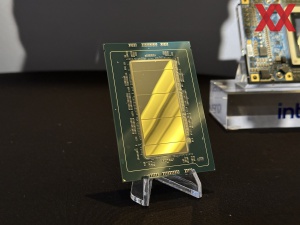

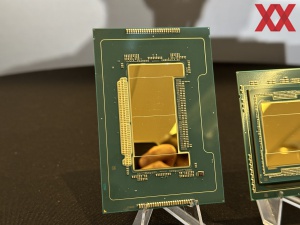

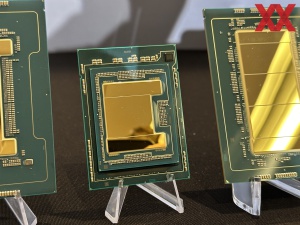

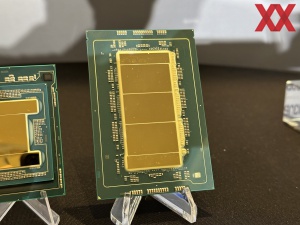

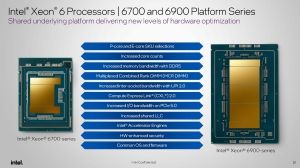

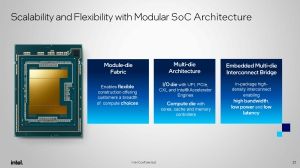

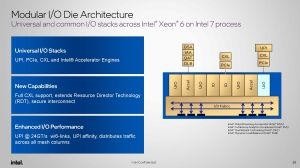

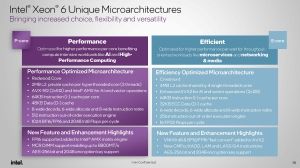

Mit der Xeon-6-Serie bestreitet nun auch Intel den Weg des Chiplet-Designs und setzt das Package aus verschiedenen Chips zusammen. Es gibt I/O-Tiles, welche sämtliche I/O-Funktionen und auch die Beschleuniger enthalten. Ein I/O-Fabrik im I/O-Tile sorgt dafür, dass die I/O-Blöcke und Beschleuniger ausreichend schnell angebunden sind. Die Verbindung zwischen I/O- und Compute-Tile erfolgt mittels EMIB. Die Compute-Tiles wiederum beherbergen die E- und P-Kerne. Während die Xeon-6-Prozessoren immer zwei I/O-Tiles enthalten, kann Intel über die Anzahl der Compute-Tiles festlegen, wie viele Kerne zum Einsatz kommen.

Ausgehend von vier Chips im Package für Sapphire Rapids und dann zwei Chips für Emerald Rapids, stellen die Xeon-6-Prozessoren demnach einen deutlichen Wechsel im Design des Package dar.

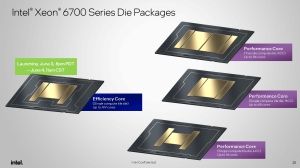

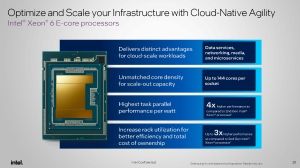

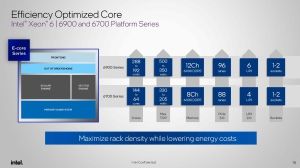

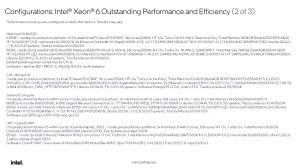

Für die Xeon-6700E-Serie kommt ein Compute-Tile mit den E-Kernen zum Einsatz. Für die Xeon-6700P-Serie wird Intel zwei Compute-Tiles mit jeweils bis zu 43 aktiven CPU-Kernen (XCC, Extreme Core Count) verwenden. Die darunter positionierte Xeon-6500P- und Xeon-6300P-Serien verwenden jeweils einen Compute Tile mit 48 Kernen (HCC, High Core Count) und 16 Kernen (LCC, Low Core Count).

Die Xeon-6900P-Serie wird neben zwei I/O-Tiles auf drei Compute-Tiles setzen, die sich die 128 Kerne aufteilen. Auch wenn Intel diese Compute-Tiles als UCC (Ultra Core Count) bezeichnet, so dürften hier dieselben Chips zum Einsatz kommen wie in der Xeon-6700P-Serie. Für die Xeon-6900E-Serie setzt Intel auf zwei Compute-Tiles mit jeweils 144 E-Kernen, sodass wir hier insgesamt auf 288 Kerne kommen. Der Einsatz von zwei Compute-Tiles mit E-Kernen und drei Compute-Tiles mit P-Kernen ist notwendig, damit Intel die 12 Speichercontroller auf der Plattform anbieten kann, denn diese befinden sich nicht in den I/O-Tiles, sondern in den Compute-Tiles.

Im Compute-Tile sind alle Kerne und Caches über ein Mesh-Interconnect angebunden. Der Last Level Cache (LLC) steht allen Kernen zur Verfügung, es kann aber auch eine NUMA-Clustering gewählt werden. Die Speichercontroller befinden sich wie gesagt mit in den Compute-Tiles. Intel wählt diesen Ansatz sicherlich, um die Latenzen und Bandbreite zu den Kernen möglichst gering bzw. hoch zu halten. AMD fährt hier ein anderes Konzept. Die CCDs beinhalten nur die Kerne, während sämtliche I/O-Funktionen und auch die Speichercontroller im IOD sitzen.

An dieser Stelle wollen wir die Funktion der einzelnen Beschleuniger noch einmal erläutern:

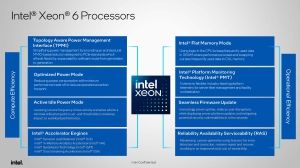

- QAT (QuickAssist Technology): Ist nun Teil des Kerns und für Verschlüsselung und Kompression von Datenstreams vorgesehen. Network Secure Gateways und Content Delivery Networks sind zwei der denkbaren Anwendungen für QAT.

- DLB (Dynamic Load Balancer): Der DLB sorgt für ein besseres Load Balancing und eine bessere Auslastung der Kerne auch für wenig anspruchsvolle Workloads. Als eine QoS können bestimmte Pakete in der Pipeline auch priorisiert werden

- DSA (Data Streaming Accelerator): Speicherzugriffe laufen nicht mehr über die Kerne, sondern können teilweise ausgelagert werden. Dies kann für eine Datenanalyse und Distributive-Storage-Dienste sinnvoll sein.

- IAA (In-Memory Advanced Analytics Accelerator): Daten werden aus dem Speicher gelesen und in diesen geschrieben, die Dekompression und Kompression erfolgen im IAA und werden von dort in den LLC übertragen. In-Memory Datenbanken, Datenanalyse oder Datenbanken allgemein sind Anwendungsfelder von den IAA.

Einige der weiteren I/O-Blöcke können frei konfiguriert werden. So können die Standard-I/O-Blöcke als PCI-Express- oder CXL-Lanes verwendet werden. Die UIP-Blöcke können zudem auch für ein UPI verwendet werden. Für 1S- und 2S-CPUs verzichtet Intel teilweise darauf und kann daher mehr PCI-Express- und CXL-Lanes anbieten.

Intel plant offenbar auch spezielle 1S-Varianten namens Xeon 6 R1S, die auf UPI verzichten und somit satte 136 PCI-Express-Lanes anbieten können.

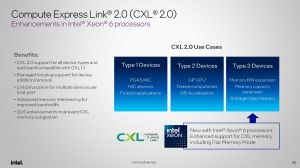

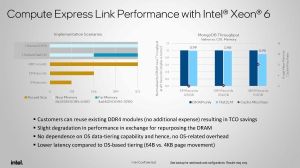

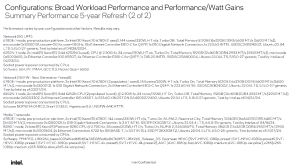

CXL 2.0 Type 3

Die Xeon-6-Prozessoren werden erstmals auch Type 3 für CXL 2.0 unterstützen. Für Type 3 geht es maßgeblich darum die Möglichkeiten der Speichererweiterung zu erweitern.

In CXL 2.0 Type 3 kann ein NUMA-Clustering des Speichers stattfinden. Dies beinhaltet auch die Kenntnis dieser Aufteilung gegenüber dem Hypervisor. Die Xeon-6P-Prozessoren unterstützen zudem ein CXL Hetero Interleaving. Hier wird der CXL-Speicher in der Speichererweiterung zum DRAM-Adressraum hinzugenommen. Die Erweiterung der Kapazität geht auch mit einer höheren Speicherbandbreite einher, denn zu den acht bzw. zwölf Speicherkanälen kommen durch das CXL Hetero Interleaving vier weitere hinzu.

Zudem gibt es nun noch einen Flat Memory Mode, in dem der Prozessor in eigener Hardware festlegt, welche Daten sich im DRAM oder in der CXL-Speichererweiterung befinden sollen. Dies ist natürlich abhängig davon, wie groß der DRAM selbst ist und ob der ständig benötigte Datensatz komplett in den DRAM passt oder nicht.

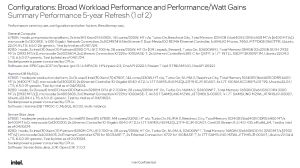

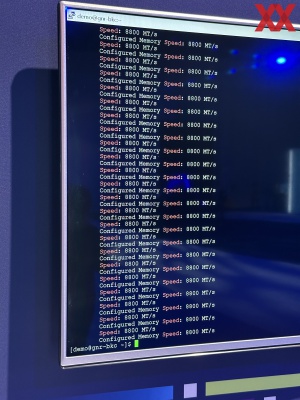

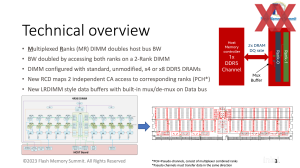

MCR: Noch nicht für Xeon 6700E

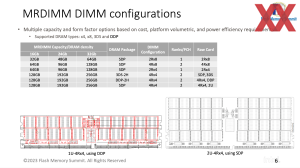

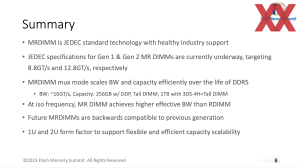

Ein wichtiger Punkt der Birch-Stream-Plattform wird die Unterstützung von DDR5 mit MCR sein. MCR steht für Multiplexer Combined Ranks und ist ein von Intel, Renesas und SK Hynix entwickelter neuer Standard für Server-Arbeitsspeicher. Gezeigt hat Intel den Betrieb von MCR bereits mit Granite Rapids in einer Quad-Channel-Konfiguration mit 6.400 MT/s, später dann auch deutlich schneller mit 8.800 MT/s und so wird er auch von den P-Kern-Xeons unterstützt werden.

Die Funktionsweise der MCR-DIMMs ist dabei vergleichsweise einfach. Der DRAM arbeitet mit der halben Signalrate, in diesem Fall 4.400 MHz. Zwei Pseudo-Kanäle werden per Multiplex-Verfahren wieder zusammengeführt und so ergeben sich aus 2x 4.400 MT/s eben zusammengenommen 8.800 MT/s.

Die heute getesteten Xeon-6700E-Prozessoren müssen also noch auf MCR verzichten. Anders wird dies in wenigen Wochen für die Xeon-6900P-Serie aussehen.

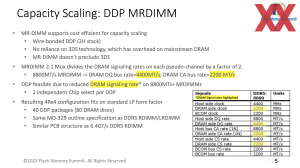

Starten sollen die MCR-DIMMs also mit 8.800 MT/s, in den nächsten Generationen soll es dann auf 12.000 MT/s und 16.000 MT/s gehen. Der klassische DDR5-Speicher wird in diesem Jahr den Schritt auf 6.400 MT/s machen – so wie heute in der getesteten Achtkanal-Konfiguration.

Die Nachteile der MCR-DIMMs sind in etwa 2-3 ns an Latenz die hinzukommen und eine etwas höhere Abwärme der Module. Auf dem Flash Memory Summit zeigte Intel einen Vergleich zwischen RDIMMs mit 4.400 MT/s und MCR-DIMMs bei 8.800 MT/s. Die Kapazität betrug jeweils 64 GB. Während die RDIMMs auf eine Leistungsaufnahme von 9 W kommen sollen, sind es für die MCR-DIMMs 16,5 W. Eine Verdopplung der Bandbreite bei einer "nur" 80 % höheren Leistungsaufnahme klingen zunächst einmal sicherlich gut. Inzwischen aber dürften die RDIMMs mit 5.600 MT/s ebenfalls im Bereich von 9 W liegen und dann schmilzt dieser Vorteil von MCR deutlich zusammen.

Die Tests der Xeon-6900P- und später auch der Xeon-6700P-Serie werden also dahingehend spannend werden, denn es wird auf die jeweilige Anwendung ankommen, die vom schnelleren Arbeitsspeicher profitiert.