Werbung

Neben NVIDIA, mit den Verkäufen der entsprechenden AI-Hardware, ist auch TSMC einer der großen Profiteure des aktuellen AI-Hypes, denn hier werden die größten und aufwendigsten der aktuellen Chips gefertigt. Entsprechend hat man auch große Pläne und baut die Kapazitäten weiter aus. Aber TSMC ist nicht der einzige Hersteller, der groß in seine Packaging-Werke investiert, auch bei Intel laufen die Baumaschinen in Malaysia (Werk "Pelican") und in den USA auf Hochtouren – bald womöglich auch in Polen.

In der kommenden Woche wird TSMC weltweit sein 2023-OIP-Ecosystem-Forum abhalten. Im Rahmen dessen, werden Neuigkeiten rund um 3Dblox 2.0 und 3DFabric-Technologien erwartet.

Hinter den Begriff 3DFabric verbergen sich mehrere Technologien, die allesamt ein 2.5D oder 3D-Verfahren für das Zusammenbringen mehrere Chips in einem Package beschreiben. Apple ist einer der großen Packaging-Kunden von TSMC. Der für gewöhnlich verschwiegene Konzern aus Cupertino spricht aber nicht so gerne darüber. Schon anders sieht dies bei AMD aus. Prozessoren und Techniken wie der 3D V-Cache oder die Instinct-Beschleuniger wären ohne TSMCs Fertigungs- und Packaging-Angebot für AMD gar nicht möglich umzusetzen.

Mit 3Dblox will TSMC das Design solcher 3D-Chips vereinfachen und vor allem einfacher zugänglich machen. Was die EDA-Werkzeuge in der Fertigung sind, soll 3Dblox 2.0 für das Packaging sein. Potentielle Kunden können vorab simulieren, welche Chips sie mit welchen Charakteristika zusammenbringen wollen und welche Auswirkungen dies auf das Gesamtdesign hat. Schnelle Zyklen in der Fertigung und ein möglichst leistungsstarkes finales Design sollen das Ergebnis sein. Im dazugehörigen Komitee sitzen Unternehmen wie Ansys, Cadence, Siemens und Synopsys, die IP-Designs und interoperable EDA-Werkzeuge beisteuern sollen.

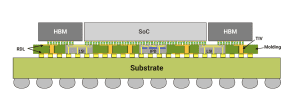

Das was wir heute in Form von 2.5D-Packages sehen, soll so in Zukunft noch weitaus komplexer im Aufbau, aber einfacher in der Umsetzung werden. Egal ob bei TSMC oder Intel – die Unternehmen werben mit mehr Interoperabilität. Bisher hat aber nur Intel eine solche auch wirklich umgesetzt. Für Meteor Lake kommen Chiplets von Intel selbst und TSMC zusammen. Ansonsten sehen die Packages meist nur ein oder mehrere Chiplets eines Hersteller vor, zu denen dann noch HBM, GDDR- oder LPDDR-Speicher von Micron, Samsung Memory, oder SK hynix dazu gepackt wird.

Auch Intel will die Interoperabilität mehrerer Chip-Hersteller weiter ausbauen. Auf der Innovation 2023 zeigte der Chipreise die Zusammenarbeit mit Synopsys. So wurde auf einem Package ein Chip von Intel und Synopsys per Universal Chiplet Interconnect Express (UCIe) miteinander verbunden.