Werbung

TSMC reiht sich in die Reihe derjenigen ein, für die Moore's law noch lange nicht am Ende ist. Eine Kombination aus voranschreitenden Fertigungstechniken und neuen Design-Ansätzen soll dafür sorgen, dass wir noch über Jahre hinweg regelmäßige Steigerungen in der Packdichte und Rechenleistung sehen werden – so zumindest sieht dies Godfrey Cheng, Leiter des Marketing bei TSMC in einem Blogpost.

Dabei gibt Cheng erstaunliche Einblicke in die aktuellen Möglichkeiten und Pläne des Auftragsfertigers, der neben NVIDIA aktuell auch AMD als Kunde hat und auch für Apple die SoCs der vergangenen Jahre gefertigt hat.

Doch machen wir einen Schritt zurück: Vor einigen Jahren wurde von zahlreichen Seiten das Ende von Moore's law vorhergesagt. Damals zeichnete sich ab, dass die Fertigungstechniken an eine Grenze stoßen und so hätte laut NVIDIA Moore's law nur noch durch die Parallelisierung in der Auslegung von Architekturen Bestand. Intel sieht über das Hyperscaling eine Möglichkeit, das Wachstum an Rechenleistung aufrecht zu erhalten. Doch die Probleme mit der 10-nm-Fertigung bei Intel haben die Pläne hier etwas verzögert. Intels Jim Keller will Moore’s law durch eine Kombination verschiedener Maßnahmen neu aufleben lassen.

TSMC will den Fortbestand von Moore's law ebenfalls durch verschiedene Maßnahmen sicherstellen. So arbeitet man derzeit bereits an Fertigungstechniken in 5 nm und befindet sich hier auch schon in der Risikofertigung. Aktuell in der Massenfertigung befinden sich N7 und N7P – auch für AMDs aktuelle Ryzen- und EPYC-Prozessoren sowie die Navi-GPUs. N5 und N5P wird dann auch verstärkt EUV in der Belichtung der Chips verwenden. Die extrem ultraviolette Strahlung wird in mehr und mehr Schichten verwendet werden. Sind es aktuell aufgrund der Kosten und Komplexität nur einige wenige, sollen es bei N5P fast alle Schichten eines Chips sein.

Die Packdichte bei den Transistoren wird also weiter gesteigert und sorgt gleichzeitig dafür, dass die Leistung weiter gesteigert und Leistungsaufnahme weiter reduziert werden können.

Eine weitere Maßnahme ist der aktuelle Trend zu modularen Designs und Chiplets. AMD macht dies mit den Ryzen- und EPYC-Prozessoren vor und über kurz oder lang wird sich auch Intel in diese Richtung bewegen. Am deutlichsten wird dies aktuell in der FPGA-Strategie von Intel, aber auch die Ice-Lake-Prozessoren mit Sunny-Cove-Kernen geben die Richtung für die Zukunft vor.

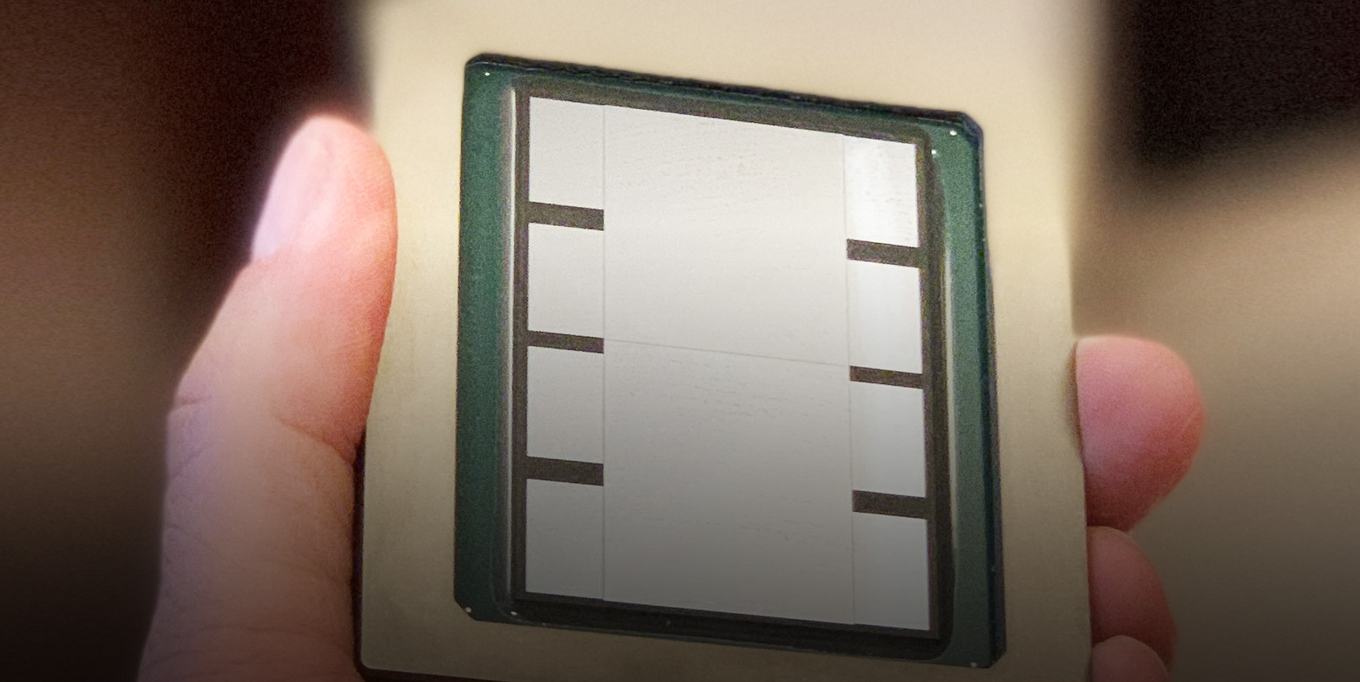

Erst kürzlich zeigte TSMC eigene Chiplet-Techniken für ARM-HPC-Prozessoren. Dabei kommen verschiedene Packaging- und Interconnect-Technologien zum Einsatz. Über einen Low-voltage-In-Package-Interconnect (LIPINCON) werden verschiedene Chips mittels eines 1.968 Bit breiten Bus miteinander verbunden. Die Chip-on-Wafer-on-Substrate (CoWoS) Packaging-Technologie ermöglicht die technische Umsetzung verschiedener Chips in einem Package.

Letztendlich zeigt TSMC ein Package bestehend aus zwei 600 mm² großen Chips, an die jeweils vier, also insgesamt acht, HBM-Chips angebunden sind. Die Chips kommen somit zusammengenommen auf 1.800 mm², die allesamt auf einem 2.500 mm² großen Interposer untergebracht sind. Bis vor wenigen Jahren wäre es unvorstellbar gewesen, solch riesige Chips in einer derart kleinen Fertigung herstellen zu können. Die Packaging-Technologien ermöglichen aber erst die Zusammenarbeit der verschiedenen Chips in einer möglichst effektiven Art und Weise, da die Interconnect-Datenraten und Latenzen deutlich reduziert werden können.

TSMC ist aber nicht der einzige Hersteller, der an solchen technischen Umsetzungen arbeitet. Intel präsentierte erst kürzlich eine Weiterentwicklung von EMIB (Embedded Multi Die Interconnect Bridge) als Co-EMIB und ein Omni-Directional Interconnect (ODI) soll die Kommunikation zwischen den Chips beschleunigen. Mit der aktuellen Ryzen-Generation sprach AMD auch ausführlich über die Herausforderungen und Umsetzungen des Packaging.

Die kommenden Jahren werden also als vielerlei Hinsicht interessant werden. Neben der immer kleineren Fertigung steigt die Komplexität der Designs zukünftig, vor allem auch die Weiterentwicklungen beim Packaging und diese Entwicklungen werden wir mit größtem Interesse verfolgen.