Werbung

In den vergangenen Tagen drehte sich in Kalifornien auf der Hotchips 2019 vieles um die zukünftigen Lösungen in der Fertigung und letztendlich auch Ausführung moderner Fertigungstechnologien. Unter anderem gezeigt wurde ein riesiger Chip mit einer Fläche von 46.225 mm², der 400.000 Kerne enthalten soll. Intel zeigte seine AI-Beschleuniger NNP-I und NNP-T in allen Details und AMD hat einige weitere Fakten zu den EPYC-Prozessoren der zweiten Generation verraten.

Kurz vor der Hotchips-Konferenz zeigte TSMC ein riesiges Chiplet-Design mit ebenso gigantischem Interposer. Auf der Konferenz selbst sprach der Auftragsfertiger über die aktuellen und zukünftigen Voraussetzungen in der Halbleiterfertigung. Kurzfristig seien die Vorgaben von Moores Law vor allem durch immer kleinere Fertigungsschritte weiter einzuhalten – so TSMC. So arbeitet man derzeit bereits an Fertigungstechniken in 5 nm und befindet sich hier auch schon in der Risikofertigung. Aktuell in der Massenfertigung befinden sich N7 und N7P – auch für AMDs aktuelle Ryzen- und EPYC-Prozessoren sowie die Navi-GPUs. N5 und N5P wird dann auch verstärkt EUV in der Belichtung der Chips verwenden.

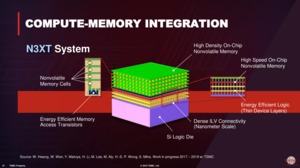

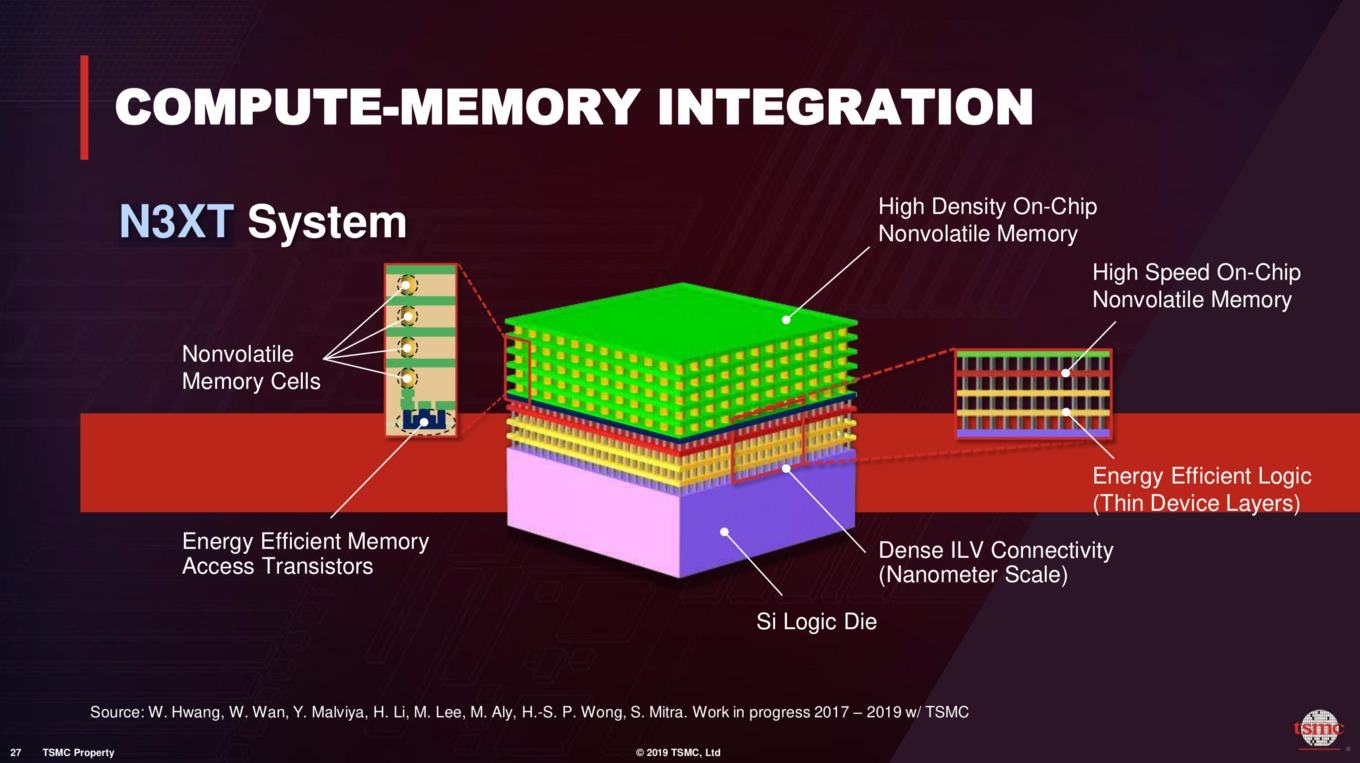

Die Packdichte bei den Transistoren wird in einer Ebene also weiter gesteigert und sorgt gleichzeitig dafür, dass die Leistung weiter gesteigert und Leistungsaufnahme weiter reduziert werden können. Neue Packaging-Technologien sorgen gleichzeitig dafür, dass die Chips nicht mehr nur in einer Ebene immer größer und komplexer werden können, sondern sollen neben den schon etablierten 2,5D-Designs auch größere 3D-Designs möglich machen.

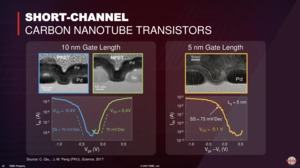

Dabei müssen immer kleinere Fertigungstechniken mit den Packaging-Technologien einhergehen. N3, also eine Fertigung in 3 nm hat TSMC schon konkret ins Auge gefasst. Gedanklich ist man aber schon viel weiter und spricht sogar von 1,4 nm. Dabei muss man sich die Strukturgrößen noch einmal vor Augen halten, über die hier gesprochen wird.

Ein menschliches Haar hat einen Durchmesser von 0,1mm. Ein Bakterium kommt auf 2 µm und ein Virus bringt es typischerweise auf 50 nm. In Kohlenstoffnanoröhrchen werden Abstände von 1,2 nm zwischen den Carbon-Atomen erreicht. Nominell sprechen die Halbleiterhersteller bereits über 7 nm, die aktuell gefertigt werden. Die Pläne gehen aber wie gesagt schon sehr viel weiter. Dabei hat diese Angabe recht wenig mit der tatsächlichen Größe oder dem Abstand einzelner Komponenten und Bauteile eines Transistors im Halbleitermaterial zu tun, aber zur Orientierung taugen die Angaben. Neue Materialen sind für TSMC also der Schlüssel für eine stetige Weiterentwicklung in diesem Bereich.

Chipet-Designs auch für TSMC unabdingbar

TSMC hat bereits mehrfach deutlich gemacht: Ohne ein Chiplet-Design sind die Anforderungen an eine immer höhere Rechenleistung bzw. größere Packdichte nicht zu erfüllen. Aus der Präsentation einer Chiplet-Technik für ARM-HPC-Prozessoren sowie der bereits angesprochenen Präsentation eines riesigen Chiplet-Designs mit ebenso gigantischem Interposer geht dies für das Taiwanesische Unternehmen klar hervor.

Zusammen mit AMD hat man nun die ersten kommerziellen Produkte in der Massenfertigung und erwartet eine immer stärkere Verbreitung des Trends in den kommenden Jahren. Aber laut TSMC ist dies kein wirklich neuer Trend. Die Notwendigkeit den Speicher immer näher an die verarbeitenden Chips zu bekommen, hat schon vor einigen Jahren zu einer Weiterentwicklung in diesem Bereich geführt. Die Verwendung von HBM bei den GPUs ist ein gutes Beispiel – sowohl AMD als auch NVIDIA haben bereits gezeigt, dass dies auch im Endkundenbereich umsetzbar, wenngleich relativ teuer ist. Für Datacenter-Produkte sind Beschleunigerchips ohne HBM kaum noch denkbar.

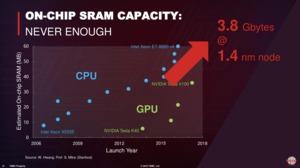

In Zukunft werden die Speicher und die Compute-Einheiten noch dichter zusammenrücken müssen. Auch dies ist als genereller Trend der diesjährigen Hotchips-Konferenz zu erkennen. So präsentierte ein französisches Startup namens UPMEM einen DIMM-Speicher, bei dem die Compute-Einheiten direkt in den DRAM verbaut sind. Der bereits erwähnte riesige Chip von Cerebras kommt zudem mit 18 GB an SRAM daher, was die Wichtigkeit von On-Chip-Speicher unterstreicht.

Auch in diesem Bereich wird es laut TSMC in den kommenden Jahren eine rasante Weiterentwicklung geben. Die eben bereits angesprochene und theoretische Fertigung in 1,4 nm würde die theoretisch zur Verfügung stehende SRAM-Kapazität auf einem Chip auf mehrere Gigabyte steigern.

TSMC sieht sich aber gut aufgestellt die zukünftigen Herausforderungen bewältigen zu können. Sie würden komplexer, da sie auf verschiedenen Ebenen stattfinden (neue Fertigungsgrößen, neue Packaging-Verfahren, ...), aber sie sind laut TSMC zu bewältigen und so sieht das Unternehmen keinen Grund am Fortbestand von Moore's Law auch über die kommenden Jahre hinweg zu zweifeln.

Vor einigen Jahren wurde von zahlreichen Seiten das Ende von Moore's Law vorhergesagt. Damals zeichnete sich ab, dass die Fertigungstechniken an eine Grenze stoßen und so hätte laut NVIDIA Moore's Law nur noch durch die Parallelisierung in der Auslegung von Architekturen Bestand. Intel sieht über das Hyperscaling eine Möglichkeit, das Wachstum an Rechenleistung aufrecht zu erhalten. Doch die Probleme mit der 10-nm-Fertigung bei Intel haben die Pläne hier etwas verzögert. Intels Jim Keller will Moore’s Law durch eine Kombination verschiedener Maßnahmen neu aufleben lassen.