Werbung

Auf der HPC-AI Advisory Council UK Conference sprach Martin Hilgeman, verantwortlich für HPC Applications bei AMD, über die aktuellen EPYC-Prozessoren auf Basis von Rome, gab dabei aber auch einen Ausblick auf den Nachfolger Milan.

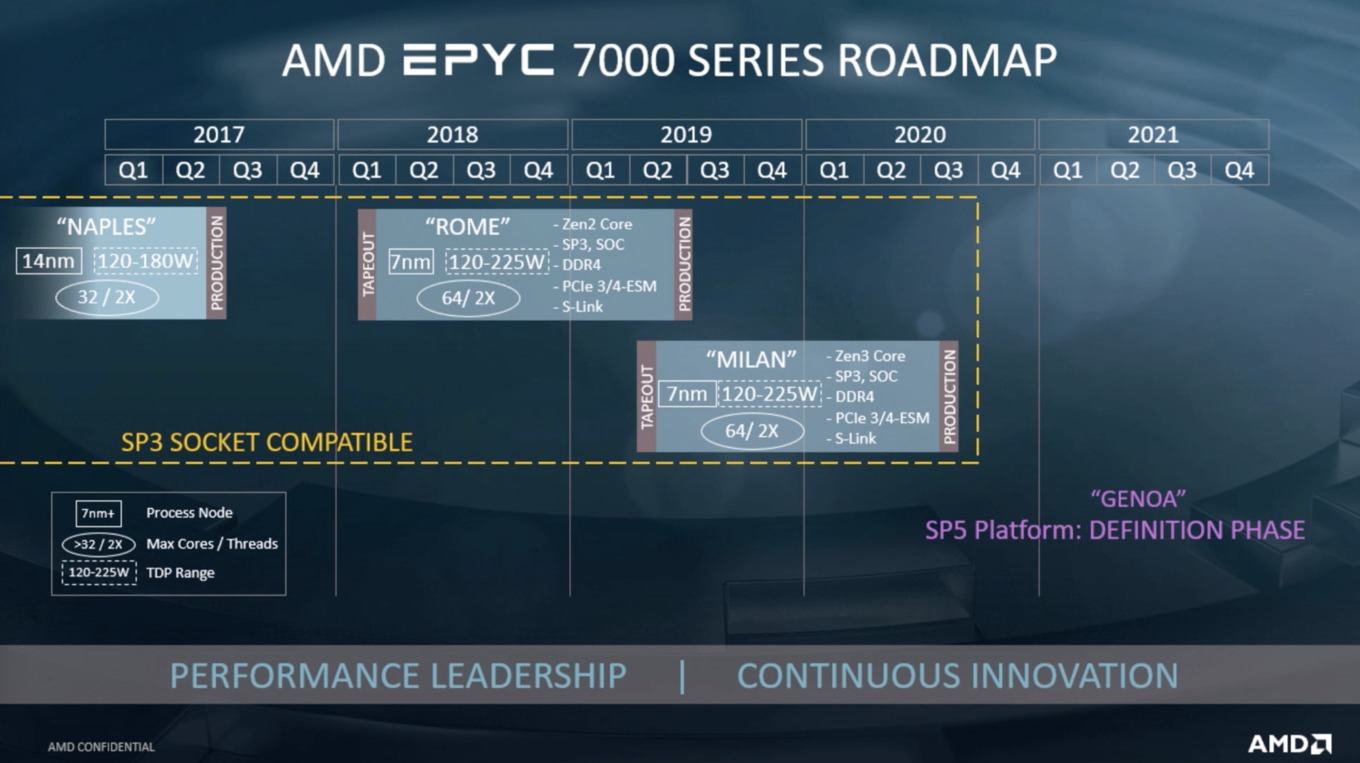

Der von ihm gezeigten EPYC-7000-Series-Roadmap zufolge haben die Milan-Prozessoren ihren ersten Tape-Out schon hinter sich gebracht. Aktuell befindet sich das Design demnach in der Qualification-Phase und wird geprüft. AMD hat bereits bestätigt, dass die Zen-3-Architektur die Design-Phase abgeschlossen hat. Werden Fehler gefunden, muss das Design noch einmal überarbeitet werden. Der Beginn der Produktion ist für das 3. Quartal 2020 angesetzt.

Offenbar plant AMD weiterhin die Fertigung in 7 nm. Die in der Legende beispielhaft angeführten 7nm+ führt AMD in der Roadmap für Milan bzw. Zen 3 nicht auf. Zudem soll die Thermal Design Power weiterhin von 120 bis 225 W reichen. Allerdings gibt es in der aktuellen Generation auch Spezialmodelle wie den EPYC 7H12, der sich bis zu 280 W genehmigt.

Die Anzahl der Kerne wird mit 64 angegeben. Somit bliebe man auf dem aktuellen Niveau. Ein SMT4 scheint nicht geplant zu sein, auch wenn die Gerüchteküche diesbezüglich kürzlich heftig brodelte. Mit zwei Threads pro Kern sind bei 64 Kernen also 128 Threads möglich. Analog sollte dies für die Ryzen-Ableger auf Basis von Zen 3 gelten. Ebenfalls keinerlei Änderungen gibt es beim Sockel. AMD wird einmal mehr den Sockel SP3 verwenden. DDR4 wird der Standard für den Arbeitsspeicher bleiben und da AMD am Sockel SP3 festhält, werden es weiterhin acht Speicherkanäle sein. Auch PCI-Express 5.0 werden wir mit den EPYC-Prozessoren im kommenden Jahr noch nicht sehen. AMD führt in der Roadmap PCIe 3/4 an – auch hier also keinerlei Änderungen.

Die übernächste Generation der EPYC-Prozessoren alias Genoa befindet sich der Roadmap zufolge aktuell in der Definitionsphase. Es wird aber offenbar mit dem SP5 einen neuen Sockel geben. Da DDR5 und PCI-Express 5.0 auf dem Plan stehen, verwundert es auch nicht, dass AMD hier einen neuen Sockel bringen wird.

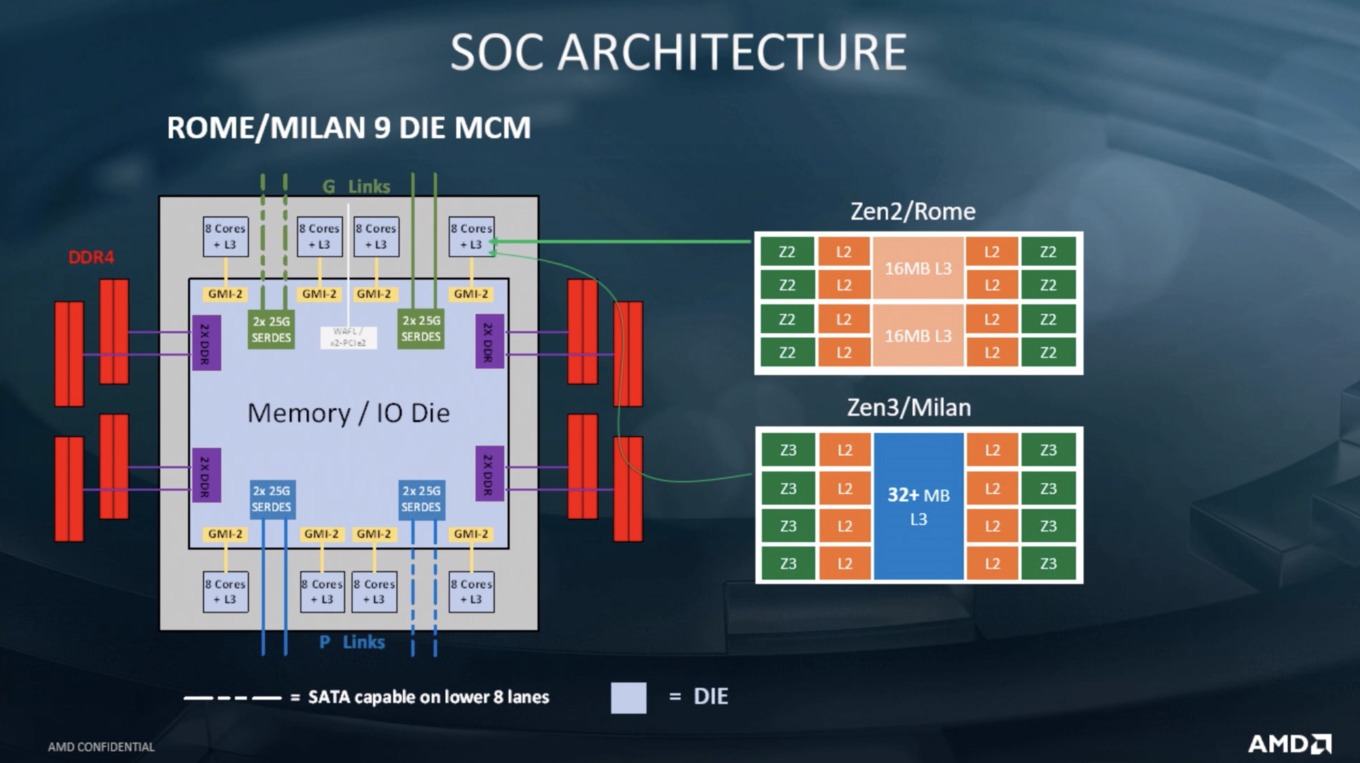

Ein kleines weiteres Detail verrät AMD zur Zen-3-Architektur. Für diese wird es offenbar eine Änderung im Aufbau des Core Compute Die (CCD) und damit auch des Core Compute Complex (CCX) geben. Der aktuell verwendete Valhalla-Die besteht als CCD aus jeweils zwei CCX-Clustern, in denen auch der L3-Cache in zweimal 16 MB aufgeteilt ist. Dies war auch schon bei den Zeppelin-Dies der Fall.

Für Zen 3 soll dies anders aussehen. Eine schematische Darstellung zeigt den CCD mit einem gemeinsamen L3-Cache. Ob es überhaupt noch zwei CCX pro CCD gibt, ist nicht bekannt. Zudem will AMD noch nicht die Größe des gemeinsamen L3-Caches verraten. Mehr als 32 MB sollen es laut der Darstellung aber sein.

Außerdem zeigt ein Blockdiagramm noch einmal den Aufbau des MCM-Designs bestehend aus acht CCDs und einem I/O-Die (IOD). Dieser Aufbau soll auch für Milan beibehalten werden. Deutlich zu erkennen sind zudem die acht Speicherkanäle sowie die entsprechenden Links zwischen den CCDs und dem IOD.

Nach dem grundlegenden Umbau mit bis zu acht Compute-Chiplets und einem zentralen I/O-Die scheint AMD für die nächste Generation weniger große Änderungen am grundsätzlichen Design der EPYC-Prozessoren vorzunehmen. Auf die Details der Änderungen in der Zen-3-Architektur darf man natürlich gespannt sein. Hinsichtlich der Anzahl der Kerne scheint AMD aber nächst einmal auf die Bremse zu treten bzw. wird es etwas langsamer angehen lassen.

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen