Werbung

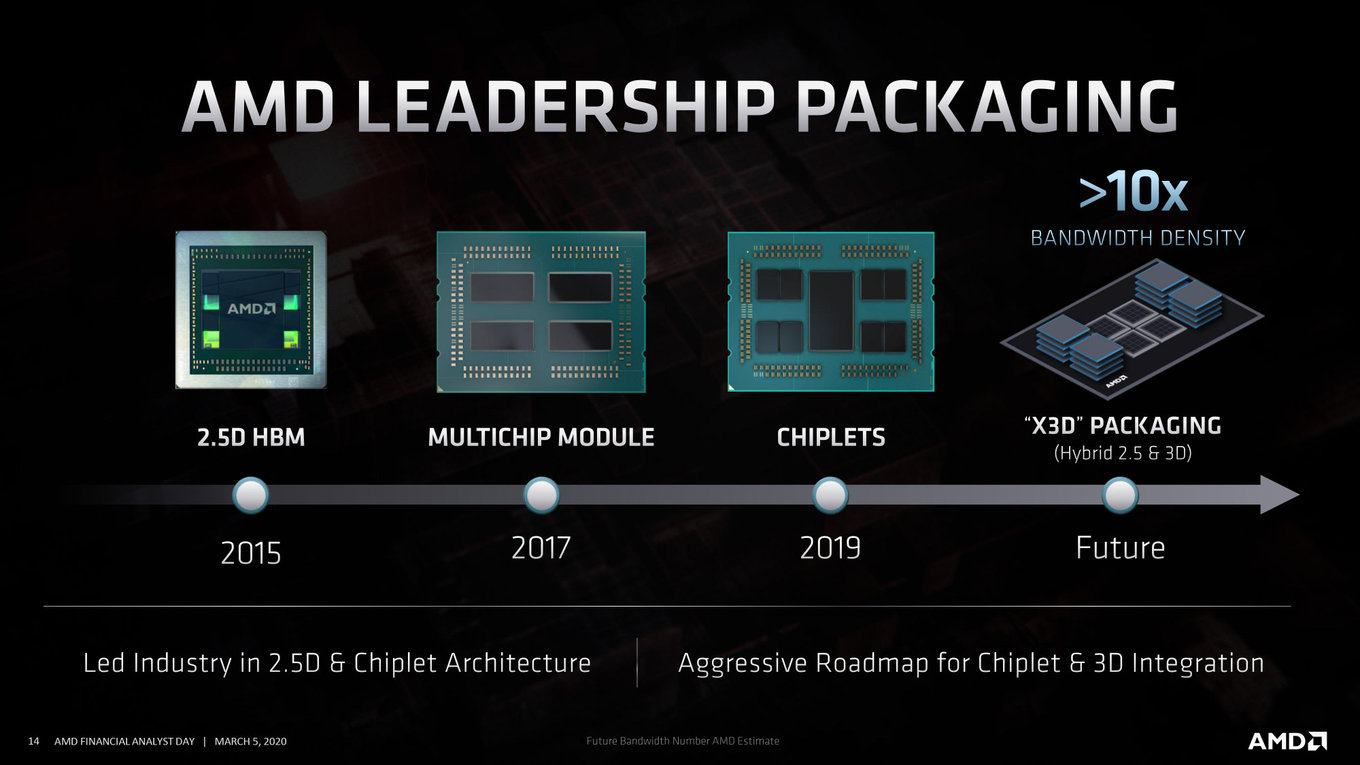

Die Gerüchteküche brodelt derzeit kräftig und kocht dabei über einem Mitte März 2020 von AMD zumindest in einer Vorschau präsentierten Technologie. Dabei handelt es sich um das X3D Packaging, also das stapeln von Chips übereinander. Derzeit führt AMD sein Chiplet-Design so aus, dass ein IOD mit bis zu acht CCDs kombiniert wird. Auf einem Package sind die neun Chips nebeneinander angeordnet. Mit dem X3D Packaging sollen die Chips auch übereinander untergebracht werden.

Zwei bekannte Leaker (Patrick Schur und ExecutableFix) trauen sich nun aus der Deckung und erwähnen den Codenamen Milan-X. Milan lautet die Bezeichnung für das aktuelle EPYC-Design mit Zen-3-Kernen. Milan-X soll nun für die Erweiterung mit X3D Packaging stehen.

Was hier um ein X3D-Packaging erweitert wird, erwähnen beide nicht. Uns wurde zugetragen, dass für die entsprechenden EPYC-Prozessoren der bekannte Milan-IOD zum Einsatz kommt, der um neue CCDs mit daneben gestapelten SRAM-Chips ergänzt wird. Dies würde zusätzlichen Speicher mit hoher Bandbreite recht nahe an den CPU-Kernen bedeutet, wenngleich AMD mit den Zen-3-CCDs bereits 32 MB an L3-Cache recht nahe an den Kernen bieten kann. Für viele der EPYC-Prozessoren sprechen wir daher schon von insgesamt 256 MB an L3-Cache, was deutlich mehr ist als bei Ice Lake-SP mit 60 MB bei 40 Kernen.

Welche Chips hier übereinander gestapelt werden können, hängt also maßgeblich von deren Funktion ab. Mit dem High Bandwidth Memory (HBM) kennen wir bereits solche gestapelten Chips. Allgemein als 2.5D-Ansatz wird beschrieben, wenn solcher HBM über eine Brücke im Interposer mit dem eigentlichen Chip verbunden wird. Im 2.5D befinden sich die wichtigen Chips mit den Recheneinheiten und dergleichen aber noch immer nebeneinander, was vor allem die Kühlung vereinfacht.

Sollte AMD tatsächlich in Kürze einen Milan-X mit X3D-Packaging vorstellen, dann ist hier Speicher als der gestapelte Chip am einfachsten zu realisieren, da die Abwärme hier nicht die wichtigste Rolle spielt. CCDs zu stapeln, ist aufgrund der Abwärme nicht möglich. Zusätzlichen schnellen Speicher an die Kerne zu bringen, ist der wahrscheinlichste Ansatz, den AMD hier fahren wird. Der Platz, der von solch gestapelten Chips, bzw. dem zusätzlichen SRAM genutzt wird, muss an anderer Stelle natürlich wieder eingespart werden. So ist zu vermuten, dass Milan-X kein Prozessor mit 64 Kernen werden wird. Stattdessen wären 4 x 8 Kerne nebst eben dem SRAM denkbar. Die Speicherbandbreite zwischen den CCDs und dem SRAM ist hier von entscheidender Bedeutung und einige Anwendungen profitieren auch besonders davon.

Neben Milan-X ist zudem schon die Rede von Genoa-X, denn ein EPYC-Prozessor mit gestapelten Speicherchips soll kein einmaliges Projekt sein, sondern wie AMD bereits angedeutet, ein Teil einer Produktstrategie. Wann AMD offiziell über Milan-X, bzw. die geplante Technologie spricht, ist noch nicht bekannt.