Werbung

Eine Analyse von Yuzo Fukuzaki von TechInsights bringt weiteres Licht in die Umsetzung von AMDs 3D V-Cache. Die Packaging-Technik stammt höchstwahrscheinlich von TSMC und nennt sich TSMC-SoIC. Der Fokus liegt vor allem in der Analyse der Fertigung, auf die ersten offiziellen Details des 3D V-Cache sind wir im Rahmen der Präsentation bereits eingegangen.

Für den 3D V-Cache stapelt AMD einen SRAM mit Abmessungen von 6 x 6 mm direkt auf dem L3-Cache des CCDs. Der L3-Cache wird je nach Stacking-Höhe entsprechend erweitert. In der bisher gezeigten Version werden aus den 64 MB L3-Cache eines Ryzen-Prozessors mit zwei CCDs dann insgesamt 192 MB, da 2x 64 MB an zusätzlichem SRAM hinzukommen. Für einen EPYC-Prozessor sind es entsprechend 8x 64 MB zusätzlichem SRAM. Sollten früher oder später SRAM-Stapel mit ein bis vier Stacks zum Einsatz kommen, kann die Kapazität des zusätzlichen Speichers auch verdoppelt, verdreifacht oder gar vervierfacht werden.

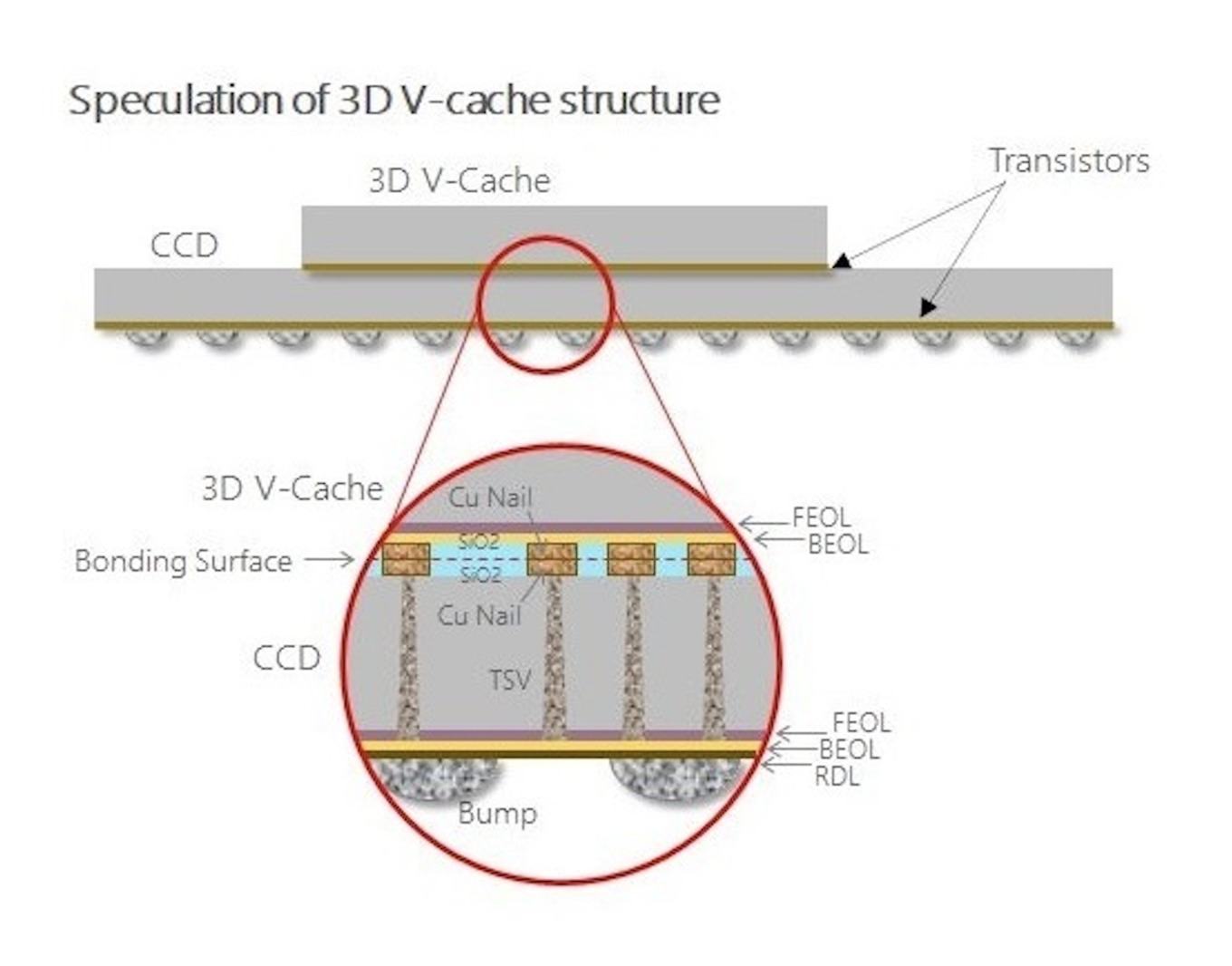

Um den SRAM-Chiplet auf dem CCD anzubringen wird dieser um 95 % auf nur noch 20 µm der ursprünglichen 400 µm angeschliffen. Damit werden die TSV-Kontakte freigelegt, welche die Datenverbindung und Stromversorgung des SRAM ermöglichen. Diese Bearbeitungsschritte finden auf den Ebenen 10 und 11 (M10 und M11) von insgesamt 15 Metallebenen statt. Zählt man die Kontakte auf dem CCD, kommt man hier auf rund 24.000 TSVs, die vom L3-Cache zum SRAM geführt werden.

Interessant an dieser Stelle: Die bisher verwendeten CCDs sehen noch nicht die TSVs selbst vor, sondern nur sogenannte Keep Out Zones (KOZ). Die TSVs werden dann nachträglich aufgebracht. Eine Kupfer-Kupfer-Verbindung der TSVs zu den Kontaktpunkten des SRAM verwendet ausschließlich Adhäsion der Kupfer-Kontaktpunkte, um die beiden Chips miteinander zu verbinden. Ein Verlöten ist nicht notwendig.

Der Abstand zwischen den TSVs (der TSV Pitch) beträgt gerade einmal 17 µm. Zum Vergleich: Der Bump Pitch von Chips, die auf einem Package untergebracht werden sollen, beträgt 80 bis 1xx µm. Intels Packaging-Techniken EMIB (Embedded Multi-die Interconnect Bridge) der ersten und zweiten Generation kommen auf 55 bzw. 45 µm. Für Foveros der ersten Generation, hier können auch Chips aus unterschiedlichen Fertigungsgrößen miteinander verbunden werden, sind es 36 µm. Die Weiterentwicklungen Foveros Omn und Foveros Direct sollen dann einen Abstand von 25 bzw. 10 µm ermöglichen. TSMC läge damit für TSMC-SoIC in der Umsetzung von AMDs 3D V-Cache genau zwischen den beiden neuen Foveros-Varianten.

Zukünftige Prozessoren von AMD, die ein Chiplet-Design und den 3D V-Cache verwenden, zeigen in vielerlei Hinsicht die technische Weiterentwicklung, die AMD in Zusammenarbeit mit TSMC hier gemacht hat. Das Chiplet-Design ermöglicht eine hohe Flexibilität in der Herstellung der Chips und auch deren Verwendung (CCDs mit unterschiedlich vielen aktiven Kernen, unterschiedlicher Güte, etc. pp.). Mit dem 3D V-Cache kann AMD nun den nächsten Schritt gehen und bei Bedarf mehr Cache hinzufügen, was für bestimmte Anwendungen sinnvoll ist. Die Spieleleistung beispielsweise profitiert vom zusätzlichen Cache, wie AMD demonstriert hat. Auch die Serverprozessoren können davon Gebrauch machen und sind sicherlich heiße Kandidaten dafür mit dem 3D V-Cache ausgestattet zu werden. Für das kommende Jahr wird damit gerechnet, dass AMD Prozessoren mit dem 3D V-Cache auf den Markt bringt. Womöglich wird dies noch mit Zen-3-CCDs erfolgen, bevor dann der Wechsel auf Zen 4 erfolgt.