Werbung

Nach vielen Gerüchten und unbestätigten Meldungen dazu hat AMD nun endlich die EPYC-Prozessoren mit 3D V-Cache vorgestellt. Analog zu den Ryzen-Prozessoren wird über dem Bereich des L3-Caches das CCD angeschliffen und eine Lage zusätzlicher SRAM oben aufgelegt, um die Kapazität des L3-Caches zu verdreifachen. Insgesamt stehen dann 768 MB an L3-Cache zur Verfügung.

Die EPYC-Prozessoren mit 3D V-Cache basieren also weiterhin auf der Zen-3-Architektur und hören somit auf den Codenamen Milan-X. Sie bieten weiterhin bis zu 64 Kerne und sind zum Sockel SP3 kompatibel, was den Upgrade-Pfad vereinfacht und die bestehende Infrastruktur begünstigt. Aber kommen wir nun zu den Details:

Je nach Anwendungen ist es besonders wichtig, die zu verarbeitenden Daten möglichst nahe an den Rechenkernen zu haben. Anstatt diese über das Speicherinterface im Arbeitsspeicher abzufragen und wieder abzulegen, sind sie im L3-Cache natürlich deutlich schneller verfügbar. Aktuell bietet AMD EPYC-Prozessoren mit bis zu 256 MB an L3-Cache an und ist dahingehend schon recht gut aufgestellt.

768 anstatt der 256 MB L3-Cache wie bisher werten die Prozessoren im Hinblick auf die Ausstattung natürlich stark auf. Ein weiterer Vorteil dieser Strategie und des offensichtlichen Weitblicks seitens AMD ist, dass die EPYC-Prozessoren mit 3D V-Cache zum aktuellen Sockel SP3 kompatibel sind. Server, die mit den EPYC-Prozessoren der dritten Generation (Milan) laufen, tun dies auch mit den EPYC-Prozessoren mit 3D V-Cache (Milan-X).

Pro CCD, der schon 32 MB an L3-Cache erhält, verbaut AMD nun zusätzlich 64 MB an 3D V-Cache. Jedes CCD mit seinen bis zu acht Kernen verfügt demnach über 96 MB L3-Cache. Bei acht CCDs pro EPYC-Prozessoren kommen wir somit auf 768 MB an L3-Cache. Für die Angabe von 804 MB rechnet AMD wohl noch den L2-Cache hinzu.

Bisher hat AMD nur Ryzen-Prozessoren mit 3D V-Cache auf zwei CCDs gezeigt. Hier ergeben sich daraus 2x 96 = 192 MB an L3-Cache im Verglich zu bisher 64 MB.

Unser Server für den Test der dritten Generation der EPYC-Prozessoren enthielt bereits die entsprechenden Einträge, die allerdings offenlegen, dass AMD bereits an Varianten mit mehr als einem SRAM-Stapel arbeitet. Entsprechend würde sich die Kapazität bei zwei und vier Stacks auf 1.280 und 2.304 MB L3-Cache erhöhen. Ob AMD diesen Schritt allerdings noch für die Zen-3-EPYCs gehen wird, ist eher unwahrscheinlich. Für mehrere Stapel dürften dann aber die Nachfolger alias Genoa (Zen 4) und Turin (Zen 5) in Frage kommen.

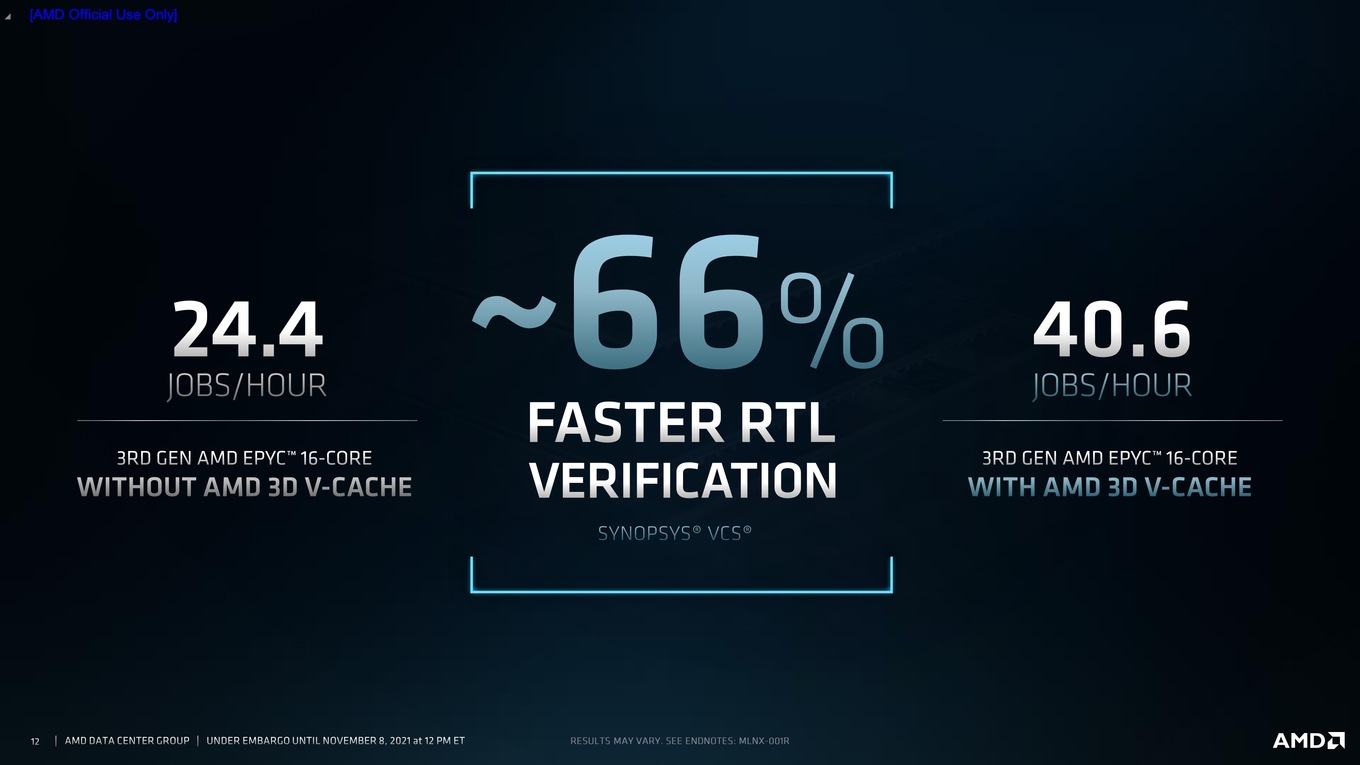

Das Leistungsplus durch den Einsatz des 3D V-Cache ist extrem von der jeweiligen Anwendung abhängig. Für eine Performance-Simulation in Synopsis VCS spricht AMD von einer um 66 % schnelleren Verifikation (24,4 zu 40,6 Jobs pro Stunde). Verglichen wird hier zwischen einem EPYC-Prozessor mit 16 Kernen - einmal mit und einmal ohne (EPYC 73F2) 3D V-Cache.

AMD spricht heute noch nicht über konkrete Modelle und nennt nur bis zu 64 Kerne. Geplant sind Modelle mit 16, 24, 32 und 64 Kernen, wie Leaks bereits offenbart haben. Diese sind dann womöglich ab dem ersten Quartal 2022 verfügbar. Auch zur TDP macht AMD noch keinerlei Angaben. Den Leaks zufolge ändert sich an der maximalen TDP jedoch nichts, was aufgrund der Kompatibilität nicht anders zu erwarten gewesen ist. Die Taktraten könnten allerdings leicht geringer ausfallen.

Die Produktpalette sähe demnach wie folgt aus:

| Kerne | Basis/Boost-Takt | L3-Cache | TDP | |

| EPYC 7773X | 64 | 2,2 / 3,5 GHz | 768 MB | 280 W |

| EPYC 7763 | 64 | 2,45 / 3,5 GHz | 256 MB | 280 W |

| EPYC 7573X | 32 | 2,8 / 3,6 GHz | 768 MB | 280 W |

| EPYC 7543 | 32 | 2,8 / 3,7 GHz | 256 MB | 225 W |

| EPYC 7473X | 24 | 2,8 / 3,7 GHz | 768 MB | 240 W |

| EPYC 7443 | 24 | 2,85 / 4,0 GHz | 128 MB | 200 W |

| EPYC 7373X | 16 | 3,05 / 3,8 GHz | 768 MB | 240 W |

| EPYC 7343 | 16 | 3,5 / 4,0 GHz | 128 MB | 240 W |

*Bisher nicht von AMD offiziell bestätigt

Technische Umsetzung des 3D V-Cache

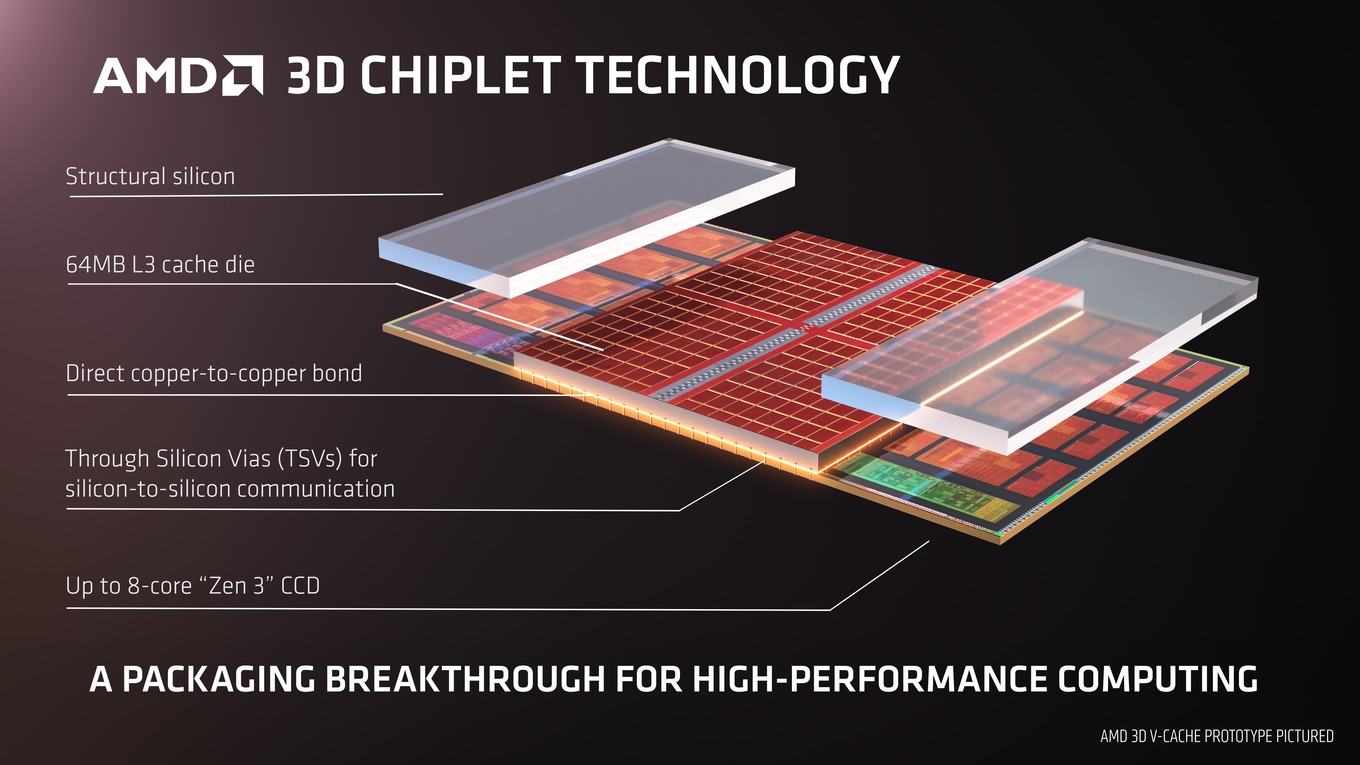

Auf der Computex 2021 Anfang Juni bestätigte AMD erstmals, dass man an Prozessoren mit 3D V-Cache arbeite. Entwickelt hat AMD die Technik gemeinsam mit TSMC, die für AMD die wichtigen CCDs mit den Zen-Rechenkernen und auch die GPUs fertigen. TSMC hat bereits zahlreiche 3D-Packaging-Technologien im Angebot und eben auf dieses Portfolio scheint AMD nun zurückzugreifen.

Der 3D V-Cache ist mittels der 3D-Packaging-Technologie direkt über TSVs (Through-silicon Via) mit dem CCD verbunden. Dazu werden aber zunächst einmal 95 % des CCDs abgeschliffen. Am Ende bleiben nur noch 20 µm des ansonsten 400 µm dicken Chips als aktives Silizium übrig. Auf diese dünne Schicht wird dann der 3D V-Cache gestapelt, der eine Fläche von 36 mm² aufweist. Auf der HotChips-Konferenz verriet AMD einige Details zur Fertigung des 3D V-Cache. Unter anderem liegen die Abstände der TSVs (Through-Silicon Via) für die physikalische Anbindung des SRAM-Dies bei gerade einmal 9 µm.

Um den SRAM-Chip auf dem CCD aufzubringen, reicht die Adhäsion der Kupfer-Kontaktpunkte der TSVs auf beiden Seiten aus, um die beiden Chips miteinander zu verbinden. Die Datenrate dieser Verbindung beträgt mehr als 2 TB/s. Sogenanntes "Structural Silicon" baut den Bereich höher auf, wo sich kein 3D V-Cache befindet, sodass die Bauhöhe des CCDs wieder gleichmäßig ist.

Der 3D V-Cache sitzt also genau über dem Bereich des CCDs, wo sonst auch schon der L3-Cache vorhanden ist. Die Bereiche, in denen sich die Zen-3-Kerne befinden, werden hingegen ausgespart. Dies verhindert, dass der 3D V-Cache die heißen Kerne bedeckt. Das Structural Silicon sorgt für eine Durchkontaktierung der Kerne zum Heatspreader.

Ebenfalls im ersten Quartal 2022 erwartet werden die Ryzen-Prozessoren mit 3D V-Cache. Hierzu hat AMD ebenfalls schon einige Leistungsdaten genannt und spricht von einem durchschnittlichen Leistungsplus von 12 % über alle Anwendungen. Bei Spielen sollen es 15 % sein. Damit wird man auf Intels Alder-Lake-Prozessoren kontern wollen, die vor allem in der Spieleleistung deutlich zugelegt haben.