Werbung

Pünktlich zum Weihnachtsgeschäft will Intel zusammen mit seinen Partnern bei den Premium-Notebooks aufräumen – Gegner sind dabei natürlich Apple und Qualcomm. Lunar Lake wird bereits seit Monaten in den Gerüchten behandelt und viele Details kennen wir bereits. Vor der Computex lud Intel zur dritten Iteration der Intel Tech Tour und hat über die ersten Details zu Lunar Lake gesprochen. Konkrete CPU-Modelle sind zum aktuellen Zeitpunkt noch nicht das Thema, stattdessen wird die neue Efficiency- und Performance-Architektur sowie die Xe2-Architektur für die integrierte GPU vorgestellt.

Natürlich sind auch die noch leistungsfähigere NPU, neue Sicherheitsfunktionen und ein weiter verbessertes Power-Management ein Thema. Allesamt werden wir diese Themenblöcke nun genauer beleuchten.

Lunar Lake ist für Premium-Notebooks vorgesehen. Zur groben Einordnung dessen machte Intel bereits in der vergangenen Woche ein paar Angaben. Die TDP-Spanne wird aller Voraussicht nach von 17 bis 30 W reichen.

Einen genauen Starttermin für Lunar Lake gibt es noch nicht. Intel spricht vom dritten Quartal und dem Weihnachtsgeschäft. Die ersten Produktions-Wafer mit den finalen Chips werden aktuell von TSMC gefertigt, denn für Lunar Lake setzt Intel bei den aktiven Chips ausschließlich auf TSMC als Fertiger. Das Packaging wird wiederum von Intel durchgeführt.

20 Partner will Intel für Lunar Lake bereits gefunden haben, die zu Weihnachten mindestens 80 Geräte am Markt haben wollen. Wahrscheinlich werden wir auf der IFA in Berlin dann die ersten Geräte sehen.

Lion Cove: Neue P-Kerne ohne Hyper-Threading

Die neuen Performance-Kerne basieren auf der Lion-Cove-Architektur. Sie sollen die gleiche Single-Threaded-Leistung wie Redwood Cove bei halber Leistungsaufnahme anzubieten haben. Single-Threaded ist auch gleich ein gutes Stichwort, denn bei diesen Kernen wird Intel auf das Hyper-Threading verzichten. Zugleich aber soll der IPC-Sprung groß sein. Wie groß? Auch dazu haben wir heute bereits eine Antwort.

Aber da die Katze bezüglich des Hyper-Threadings nun aus dem Sack ist, will Intel natürlich auch erläutern, warum man für Lunar Lake auf das Hyper-Threading verzichtet.

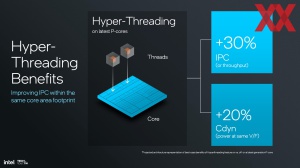

Hyper-Threading wurde für die Xeon-Prozessoren im Februar 2002 und für die Pentium-Prozessoren im November 2002 eingeführt. Über zwei vollständig eigene Register und Pipeline-Stufen ermöglicht das Hyper-Threading die Ausführung von zwei Threads pro Kern, was in Multi-Threaded-Anwendungen die Auslastung des Kerns verbessert und zu einer höheren Rechenleistung sorgt. Durch das Hyper-Threading kann die IPC-Leistung um etwa +30 % gesteigert werden, aber auch die Cdyn (Leistungsaufnahme im gleichen Punkt der V/F-Kurve) steigt um 20 %.

Wird bei einem Redwood-Cove-Kern das Hyper-Threading deaktiviert und vergleicht man dies nun mit Lion Cove, steigen das Leistung/Watt-Verhältnis um 15 % und das Leistung/Area um 10 % an. Leistung/W/Area gehen dementsprechend um 30 % nach oben. Redwood Cove mit Hyper-Threading sieht im Vergleich zu Lion Cove mit +5 % Leistung/Watt gar nicht so schlecht dar. Das Verhältnis aus Leistung pro Fläche ist mit -15 % aber nicht mehr ganz so gut. Die Leistung/W/Area geht aber dennoch um 15 % nach oben.

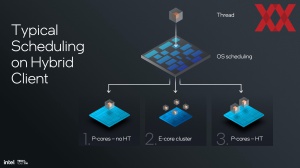

Für die auf Lunar Lake ausgeführten Workloads geht Intel aber davon aus, mit einem auf Single-Threaded-Leistung optimierten Lion-Cove-Design besser dazustehen. Den Nachteil der geringeren Multi-Threaded-Leistung will man in diesem Segment mit den Efficiency-Kernen abfangen.

Lion Cove war von Anfang allerdings mit Hyper-Threading geplant und so wird es in anderen Produkten auch zum Einsatz kommen: Arrow Lake und Xeon-Prozessoren, welche die Lion-Cove-Kerne verwenden sind hier die entsprechenden Kandidaten. Für Lunar Lake hat man die notwendigen Register und Pipeline-Stufen aber weggelassen. Auf RTL-Ebene des Chipdesigns kann dies aber problemlos so ausgelegt werden, dass Lion Cove in anderen Produkten ein Hyper-Threading beherrscht.

Änderungen im Front-End

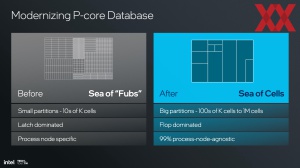

Das Front-End von Lion Cove wird im Vergleich zu Redwood Cove deutlich aufgeweitet. Der Decoder wird von 6- auf 8-Wide aufgeweitet, der µOP-Cache von 8-Wide auf 12-Wide.

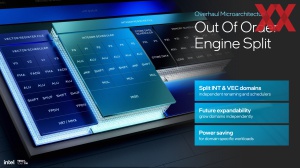

Die OoO-Engine (Out-of-Order) wird in einen Integer- und einem Vektor-Teil aufgespalten. Damit wird man den Veränderungen in den Anforderungen durch die Workloads gerecht. Beide Bereiche haben einen eigenen Scheduler und Register Files.

Die OoO-Engine kann nun Allocate- und Rename-Einheiten acht anstatt sechs Operationen ausführen. Um Ressourcen der Pipeline schneller wieder freigeben zu können, verfügt Lion Cove nun über eine 12-Wide Retire-Einheit – bei Redwood Cove waren es diese 8-Wide. Das Instruction Windows wächst von 512 auf 576 Tiefe. Aus 12 werden insgesamt 18 Ausführungs-Einheiten.

Integer-Einheiten

Im Integer-Segment stehen nun sechs anstatt fünf ALUs zur Verfügung. Die Anzahl der Jump-Units wächst von zwei auf drei, was auch für die Shift-Units gilt. Bei den MUL-Einheiten (Multiply–Accumulate Operation) geht es von eins auf derer gleich drei.

Vektor-Einheiten

Einen Sprung gibt es auch bei den Vektor-Einheiten. Die Anzahl der SIMDs mit jeweils 256 Bits steigt von drei auf derer vier. Aus einem Teiler für Fließkommaberechnungen werden derer zwei, die 256 Bit Operationen ausführen können und im Hinblick auf Latenz und Durchsatz weiter optimiert wurden.

Speicher-Subsystem von Lion Cove

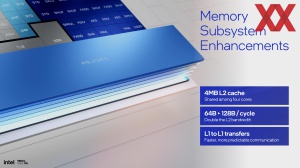

Zu den Verbesserungen gehört auch das Speicher-Subsystem, welches mit Lion Cove verbessert wurde. Mit einem L0-Cache kommt beispielsweise eine Cache-Ebene hinzu. Mit einer Latenz von vier Taktzyklen ist der L0-Cache auch schneller erreichbar, als dies für den L1-Cache in Redwood Cove der Fall ist.

| Load to use | Lese-Bandbreite | Kapazität | |

| Redwood Cove (L1-Cache) | 5 | 3x 256 Bit / 2x 512 Bit | 48 kB |

| Redwood Cove (L2-Cache) | 16 | 2x 64 Bit | 2 MB |

| Lion Cove (L0-Cache) | 4 | 3x 256 Bit / 2x 512 Bit | 48 kB |

| Lion Cove (L1-Cache) | 9 | 2x 64 Bit | 192 kB |

| Lion Cove (L2-Cache) | 17 | 2x 64 Bit | 2,5 / 3 MB |

Dass Lion Cove für mehrere CPU-Designs ausgelegt ist, wird an der daran ersichtlich, dass die Performance-Kerne für Lunar Lake über 2,5 MB L2-Cache verfügen werden, aber auf maximal 3 MB kommen können, was wir dann womöglich bei Arrow Lake sehen werden.

Um das Speicher-Subsystem von Lion Cove besser auslasten zu können hat Intel die Anzahl der Pages des DTLB (Data Translation Lookaside Buffer) von 96 auf 128 erhöht. Bei den AGUs (Address Generation Unit) geht es von zwei auf drei.

All diese Änderungen in der Mikro-Architektur sollen natürlich für eine bessere Leistung sorgen.

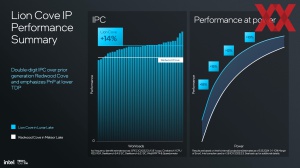

Im Vergleich zu Redwood Cove liegt das IPC-Plus im Mittel bei 14 %. Über verschiedene Bereich der Leistungskurve kann Intel zwischen 18 und 10 % einhalten.

Skymont: Neue E-Kerne mit deutlichem IPC-Zuwachs

Waren die Efficiency-Kerne bisher meist nur Beiwerk waren, ist ihnen in den vergangenen Jahren eine deutlich größere Rolle zugeteilt worden. Sie sind nicht mehr nur die sparsamen Kerne für mobile Systeme, sondern seit Alder Lake Bestandteil eines Hybrid-Performance-Designs. Mit Meteor Lake führte Intel die Low-Power-E-Kerne ein, eine dritte Ebene an Kernen, die besonders sparsam sein sollen und sich um die Hintergrundaufgaben kümmern.

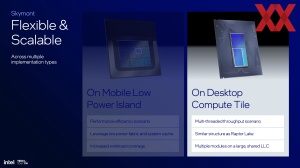

Mit Lunar Lake geht man nun wieder einen Schritt zurück. Die P-Kerne haben wir besprochen, zu diesen gesellen sich vier weitere E-Kerne, die Intel als Low-Power-Island bezeichnet, die aber auch Bestandteil des Compute-Tiles sind.

Die neuen Skymont-Kerne wurden komplett überarbeitet. Sie sollen einerseits die Multi-Threaded-Leistung des SoCs unterstützen, übernehmen dabei aber eine deutlich größere Rolle in der Gesamtleistung des Chips. Die Mikroarchitektur wird deutlich breiter und schneller.

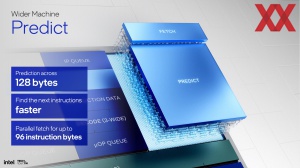

Front-End

Genau wie bei Lion Cove wird die Sprungvorhersage von 64 auf 128 Byte erweitert. In so manchen Crestmont-Designs waren sogar nur 32 Byte möglich. Damit ist es möglich, dass die nächste Instruktion schneller gefunden wird. Die Decoder-Engine wird 9-Wide und besitzt mit ihrer 3x3-Konfiguration 50 % mehr Decoder-Engines als dies mit Crestmont und der 2x3-Konfiguration der Fall war.

Zum Front-End gehört auch die µOPQueue, die von 64 auf 96 Einträge erweitert wird. Eine Instruktion besteht aus mehreren µOPs. Vom ROM konnte bei Crestmont aber immer nur von einem Decode-Cluster gelesen werden, was nun bei Skymont parallel möglich ist.

Back-End

Die Out-of-Order-Engine ist nun ebenfalls breiter und kann acht statt sechs Allocate- oder Rename-Operationen durchführen. Um die Ausführung der nächsten Instruktionen zur beschleunigen, wird die Retire-Einheit von acht auf 16 verbreitert, was auch die Latenzen und die Anzahl der Taktzyklen bis zur Ausführung der nächsten Instruktion beschleunigt. Um dies alles zu unterstützen werden die dazugehörigen Register ebenfalls größer.

Integer-Leistung

Um die Integer-Leistung zu steigern bietet Skymont nun 8-Wide statt nur eine 6-Wide breite Allocate- und Rename-Einheiten. Die OoO-Engine (Out of Order) ist nun doppelt so breit aufgestellt – von 8 auf 16-Wide und die Anzahl der Execution Ports wird von 12 auf 18 erhöht.

Vektor-Leistung

Im Vergleich zu Crestmont werden die Vektor-Einheiten bei Skymont verdoppelt. Es sind nun vier 128 Bit FP & SIMD Vektor-Einheiten vorhanden. Zudem gibt es hier dedizierte Hardware für die Rundung von Fließkomma-Zahlen. Neben der Verdopplung der Vektor-Leistung geht mittels VNNI über AVX2 auch die KI-Leistung der Skymont-Kerne deutlich nach oben.

Schaut man sich nun noch die Load/Store-Einheiten an, die unter anderem dem Data-Cache zuarbeiten, so kann Skymont nun drei anstatt zwei Loads pro Taktzyklus ausführen. Die Anzahl der Store-Engines geht ausgehend von zwei bei Crestmont hoch auf nun vier bei Skymont. Der geteilte L2-Cache TLB bekommt nun 4.192 anstatt wie bisher 3.096 Einträge spendiert.

Ein weiterer Punkt in der Leistung und Effizienz von Skymont sind die L1-zu-L1-Cache-Transfers der Kerne untereinander, die nun auf direktem Wege ausgeführt werden und nicht mehr über den Fabric und den L2-Cache gehen müssen.

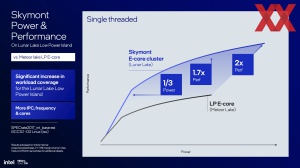

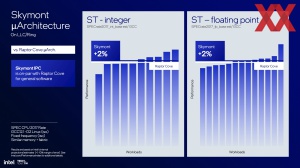

Kann Lion Cove mit einem IPC-Plus von 14 % schon überzeugen, ist das, was Skymont anzubieten hat, für viele sicherlich überaschend. Für Integer-Anwendungen liegt das IPC-Plus bei 38 %, durch die Verdopplung der Vektor-Einheiten für Fließkomma-Anwendungen sogar bei 68 %. Es dürfte sich hierbei um das größte IPC-Plus handeln, welches wir in den vergangenen Jahren gesehen haben.

Im Vergleich zu den Low-Power E-Kernen sind die neuen E-Kerne in Lunar Lake im idealen Leistungsfenster betrieben um den Faktor 2,9 schneller und haben dabei nur rund ein Drittel der Leistungsaufnahme. Ehrlicherweise muss man dazu aber sagen, dass Intel hier die zwei LP E-Kerne gegen die vier neuen Skymont-Kerne vergleicht.

Letztendlich bieten Skymont und damit die E-Kernen die gleiche IPC-Leistung (+2 %) wie Raptor Cove, wenngleich es hierbei um einen Mittelwert handelt und einige Anwendungen teils deutlich langsamer sind.

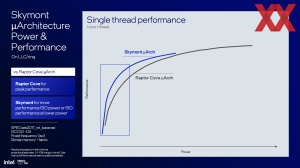

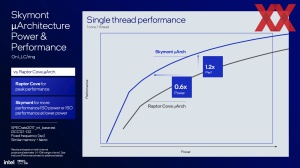

Vergleicht man die Single-Threaded-Leistung zwischen Skymont und Raptor Cove, so können die E-Kerne in einem gewissen Betriebsfenster um 20 % schneller sein und haben dabei eine um 40 % niedrigere Leistungsaufnahme vorzuweisen.