Werbung

Für das Team hinter Lunar Lake war von Anfang an klar, dass die Fertigung bei TSMC stattfinden wird. Es handelt sich also um eine bewusste Entscheidung, die auf Basis der eigenen Anforderungen an Lunar Lake gefällt wurde. Natürlich ist dies für Intel als Unternehmen, welches über Jahrezehnte mit seinen Qualitäten aus Chiphersteller geglänzt hat, keine Aushängeschild, wenn man nun für derartige Flaggschiff-Produkte auf eine externe Fertigung zurückgreifen muss.

Aber Intel geht diese Phase nun pragmatisch an und es ist auch nicht neu, dass ganze Chips bei TSMC gefertigt werden. Für Lunar Lake kommen drei der fünf Chiplets von TSMC. Auch zukünftige Chips werden teilweise noch auf TSMC setzen. Intel wird die Zusammenarbeit also noch einige Zeit fortsetzen. Natürlich aber wird es das Ziel sein wieder möglichst vollständig auf eine eigene Fertigung vertrauen zu können.

Der Compute-Tile mit den P- und E-Kernen sowie der GPU, NPU, dem Side Cache und vielem mehr wird in TSMC N3B gefertigt. Dabei handelt es sich um den gleichen Prozess, in dem auch der M3 von Apple gefertigt wurde. Allerdings sind Apple und Intel wohl die einzigen größeren Kunden, die N3B nutzen werden. N3B konnte die Erwartungen von TSMC nicht erfüllen und so wurde ein schneller Wechsel auf N3E vollzogen, den Apple mit dem M4 bereits hinter sich gebracht hat.

Der Platform-Controller-Tile wird in TSMC N6 gefertigt. Darauf befinden sich vor allem die I/O-Funktionen wie Wi-Fi, Bluetooth, USB, Thunderbolt sowie die PCI-Express-Controller. Aber auch die Partner Security Engine, Silicon Security Engine sowie die Management Engine sind hier zu finden.

Der Compute- und der Platform-Controller-Tile sitzen auf einem Base-Tile, der in Intel 22FFL (P1227.1) gefertigt wird. Erstmals bringt Intel Foveros mit einem Bumb-Pitch von 25 µm zum Einsatz. Für Meteor Lake verwendete Intel noch einen Abstand von 36 µm zwischen den Kontakten. Zudem gab es hier anfangs noch ein paar Probleme in der Fertigung, die inzwischen aber beseitigt sind. Für Lunar Lake mit Foveros-Bumb-Pitch von 25 µm sollen diese nicht mehr vorhanden sein.

Schaut man sich das Package noch etwas genauer an, dann fällt noch ein dritter kleiner Tile in der Ecke auf. Dabei handelt es sich um einen Filler, der notwendig ist, um die Signalintegrität gewährleisten zu können.

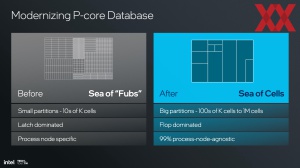

Um Lion Cove agnostisch zur Fertigung zu gestalten, hat Intel im Design der Mikroarchitektur einige Design-Richtlinien erneuert. Das P-Kern-Design ist nicht mehr in mehreren hundert sogenannte "Fubs" (Functional Blocks) aufgeteilt, sondern besteht un aus weniger Zellen, die dafür deutlich größer sind und mehr Design-Elemente und letztendlich auch Transistoren enthalten.

Mit der neuen Auslegung einher geht auch, dass Intel nicht mehr ausschließlich auf eigene EDA-Werkzeuge setzt, sondern Standardsoftware in diesem Bereich, was natürlich auch die Zusammenarbeit mit TSMC vereinfacht.

Am Ende aber macht es die Mikroarchitektur eben unabhängig vom jeweiligen Fertiger und es bedeutet auch, dass wir Lion Cove in unterschiedlichen Ausprägungen sehen werden und Intel auf einen Werkzeugkasten zurückgreifen kann, um Lion Cove an die jeweiligen Anforderungen anzupassen.

Scalable Fabric 2 und D2D-Interface

Um alle IP-Blöcke im Compute-Tile zu verbinden, setzt Intel auf den Scalable Fabric 2. Dieser verbindet die P- und E-Kerne, sowie den Memory Side Cache, die NPU und GPU miteinander. Auf den Side Cache haben die P- und E-Kerne sowie die NPU entsprechend Zugriff. Theoretisch ist dies auch für die GPU der Fall, nur genutzt wird dieser Cache von der GPU nicht.

Über das Die-2-Die-Interface sowie den Scalable Fabric 2 werden die Daten auch zwischen dem Platform-Controller-Tile und dem Compute-Tile ausgetauscht bzw. die IP-Blöcke haben untereinander Zugriff auf den kohärenten Speicher.

Dieser Datenzugriff bzw. die entsprechende Anbindung ermöglicht eine schnelle Anbindung der I/O-Ports. Von diesen vorhanden sind:

- Wi-Fi 7

- Bluetooth 5.4

- 4x PCIe 5

- 4x PCIe 4

- 3x Thunderbolt

- 2x USB 3.0

- 6x USB 2.0

Ein Dual-Channel-Speicherinterface für LPDDR5X

Der Speichercontroller sitzt am Compute-Tile. Für Lunar Lake-MX sieht Intel vor, dass sich der LPDDR5X-Speicher direkt mit auf dem Package befindet. Dies reduziert einerseits die Leistungsaufnahme, da die PHYs weniger Leistung benötigt, durch die geringeren Latenzen und den geringen Abstand kann aber auch schnellerer Speicher eingesetzt werden. Zudem können die Notebook-Hersteller die PCBs entsprechend kleiner gestalten, da sie keine Fläche für den Arbeitsspeicher vorsehen müssen.

Intel sieht LPDDR5X-8500 mit 32 GB in zwei Chips in der maximalen Konfiguration vor. Die Notebook-Hersteller können aber auch auf langsameren Speicher setzen, was wir bei einigen Herstellern auch schon gesehen haben.

Genau wie bei Meteor Lake kommt ein 128 Bit breites Speicherinterface zum Einsatz, welches sich aus zweimal 4x 16 Bit zusammensetzt. Aus 128 Bit x 8.500 MT/s / 8 Bit ergibt sich eine Speicherbandbreite von 136 GB/s. Bei Meteor Lake waren es noch 119,5 GB/s (128 Bit x 7.467 MT/s / 8 Bit) und auch viele anderen mobile Chips wie der Snapdragon X Elite kommen auf 135 GB/s. Beim M3 Pro sind es 150 GB/s.

Zunächst veröffentlichte und bestätige Intel auf Nachfrage ein nur 64 Bit breites Speicherinterface. Dies hätte sich alles andere als positiv auf die Leistung des gesamten SoCs, vor allem aber die der GPU ausgewirkt.

Notebooks im dritten Quartal

Zur Computex 2024 stellt Intel Lunar Lake als Plattform vor, nennt aber noch keine konkreten Modelle mit den dazugehörigen Taktraten, der Anzahl der Kerne oder Leistungsaufnahme. Die dazugehörigen Notebooks sollen im dritten Quartal auf den Markt kommen. Wir konnten uns aber schon erste Modelle von ASUS und Acer anschauen. Dazu haben wir aber eine gesonderte News gemacht. Dieser Artikel hier soll schon einmal die theoretische Basis dessen Bilden, was dann ab Spätsommer oder Herbst im Handel sein wird.

Die P- und E-Kerne, vor allem die sparsamen E-Kerne auf Basis von Skymont sind auf dem Papier sehr überzeugend. Ob das Gesamtkonzept aufgehen wird, wird sich zeigen müssen. Die Gegner stehen ebenfalls bereits in den Startlöchern: AMDs Ryzen-Serie mit Zen 5, Qualcomms Snapdragon X Elite und Apples M4 werden allesamt ebenfalls ab spätestens Herbst die Konkurrenz für Lunar Lake sein und daran wird man sich bei Intel messen lassen müssen.