Werbung

Zusammen mit dem Ryzen 7 9800X3D (Test) führte AMD die zweite Generation der 3D-V-Cache-Technologie ein und in dieser gab es einige entscheidende Änderungen im Aufbau, die letztendlich dazu geführt haben, dass der Ryzen 7 9800X3D höhere Taktraten halten kann und weniger kritisch auf hohe Lasten und Temperaturen reagiert.

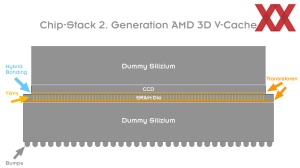

Mit der zweiten Generation der 3D-V-Cache-Technologie platziert AMD den SRAM-Chip unter dem CCD. Soweit so gut, denn zwei Chips einfach nur zu tauschen klingt auf den ersten Blick recht einfach. Aber es gibt einige Änderungen im Aufbau. So war der SRAM-Chip bisher deutlich kleiner als der CCD und an den Seiten waren Filler-Chips aufgebracht. Da der SRAM-Chip nun unter dem CCD sitzt, ist dieser sogar etwas größer als der CCD.

Tom Wassick analysiert beruflich den Aufbau solcher Chips. Seiner ersten Analyse zufolge ist der SRAM-Chip um etwa 50 µm auf allen Seiten größer als der CCD. In der Fertigung werden der SRAM-Chip und CCD auf unter 10 µm abgeschliffen, nachdem die notwendigen Strukturen auf dem Wafer hergestellt wurden. Damit werden auch die notwendigen Strukturen in Form der TSVs freigelegt, die dann per Hybrid-Bonding miteinander verbunden werden. Darunter versteht man, dass die TSVs des CCDs und Kontaktpunkte des SRAM-Chips korrekt zueinander positioniert werden und dann die Adhäsion des Kupfers ausreicht, um die Verbindung beizubehalten. Ein Verlöten ist nicht notwendig.

Der Abstand zwischen den TSVs beträgt etwa 15 µm, was nur geringfügig weniger wäre, als bei der bisherigen Umsetzung des 3D V-Cache mit 17 µm.

* Das Schaubild soll den Aufbau in etwa veranschaulichen und darlegen, wo sich der SRAM-Chip, CCD und das Dummy-Silizium in etwa befindet

Die zwei extrem dünnen Chips mit jeweils weniger als 10 µm wären natürlich viel zu empfindlich, darum bringt AMD auf beiden Seiten ein Dummy-Silizium auf. Hinzu kommt noch das BEOL (Back-end of Line) mit den notwendigen Metallschichten zur Aufbringung auf dem Package-Substrat. Der Stack aus dem SRAM-Chip und CCD kommt inklusive des BEOL auf eine Dicke von etwa 40 bis 45 µm. Insgesamt ist der Stack auf dem Package-Substrat etwa 800 µm dick, sodass 750 µm Dummy-Silizium sind. Zwischen 500 und 800 µm sind die typischen Größen, die von AMD und Intel für die Dicke des eigentlichen Chips anvisiert werden.

Zwischen den SRAM, CCD und dem Dummy-Silizium gibt es jeweils eine Oxidschicht, welche die verschiedenen Schichten aneinander bindet. Diese Oxidschichten sind für den Wärmeübergang besonders kritisch und sollten in Anzahl und Dicke so gering wie möglich gehalten werden. Die Bindeschicht zwischen dem Dummy-Silizium und den Chips ist wohl schon etwas dünner, als dies zwischen dem SRAM-Chip und dem CCD der Fall ist. Dies dürfte eine der Optimierungsmaßnahmen für einen möglichst idealen Wärmeübergang zwischen den Schichten sein.

Wassick wird nun noch Untersuchungen mit einem Rasterelektronenmikroskop anstellen, was weitere Erkenntnisse über den Aufbau der Chips erbringen soll. So wäre es interessant zu wissen, in welchen Bereich des SRAM-Chip sich die Speicherblöcke für die insgesamt 64 MB an zusätzlichem Cache befinden und wo die Durchleitungen vom Package-Substrat zum Chip ausgeführt sind.

Die Zusammenarbeit von AMD und TSMC für die 3D-V-Cache-Technologie verwendet in weiten Teilen Halbleiter- bzw. Packaging-Ressourcen von TSMC. Für ein Produkt wie den CCD mit 3D V-Cache geht eine solche Zusammenarbeit über weit über das Hinaus, was sonst bei einer Auftragsfertigung zu erwarten ist.

Im Januar dürften die weiteren X3D-Modelle mit Zen-5-Kernen erscheinen. Dabei handelt es sich um den Ryzen 9 9950X3D mit 16 Kernen und den Ryzen 9 9900X3D mit 12 Kernen. Ob sich die Liefersituation um den Ryzen 7 9800X3D bis dahin etwas entspannt hat oder gerade wegen der weiteren Modelle weiterhin angespannt bleibt, bleibt abzuwarten.

Update:

Tom Wassick schiebt noch einige Details nach, die offenbar nach der Untersuchung mittels Rasterelektronenmikroskopie entstanden sind:

Demnach ist der SRAM-Chip nur 6 µm dick, während der CCD auf 7,2 µm kommt. Zudem kommt der SRAM-Chip auf 14 Metalllagen und beim CCD sind es derer 18. Bei den TSVs scheinen AMD und TSMC das aktuell Mögliche der SoIC-Technologie auszuschöpfen und kommen auf einen minmalen TSV-Abstand von 10 µm. Bisher lag man hier im Bereich von 15 µm.

Datenschutzhinweis für Twitter

An dieser Stelle möchten wir Ihnen einen Twitter Feed zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Twitter setzt durch das Einbinden des Applets Cookies auf ihrem Rechner, mit welchen sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf diesen Feed. Der Inhalt wird anschließend geladen und Ihnen angezeigt.Ihr Hardwareluxx-Team

Tweets ab jetzt direkt anzeigen