Werbung

Im Rahmen eines "Intel Accelerated" getauften Webcasts hat Intel am Abend über seine Pläne bei den Prozess- und Packaging-Roadmaps gesprochen. CEO Pat Gelsinger und Dr. Ann Kelleher, SVP und GM des Technology Development, haben noch einmal die grundsätzliche Neuausrichtung der IDM-2.0-Strategie aufgezeigt. Demnach wird Intel einerseits weiterhin (und eventuell auch im größeren Maßstab) die externe Fertigung von TSMC, Samsung und GlobalFoundies nutzen. Intel will aber wieder Technologieführer in der Halbleiterfertigung werden – sowohl für die eigenen Produkte, als auch im Angebot der externen Fertigung.

14nm, 14nm+, 14nm++, 14nm+++, eine nie problemlose Fertigung in 10nm, ein eingestelltes 10nm+ – dann wurde es Intel in der Außenkommunikation offenbar zu wild und man wechselte auf 10nm SuperFin. Alter Wein in neuen Schläuchen könnte man auch sagen, denn am Ende schraubte Intel so lange an der Fertigung, bis man daraus endlich funktionsfähige Produkte fertigen konnte. Offenbar wollte man auf den Einsatz der teuren Belichtung mittels EUV größtenteils verzichten und neben andern Fehlentscheidungen wurde dies dann zum "10 nm Debakel" bei Intel. Tiger Lake erreichte in 10nm SuperFin dann final das zu erwartende Niveau in der Fertigung, sowohl hinsichtlich der Ausbeute, als auch in der Leistung der Transistoren. Für den Desktop kam diese Rettungsaktion jedoch zu spät, denn bis zur aktuellen Rocket-Lake-Generation setzt Intel auf dem Desktop weiterhin auf 14 nm, während die Xeon-Prozessoren nun mit Ice Lake-SP zumindest den Weg auf die Fertigung in 10 nm (10nm SuperFin) gefunden haben.

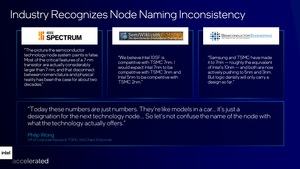

Mit Enhanced 10nm SuperFin wird nun der nächste Schritt gemacht und zugleich wird dies der letzte für die aktuelle Namensgebung sein. Die Nanometer-Angaben waren schon seit Jahren nur noch ein Marketing-Instrument. Mit tatsächlichen Größen im Chip hatten diese Angaben schon lange nichts mehr zu tun. Zugleich drifteten die Angaben der weiteren Hersteller auseinander. Das, was TSMC und Samsung in 7 nm erreicht, schafft Intel hinsichtlich der Packdichte in 10 nm. So wirklich vergleichbar waren und sind die Angaben der verschiedenen Halbleiterhersteller also weiterhin nicht.

Neue Namensgebung in der Fertigung

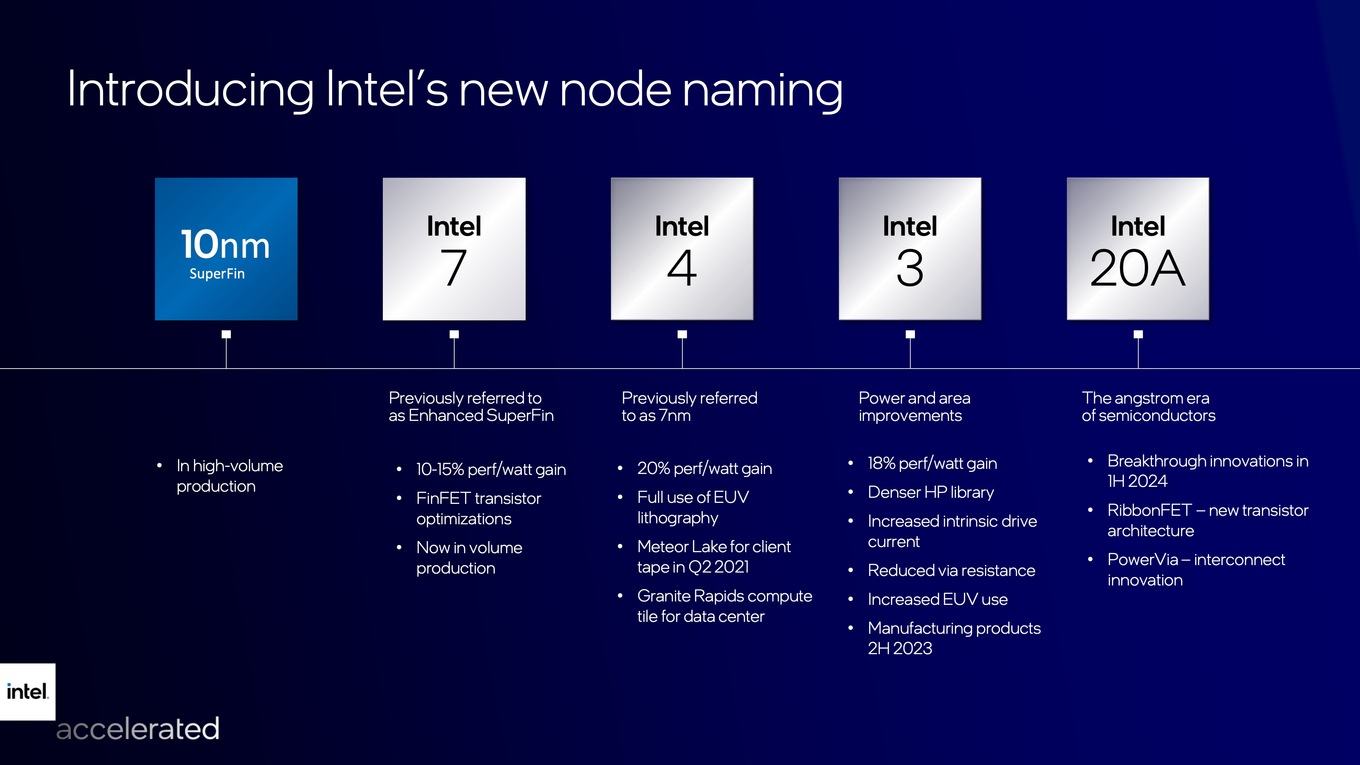

Intel hat sich dazu entschieden, das Namensschema zu erneuern. Aus Enhanced 10nm SuperFin wird nun Intel 7. Dies geschieht wohl deswegen, um dem eben erwähnten Umstand Rechnung zu tragen. Darauf folgen werden Intel 4, Intel 3, Intel 20A und Intel 18A. Was es nicht mehr geben soll, sind die sogenannten Intranodes, also die kleineren Verbesserungen in einem Fertigungsschritt. Diese kleineren Schritte waren zuletzt bei Intel durchaus signifikant. Im Rahmen der Vorstellung von 10nm SuperFin sagte Intel, dass die Fertigung in 14 nm ausgehend von Broadwell über Skylake, Kaby Lake, Coffee Lake und Cooper Lake um 5,5, 3,8, 5,8 und 5,9 % (insgesamt 21 %) leistungsstärkere Prozessoren ermöglicht habe. Mit Rocket Lake hat man die Fertigung in 14 nm auf die Spitze getrieben – auch hinsichtlich der Leistungsaufnahme.

Nun aber will Intel auf einen schnelleren und effizienteren Rhythmus in der Fertigung wechseln und dieser soll wie folgt aussehen:

| Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A | |

| bisherige Namensgebung | Enhanced 10nm SuperFin | 7 nm | 5 nm | - | - |

| Perf/Watt | +10-15 % | +20 % | +18 % | - | - |

| Produktionsstart | Q2 2021 | 2H 2022 | 2H 2023 | 1H 2024 | 2025 |

| Markteinführung erster Chips | Q3/Q4 2021 | 2023 | - | - | - |

Die Einheit Nanometer taucht demzufolge nicht mehr auf. Das, was bisher als eine Fertigung in 7 nm beschrieben wurde, wird zu Intel 4. Darauf folgt Intel 3 und alles, das danach kommt, befindet sich schon in der Ångström-Ära, wie Intel sie bezeichnet.

Bisher hat Intel noch nicht viel zu dem Verbesserungen für Enhanced 10nm SuperFin nun Intel 7 verraten. Die FinFETs sollen aber noch einmal überarbeitet worden sein. Dazu gehören eine erhöhte Dehnungen im Design, die Verwendung niederohmigerer Materialien, neuartige High-Density-Strukturierungstechniken, und ein besseres Routing mit einem höheren Metal Stack. Für Intel 7 will Intel das Verhältnis aus Leistung pro Watt um 10 bis 15 % erhöhen. Alder Lake für den Desktop und mobilen Markt sowie die Xeon-Prozessoren alias Sapphire Rapids werden in Intel 7 gefertigt werden. Die Massenproduktion soll bereits angelaufen sein. Im dritten oder vierten Quartal wird die Einführung dieser erwartet, während die nächste Xeon-Generation mit HBM nun erst Anfang 2022 erwartet wird. Zumindest für Sapphire Rapids soll auch EMIB 1.0 zum Einsatz kommen. Über die Interconnect-Technologie werden die vier Dies miteinander verbunden. Der Bump-Abstand von nur 55 µm soll dafür sorgen, dass sich diese bis zu vier Dies wie ein einzelner Chip verhalten. Dazu aber später noch mehr.

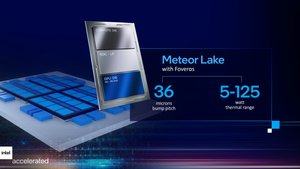

Intel 4 wird Intels bisher als 7 nm bezeichnete Fertigung. Diese wird für Meteor Lake und Granite Rapids (zumindest für den Compute Tile) zum Einsatz kommen. Das Ziel ist eine um 20 % gesteigerte Effizienz. Der Produktionsstart wird im zweiten Halbjahr 2022 erwartet, erste Produkte sollen allerdings nicht vor 2023 zu erwarten sein. Für Intel 4 setzt der Halbleiterhersteller auf mehr EUV-Fertigung (in mehr Layern), als dies für Intel 7 der Fall ist. Die schematischen Darstellungen von Meteor Lake zeigt die Desktop-Version mit einem Compute Tile, einem SoC-Tile und einem GPU-Die mit 96 bis 192 EUs. Die TDP von Meteor Lake wird wie bei Alder Lake bei 5 bis 125 W liegen und damit wird Intel mit diesem Design sowohl die sparsamen Notebooks, als auch den Desktop abdecken.

Noch relativ konkrete Zahlen gibt es zu Intel 3. Das Verhältnis aus Leistung pro Watt soll um 18 % steigen. Intel will hier ein höheres Niveau an Verbesserungen der Transistorleistung umsetzen, als dies typischerweise von einem Full-Node-Sprung zu erwarten wäre. Für Intel 3 spricht Intel außerdem von einer höheren Packdichte der High-Performance-Bibliotheken im Chip-Design und von einem optimierten Metal Stack für den Inteconnect-Bereich. Die Nutzung der EUV-Belichtung für mehr Layer wird weiter erhöht. Die Fertigung erster Chips in Intel 3 soll im zweiten Halbjahr 2023 erfolgen.

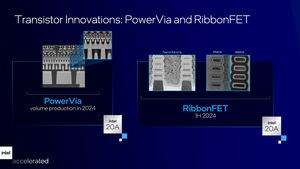

Danach beginnt für Intel die Ångström-Ära. Ein Ångström entspricht dem zehnmillionsten Teil eines Millimeters. Ein Ångström entspricht in etwa 0,1 nm. Das, was Intel als Intel 20A bezeichnet, könnte also bisher als eine Fertigung in 2 nm aufgeführt werden. Leistungsdaten nennt man hier nicht mehr, dafür mit den RibbonFET und PowerVia zwei neue Technologien, auf die wir noch eingehen werden. Für das erste Halbjahr 2024 plant Intel mit der Fertigung in Intel 20A. 2025 soll dann Intel 18A folgen. Intel plant hier den Einsatz der sogenannten High-NA (Numerical Aperture) EUV-Tools und ASML soll erste Geräte an Intel liefern.

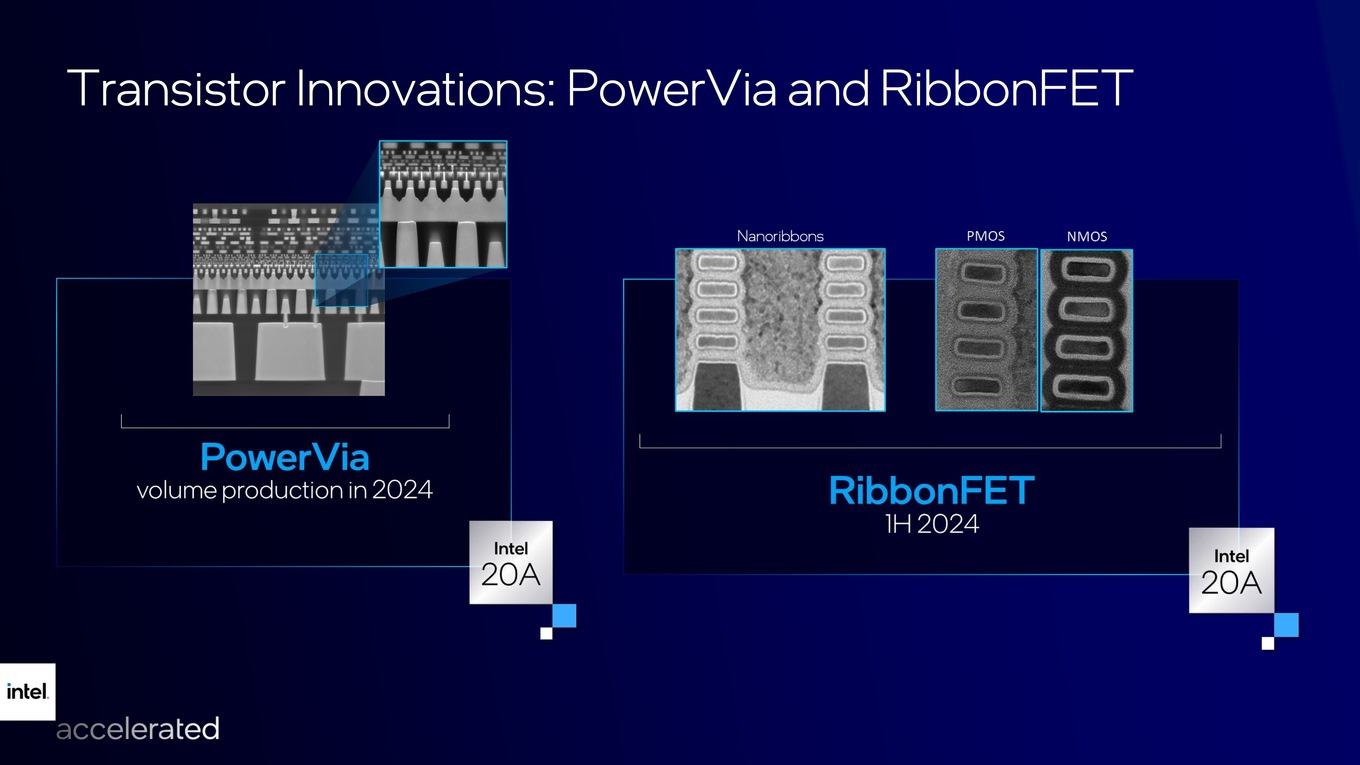

RibbonFET und PowerVia für die Ångström-Ära

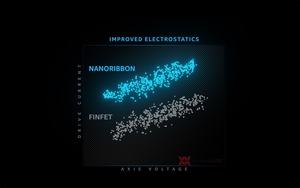

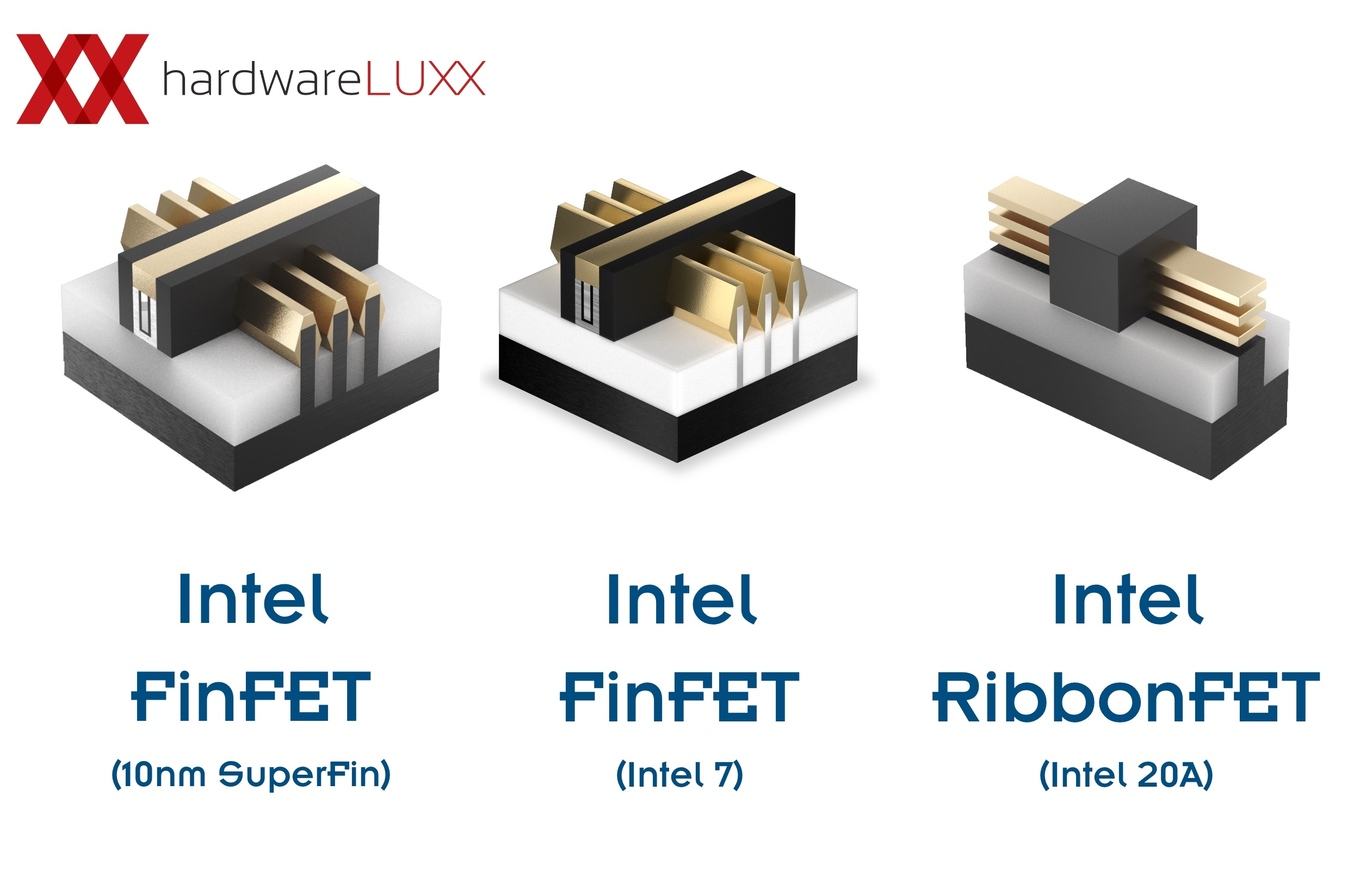

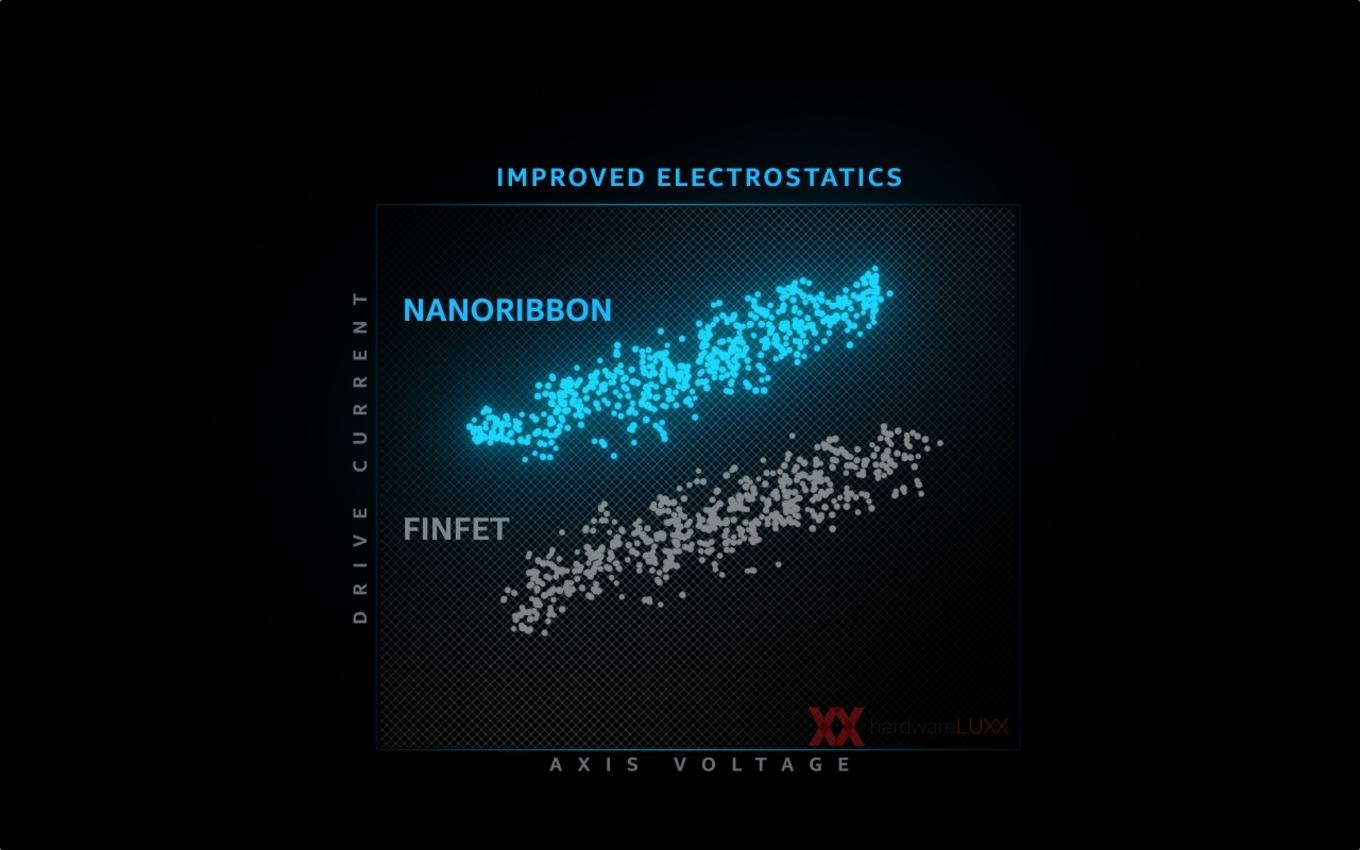

Intel hat für die Gate-All-Around-Transistoren (GAA) endlich einen Namen gefunden. Diese werden als RibbonFET und sollen die aktuell verwendeten FinFETs (Feldeffekttransistoren) ablösen. Die Multi Bridge Channel FETs (MBCFET) können in unterschiedlichen Strukturen ausgeführt werden. Bei Intel werden es Bänder sein, die um die Kanäle des Transistors gelegt werden. Allgemein sind GAA-Transistoren also weiterhin Feldeffekttransistoren (FET), deren Gates auf allen vier Seiten um ultradünne Kanäle gewickelt sind. Diese verbesserte Gate-Steuerung des Kanals überwindet die physikalischen Skalierungs- und Leistungsbeschränkungen von FinFETs und ermöglicht eine weitere Skalierung der Versorgungsspannung. Zudem haben GAA-Transistoren den Vorteil, dass sie in einer anderen Ausrichtung gefertigt werden können und einen echten 3D-Stapel bilden. Ein RibbonFET kann den gleichen Strom schalten, wie dies mehrere FinFETs aktuell tun und das auf einer kleineren Fläche. Über die breite der Gates, die in der Fertigung variable ist, können die RibbonFETs in den Eigenschaften angepasst werden.

Samsung will die Fertigung in 3 nm mit MBCFETs in allen Bereichen der Auftragsfertigung anbieten. Bereits 2022 soll es losgehen. Intel wäre damit zwei Jahre später dran.

PowerVia stellt eine neue Technik in der Stromversorgung eines Chips dar. Bisher werden die Leiterbahnen und Kanäle im Silizium von der gleichen Seite ausgeführt, wie das für die eigentlichen Logikelemente, spricht Transistoren, der Fall ist. Dies kann aber zu Problemen führen, da es zu Interferenzen zwischen mehreren, stromführenden Elementen und den Logikbauteilen bzw. den Metallschichten für die Kommunikation mit den Transistoren kommen. Die Komplexität ist innerhalb eines Chips mit mehreren Milliarden Transistoren ohnehin schon nicht unerheblich. Mit PowerVia wird nun die Rückseite des Wafers verwendet. Während auf der einen Seite weiterhin die Logikelemente und Interconnects belichtet werden, soll die Stromversorgung nun von der anderen Seite erfolgen. Die für PowerVia verwendeten TSVs sollen 500mal kleiner sein, als das was heutzutage für die TSVs im Packaging möglich ist.

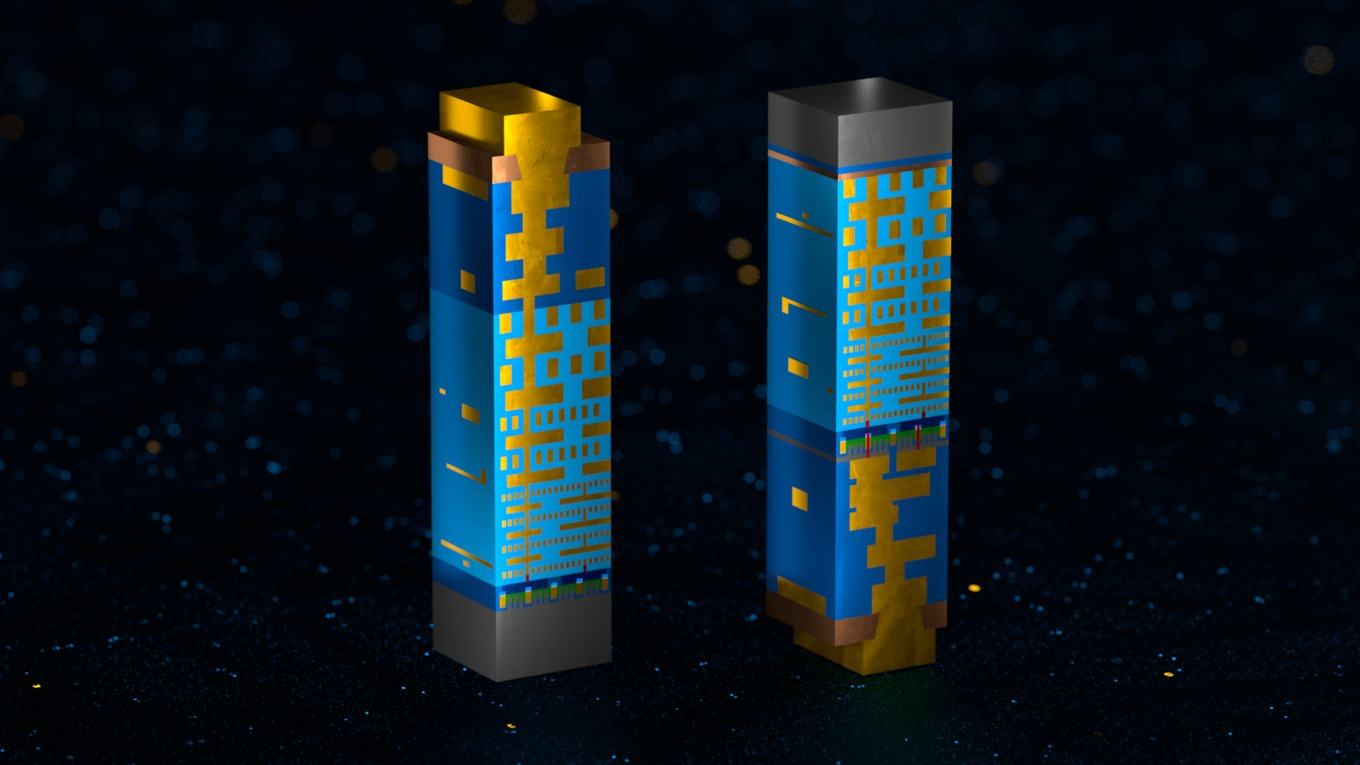

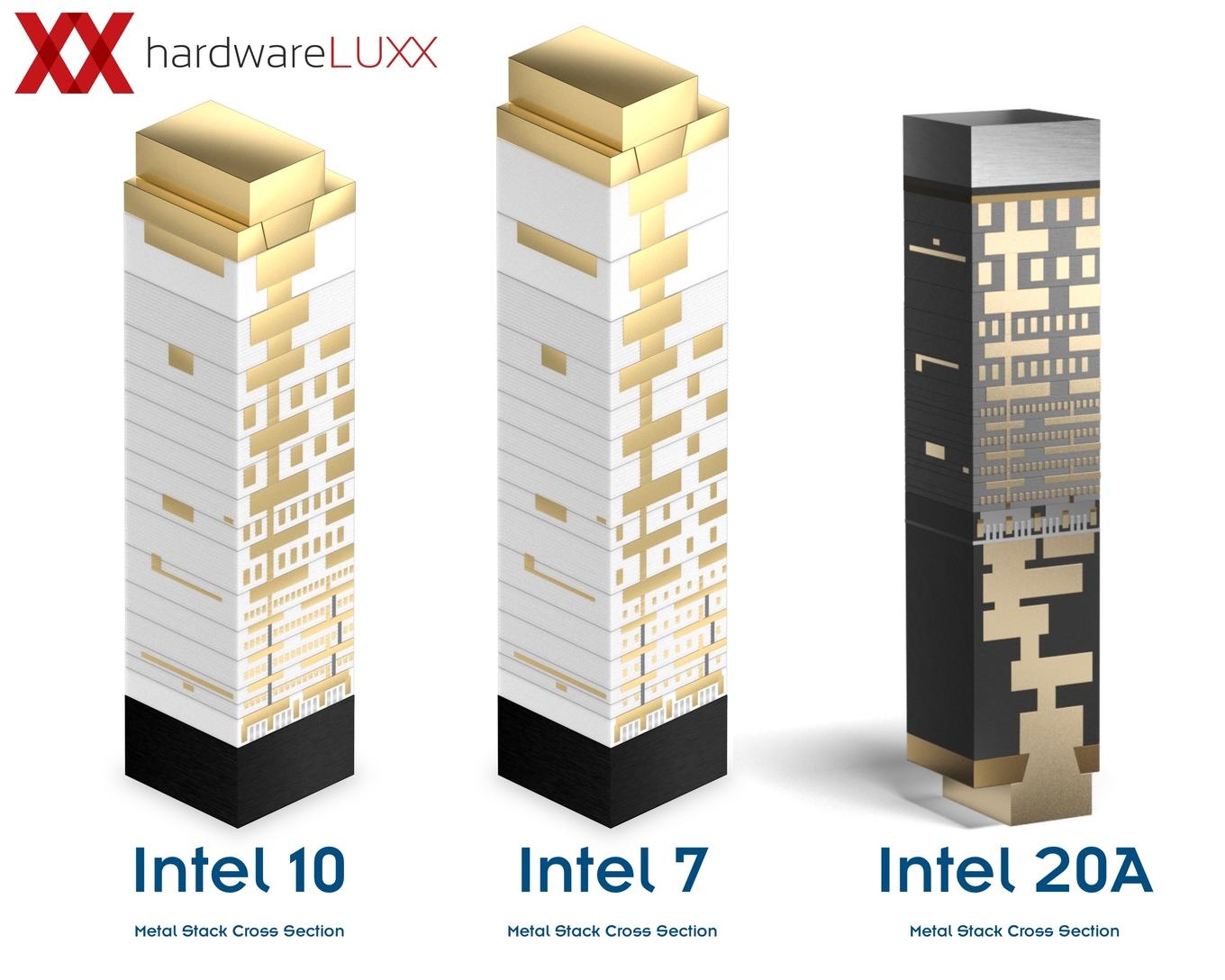

Bisher ist uns jedoch noch nicht ganz klar, wie dies genau funktionieren soll. Intel zeigt ein Schaubild, welches links den derzeitig verwendeten Aufbau zeigt und rechts die Versorgung über PowerVia. Links sehen wir den zu erwartenden Aufbau in der Belichtung eines Wafers. Ganz unten in einer dünnen Schicht mit den grünen Elementen befinden sich die eigentlichen Transistoren. Darüber dann das sogenannte Backend mit den notwendigen Verbindungsebenen für die Kommunikation und die Stromversorgung. Ganz oben befinden sich dann im finalen Packaging die eigentlichen Verbindungen nach Außen.

Das rechte Schaubild soll nun einen in Intel 20A gefertigten Chip mit RibbonFETs und PowerVia zeigen. Die Ausrichtung entspricht in etwa dem, wie wir den Aufbau sehen, wenn sich der Chip auf dem PCB und wieder im Sockel befindet. Unten ist nun die Stromversorgung des Chips untergebracht, die bis in die dünne Ebene geführt wird, in der sich die eigentlichen Transistoren befinden. Darüber ist dann wiederum das Frontend abgebildet – so wie wir es auch vom bisher verwendeten Aufbau kennen. Etwas unterhalb der Transistorebene ist eine dünne, graue Ebene zu erkennen, welche die Trennschicht zwischen der Vorder- und Rückseite des Wafers sein soll. Oberhalb aller Strukturen befindet sich wieder eine dicke Siliziumschicht, der Schnitt durch den Chip steht hier sozusagen auf dem Kopf. Wie Intel hier aber eine Belichtung von zwei Seiten technisch ausführt, ist uns daher nicht ganz klar.

Auf zukünftigen Architecture Days wird Intel sicherlich weitere Details zu den RibbonFETs und PowerVia verraten. Erst für 2024 ist die Fertigung der ersten Chips in Intel 20A mit eben diesen Technologien geplant.

Um die Unterschiede im Aufbau der Transistoren und des Chips aufzuzeigen, haben wir die schematischen Zeichnungen und Darstellungen noch einmal gegenübergestellt.

Die Verbesserungen im FinFET-Design beziehen sich zum einen auf den Aufbau des Transistors selbst. So können die Dimensionen von Gate, Source und Drain angepasst werden, so dass geringere Spannungen notwendig sind oder die Schaltgeschwindigkeiten gesteigert werden. Mit den GAA-Transistoren ändert sich der komplette Aufbau, wie an der Darstellung des RibbonFET zu erkennen ist. Es werden gleich mehrere Transistoren gestapelt (wie bei den FinFETs), allerdings sind um die Gates auf allen vier Seiten ultradünne Kanäle gewickelt. Dies verbessert die Gate-Steuerung und erhöht die Leistung des Transistors.

Im Vergleich zu den FinFETs mit niedrigerer Spannung können die RibbonFETs höhere Ströme schalten. Nicht nur bei Intel stehen die GAAs als Nachfolger der FinFETs in den Startlöchern, auch Samsung und TSMC werden in den kommenden Jahren erste Fertigungen damit anbieten.

Zum Abschluss noch ein Abgleich der Schnitte durch einen Chip mit den Optimierungen für die FinFETs und letztendlich den Wechsel auf RibbonFET und PowerVia. Zwischen Intel 10 und Intel 7 tut sich vor allem etwas im Aufbau des Metal Stack. Mit Intel 20A wechselt man dann auf die neuartige Stromversorgung.

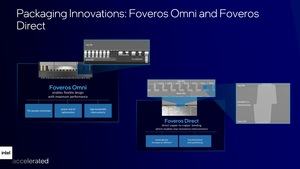

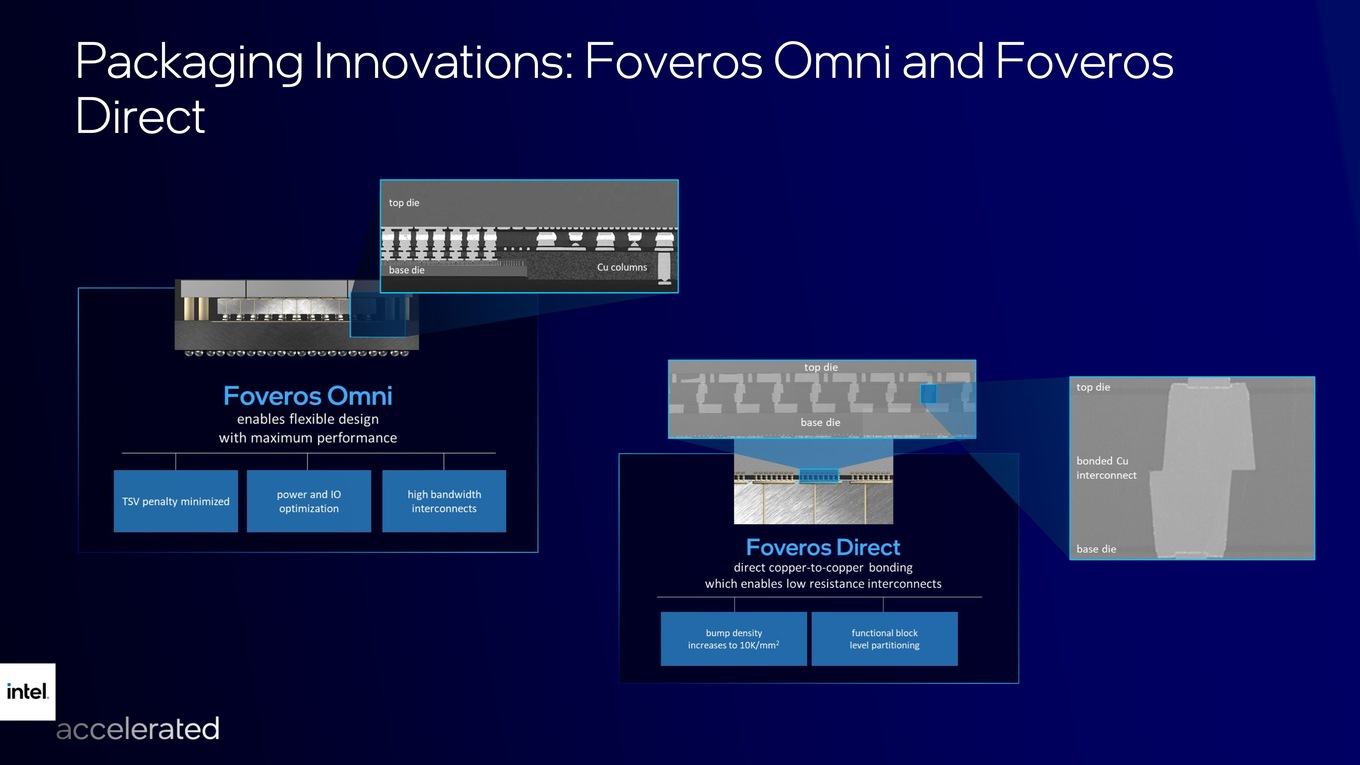

Foveros 2.0 wird zu Foveros Omni und Foveros Direct

Nicht nur in der Fertigung will Intel spätestens in ein bis zwei Jahren wieder zu alter Stärke zurückkehren. Bei den Packaging-Technologien sieht man sich aktuell schon in führender Position. EMIB und Foveros sind hier die Namen der entsprechenden Technologien, die sich schon im Einsatz befinden.

Foveros kam für die inzwischen eingestellten Lakefield-Prozessoren zum Einsatz, EMIB schon bei den Core-Prozessoren mit Radeon-RX-Vega-M-Grafik. Auch für Sapphire Rapids, also die nächste Xeon-Generation, wird EMIB der ersten Generation mit einem Bump-Abstand von 55 µm verwendet werden. EMIB 2.0 kommt auf einen Bump-Abstand von 45 µm, was die Dichte des Interconnects erhöht und die Bandbreite in der Verbindung erhöhen soll.

Foveros ist das zweite Steckenpferd im Rahmen der Packaging-Technologien bei Intel. Für die zweite Generation teilt Intel dies in Foveros Omni (Verbindung mehreren Tiles in einem 2.5D-Stacking) und Foveros Direct (ein Stapeln von Dies aus gleicher Fertigung) auf. Beide Techniken sollen sowohl für die eigenen Produkte, als auch im Foundry-Angebot zum Einsatz kommen. Für Foveros Omni spricht Intel von einem möglichen Bump-Abstand von 25 µm. Die erste Generation von Foveros kommt auf 36 µm.

Foveros Direct erinnert stark an das Stapeln von SRAM, wie es AMD für den 3D V-Cache verwendet. Dahinter verbirgt sich das Chip-Stacking SoIC von TSMC. Auch Intel verwendet für Foveros Direct eine Direkverbindung mit Bumps aus Kupfer – so wie TSMC mit SoIC. Der Bump-Abstand soll hier auf 10 µm zusammenschrumpfen.

Der HPC-Beschleuniger Ponte Vecchio wird als erster Chip Foveros der ersten Generation und EMIB der zweiten Generation verwenden.

Qualcomm und Amazon sind erste Kunden für Intel

Die heutige Ankündigung begann mit IDM 2.0 und endet auch damit. Als erste Kunden für das Foundry-Geschäft nennt Intel Qualcomm für die Fertigung eines Chips in Intel 20A und Amazon, die vermutlich für einen Datacenter-Prozessor das Packaging von Intel in Anspruch nehmen werden.

Zum Abschluss noch ein paar Videos, die Intel zum Update von EMIB, Foveros und den neuen RibbonFET sowie PowerVia veröffentlicht hat:

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen

Datenschutzhinweis für Youtube

An dieser Stelle möchten wir Ihnen ein Youtube-Video zeigen. Ihre Daten zu schützen, liegt uns aber am Herzen: Youtube setzt durch das Einbinden und Abspielen Cookies auf ihrem Rechner, mit welchen Sie eventuell getracked werden können. Wenn Sie dies zulassen möchten, klicken Sie einfach auf den Play-Button. Das Video wird anschließend geladen und danach abgespielt.

Ihr Hardwareluxx-Team

Youtube Videos ab jetzt direkt anzeigen