Werbung

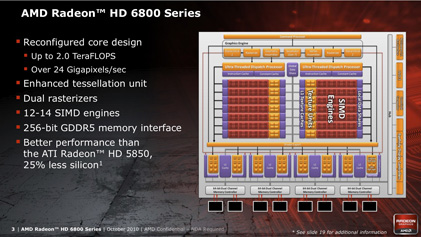

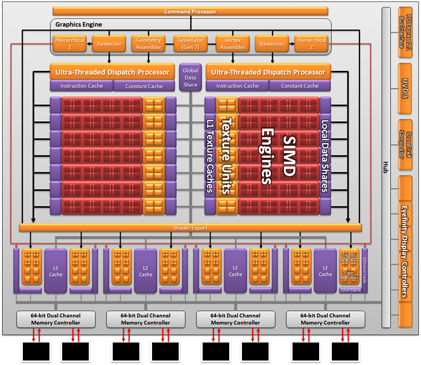

Innerhalb der eigentlichen Architektur hat sich für die AMD Radeon HD 6850 und 6870 nichts getan. Die 960 bzw. 1120 Stream-Prozessoren teilen sich wie folgt in Thread-Prozessoren und SIMD-Einheiten (Single Instruction Multiple Data) auf. Für die Radeon HD 6860 sind 12 SIMD-Einheiten vorgesehen. Bei der Radeon HD 6870 sind es 14. Jede von diesen besteht aus 16 Thread-Prozessoren, die sich nochmals in jeweils 5 Stream-Prozessoren aufteilen. Jede SIMD-Einheit beinhaltet zudem noch vier Texture-Units, bei 12 SIMDs ergibt dies 48 Texture-Units. Für die Radeon HD 6870 mit ihren 14 SIMDs sind dies entsprechend 56.

Durch Klick auf das Bild gelangt man zu einer vergrößerten Ansicht

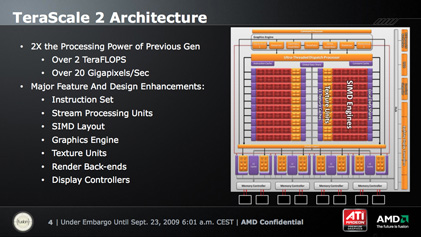

Links ist der Aufbau der RV870-GPU zu sehen, rechts Barts. Es zeigt sich, dass AMD im mittleren Block einige Logik entfernt hat und so auch auf die geringere Anzahl an SIMD-Einheiten sowie weiteren Komponenten der Architektur kommt. AMD spricht von einer Neukonfiguration.

Zumindest im Vergleich zur AMD Radeon HD 5850 wird so bei einer 25% kleinen GPU eine leicht höhere Performance erreicht, so AMD. Besonders stark optimiert worden sein soll die Tesselation-Einheit. Auf einer eigenen Seite gehen wir darauf noch einmal etwas genauer an und erklären auch, warum das der Fall ist.

Wie oben bereits erwähnt, teilt sich jeder Thread-Prozessor in fünf Stream-Prozessoren auf. Bei vieren handelt es sich um flexible Stream-Prozessoren, die pro Takt sowohl eine MADD (Multiply-ADD), als auch eine MUL (Multiplikation) durchführen können. Unter bestimmten Bedingungen können auch beide Operationen in einem Takt berechnet werden. Neben den vier Stream-Prozessoren befindet sich in einem Thread-Prozessor aber auch noch eine Special Function Unit (SFU). Sie berechnet mathematische Operationen wie Sinus-, Kosinus- und Logarithmus-Anweisungen. Eine Branche-Unit im Thread-Prozessor sorgt dafür, dass eine Sprunganweisung im Code ("if-Befehl") nicht eine MADD-Einheit belegt, sondern von einer gesonderten Funktionseinheit berechnet wird.

Durch Klick auf das Bild gelangt man zu einer vergrößerten Ansicht

AMD bleibt der VLIW-(Very Long Instructions Word)-Befehlssatzarchitektur der Länge 5 als auch bei Barts treu. Es können fünf parallele Instruktionen auf einem VLIW-Shader ausgeführt werden. AMD und NVIDIA gehen hier sehr unterschiedliche Wege. AMD ist derzeit aber auch auf der Suche nach dem richtigen Konzept für die Zukunft und so könnte uns mit dem nächsten Entwicklungsschritt hier schon eine Neuerung erwarten.

Jede SIMD-Einheit verfügt über einen 8 kB großen L1-Cache, der wiederum mithilfe einer Crossbar mit dem L2-Cache verbunden ist. Dessen Kapazität bleibt wie beim RV870 bei 128 kB pro Speichercontroller. Der Einsatz der DirectX-11-Features sowie die erhöhte Anzahl an Texture-Units und deren Anbindung an den Speichercontroller erlauben eine maximale Texturgröße von 16.000 x 16.000 Pixeln.