Werbung

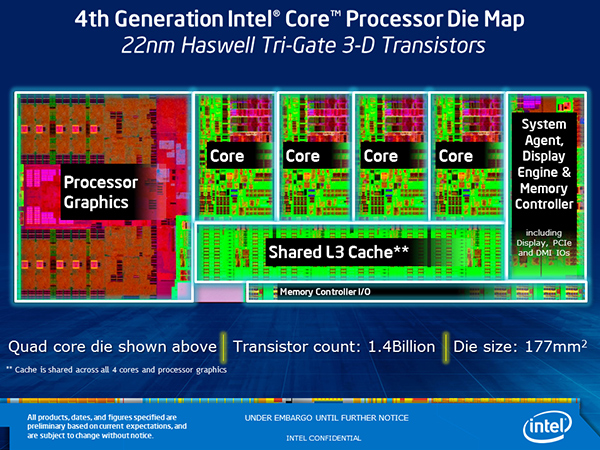

Erinnern wir uns kurz an Ivy Bridge: Im Vergleich zu Sandy Bridge hatte Ivy Bridge keine großartigen Veränderungen an der CPU-Architektur, denn Ivy Bridge war hauptsächlich ein "Tick", es wurde eine neue Fertigungstechnologie eingeführt. Trotzdem waren 400 Millionen mehr 22-nm-Tri-Gate-Transistoren auf der CPU vorhanden, weshalb Intel auch gerne von einem "Tick+" gesprochen hat. Doch diese hinzugefügten Transistoren gehörten alle zur Grafikeinheit von Ivy Bridge. An der Struktur der CPU, am Aufbau, dem Memory Controller und anderen Bereichen hat Intel nur Detailverbesserungen durchgeführt.

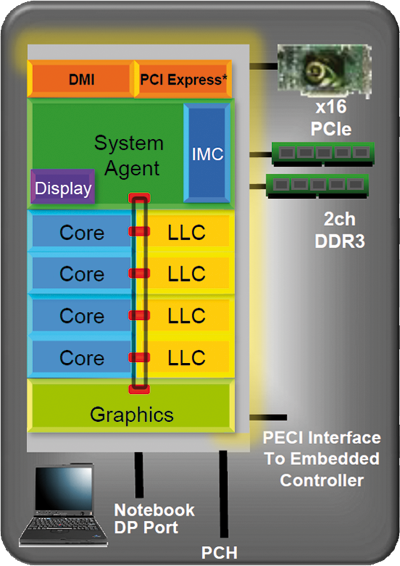

Wenn man die Architektur von Haswell nun betrachtet, kann man sich im Vergleich somit eigentlich auf Sandy Bridge beziehen. Erstmals gab Intel auf dem vergangenen Intel Developer Forum im September 2012 in San Francisco Einblicke in die Haswell-Architektur. Im Endeffekt hat Intel aber den groben Aufbau von Sandy-Bridge beibehalten:

Leistung für die integrierte Grafik mitzubringen. Bei Ivy Bridge ist er in

unveränderter Art ebenso vorhanden, ähnlich sieht es bei Haswell aus.

Mit Sandy Bridge führte Intel den Ring-Bus-Cache ein. Schaut man auf einen Die-Shot von Haswell, kann man diese Struktur weiterhin erkennen. Ein Ring-Bus verbindet weiterhin die Cores, Caches und die Grafik, auch der System Agent besitzt dieselben Funktionen:

Was hat sich nun bei Haswell im Vergleich zu Sandy Bridge verbessert?

Veränderungen an den Kernen

Im September letzten Jahres gab Intel erstmals einen Einblick in die Haswell-Architektur. Erstaunlicherweise berichtete man dort von einer Erhöhung der Single-Thread-Performance. Um dies zu erreichen, hat man einige Verbesserungen in die maximal vier Kerne von Haswell integriert: Wie bei jedem Intel-Prozessor wurde wieder an der Branch Prediction Einheit gefeilt, das Front End des Prozessors wurde massiv verbessert, die Puffer vergrößert und die Anzahl der Execution Units erhöht (von sechs auf nun acht), während gleichzeitig deren Latenz verbessert wurde. Hinzu kommt eine größere Bandbreite bei den Caches, deren Größe aber zumindest im L1- und L2-Bereich unverändert bleibt.

Intel erreicht durch eine Erhöhung der Buffer Sizes eine bessere Parallelisierung von Workloads. Haswell hat im Vergleich zur Sandy-Bridge-Architektur in allen Bereichen (Out-of-Order Window, In-Flight Loads, In-Flight Stores, Scheduler Entries, Integer Register Files, FP Register Files und Allocation Queues) eine größere Buffer Size. Dabei hat Intel aber aufgrund der Effizienz darauf geachtet, die Buffer auf einem aufeinander abgestimmten Niveau zu halten und nicht zu sehr aufzublasen - denn ungenutzte Buffer verbrauchen nur Strom, bringen aber keinen Geschwindigkeitsvorteil mehr.

Konkret hat Intel zwei Fused-Multiply-Add-Einheiten für AVX hinzugefügt, zwei zusätzliche Ports mit einer vierten Integer-ALU, eine zweite Sprungeinheit und eine Store-Adress-Einheit. Die Pipeline hat Intel beibehalten und sie nicht verlängert. Mit einigen Veränderungen entspricht sie also noch dem Vorgänger Sandy Bridge (und in der Basis sogar noch dem Pentium Pro). Die Größe des Out-of-Order-Window steigt auf 192 Einträge, Sandy Bridge besaß 168 Einträge. Gleichzeitig hat man die Reservation Station von 54 auf 60 Einträge aufgebort. Die Execution Unit 7 entlastet die beiden Load/Store-Ports 2 und 3 durch eine dedizierte Store-Address-Einheit. Intel hat auch die physischen Register vergrößert, jetzt stehen 168 Einträge für das Floating-Point-Gleitkommaregister statt vorher 144 Einträge zur Verfügung, auch die Integer-Register wurden mit 168 Einträgen leicht erweitert (160). Als wichtige Veränderung hat Intel zudem die Größe des Unified Translation Lookaside Buffers (L2 Unified TLB) auf eine Größe von 4K + 2M shared mit 1024 Einträgen statt 512 Einträge bei Sandy Bridge aufgebohrt. Wichtig war Intel die Beibehaltung der Länge der Pipeline und niedrige Latenzzeiten zu den Caches.

{jphoto image=28486}

Neue Befehlssätze: Advanced Vector Extensions 2

Ein weiteres neues Kernfeature für Haswell sind Advanced Vector Extensions 2 (kurz Intel AVX2). Diese Befehlssatzerweiterung besitzt unter anderem jetzt 256-bit Integer Vectors, zudem wird Fused Multiply-Add (zwei Einheiten für AVX) unterstützt. Intel schafft es damit die Flops pro Taktzyklus bei Haswell zu verdoppeln. Als Resultat erhält man bei Anwendungen, die AVX2 nutzen, eine deutlich höhere Performance. Die Integer Instructions behandeln hauptsächlich den Bereich Indexing und Hashing, Kryptografie und Endian Conversion (MOVBE). Durch Fused Multiply-Add wird zudem das Rechenergebnis genauer, da bei einer getrennten Operation zwei Rundungsvorgänge vorhanden sind, bei der Abwicklung mit FMA jedoch nur einer enthalten ist.

Cache-Bandbreite und sonstige Verbesserungen

Spannend sind die Verbesserungen bei der Cache-Bandbreite. Während die Größe für den L1-Instruction- und Data-Cache weiterhin bei 32K und einer 8-fach assoziativen Anbindung geblieben sind, hat Intel die Load- und Store-Bandbreite im Vergleich zu Sandy Bridge von 32 Bytes pro Cycle auf 64 Bytes pro Cycle für Load und von 16 Bytes/Cycle auf 32 Bytes/Cycle für Store aufgebohrt. Der L2-Cache bleibt ebenso bei 256K und 8-Fach assoziativer Anbindung, auch hier bohrt man die Bandbreite zum L1-Cache auf 64 Bytes/Cycle auf.

Auch den System Agent und Last Level Cache hat Intel überarbeitet. Man bietet unter anderem mehr Bandbreite für den Shared Last Level Cache durch neue, dedizierte Pipelines, die Data und Non-Data-Zugriffe parallel behandeln können. Für den System Agent gibt es einen neuen Load-Balancer, der die Ressourcen effektiver verteilen kann. Zudem wird auch der DRAM Write Throughput durch bessere Queues und einen besseren Scheduler beschleunigt. Letztendlich hat Intel die Geschwindigkeit für Roundtrips bei Virtualisierung in VT-x noch einmal deutlich beschleunigt, hier liegt man jetzt unter 500 Zyklen pro Roundtrip.

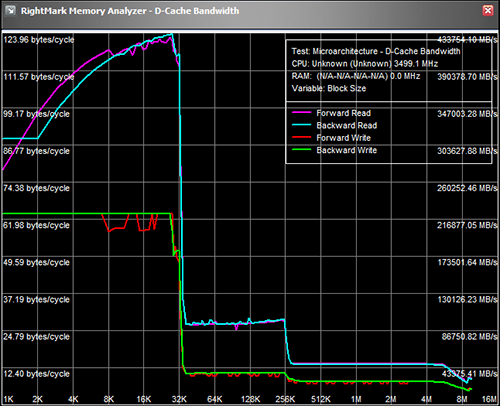

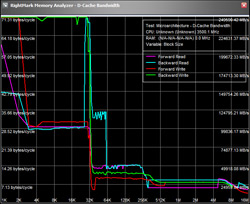

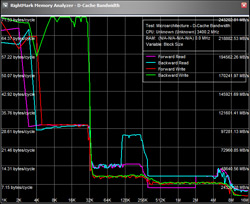

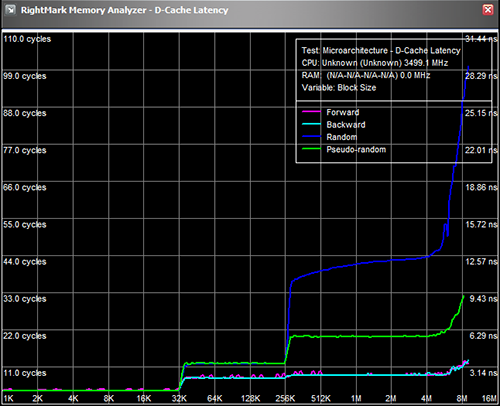

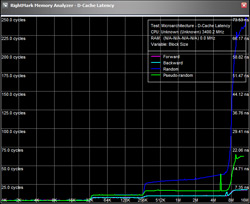

Für einen Leistungsvergleich der Bandbreite haben wir mit CPU Rightmark die Cache Latenz (oben) und die Cache Bandbreite (unten) gemessen.

Cache-Latency-Vergleich:

Oben Haswell, Links Ivy Bridge, Rechts Sandy Bridge

Cache-Bandbreiten-Vergleich:

Oben Haswell, Links Ivy Bridge, Rechts Sandy Bridge

Die Performance ist fast so, wie sie von Intel versprochen wurde: Bei der Bandbreite der Caches sieht man durch alle Bereiche (L1, L2, L3), dass Haswell schneller an die Daten kommt - die Bandbreite ist also deutlich gestiegen. Die Latenzzeiten wollte Intel zwar möglichst gleich beibehalten, allerdings ist hier ein marginaler Anstieg zu erkennen, der aber wohl eher zu vernachlässigen ist.

Intel Transactional Synchronization Extension (TSX) mit Lock Elision

Damit Multi-Core-Prozessoren immer mit validen Daten arbeiten, gibt es sogenannte Locks. Greifen mehrere Threads auf den Speicher zu, wird der entsprechende Bereich zunächst gesperrt (Lock), um eine Veränderung während der Verarbeitung zu verhindern. Mit diesem Prinzip rechnet jeder Kern für sich ein valides Ergebnis aus, da die Daten immer aktuell sind. Im Normalfall sind diese zeitaufwändigen Locks allerdings überflüssig, da nur sehr selten mehrere Threads bei Speicherzugriffen auf denselben Bereich konkurrieren. Hierfür gibt es mit Haswell nun TSX und Transactional Memory: Ein Speicherzugriff kann auch ohne Lock geschehen, somit können schneller Daten zur Bearbeitung in den L1-Cache geladen werden. Allerdings muss es hardwareseitig einen Mechanismus geben, der konkurrierende Zugriffe erkennt und dann die Berechnung abbricht.

Haswell hat zwei derartige Mechanismen. Hardware Locked Elision arbeitet nach dem obigen Prinzip und berechnet bei einem Konflikt denselben Code noch einmal unter Berücksichtigung der Locks. Restricted Transactional Memory hingegen meldet einen Abbruch erst einmal an die Software, die dann durch einen vorgesehenen Codepfad selber entscheiden kann, ob er mit Locks arbeiten möchte oder die Transaktion später wiederholen möchte. Beide Mechanismen arbeiten im L1-Daten-Cache der CPUs, Haswell kann aber auch Teilbereiche in die L2-Caches swappen.

Optimierungen am Stromverbrauch

Beim Stromverbrauch geht Intel den Weg weiter, möglichst alles abzuschalten, was nicht gerade benötigt wird. Interessant ist, dass Intel die Kerne vom LLC+Ring nun trennt und jeweils eine separate Frequency Domain anbietet. Dadurch soll eine genauere Steuerung der Taktraten möglich sein. Die Power Control Unit steuert dabei dynamisch das vorhandene TDP- oder Strom-Budget, wenn man ein Limit angibt.

Intels integrierter Spannungswandler (iVR)

Intel versorgt die CPU mit einer Spannung "VCCin" (Voltage Common Connector "in") von 1,75 Volt. Aus dieser Spannung VCCin generiert Intel alle notwendigen Spannungen für die CPU (z.B. Vcore). Intel nutzt immer noch die Voltage Identification VR 12.5, sodass von 0,5 bis 3,04 V Spannung angelegt werden können. Als minimalen Wert für den Berieb eines Haswell-Prozessors sieht Intel 1,65 Volt an, als maximalen 1,86 Volt. Im C6/C7-Modus sind es 1,5 bis 1,65 V bei 1,6V Sollspannung. Die Spannungswandler sind dabei für eine kurzzeitige Belastung von 100 A ausgelegt, für die integrierte GPU noch einmal 35 A. Für Dauerlast sieht Intel 85 A bzw. 25 A vor, wobei die TDP hier limitierend wirken soll.

Neben der Spannung für die CPU und den System Agent erhält auch die Grafik eine eigene Power Domain. Intel kann die Spannungen für die CPU also so steuern, wie gerade Leistung benötigt wird - das sollte auch die Active Power reduzieren oder gleichzeitig eine höhere Taktung und höhere Turbo-Modi möglich machen.

Für den Mainboardhersteller ergeben sich dadurch Einsparungspotentiale, da Intel den Spannungswandler in die CPU integriert. Die CPU-internen Spannungen Vring, Vgt, Vsa und Vioa, Viod müssen nicht mehr bereitgestellt werden. Es bleibt nur ein Spannungswandler für die Speichermodule (Vddq). Das spart am Layout-Design ein paar Euros und der Bereich um den Sockel kann etwas flexibler gestaltet werden.

Neuer Stromsparmodus "S0ix Active Idle"

Intel hat Haswell neue Power- und Idle-States verpasst. Zum einen hat man neue Funktionen im Power-State im C7-Modus untergebracht. Hier werden alle Takte gestoppt, die Spannung wird vom Hauptteil der CPU genommen - selbst, wenn das Display noch aktiv ist. Die kommenden Ultrabooks bieten dabei sogar Self-Panel-Refresh (SPR), also kann kein Display-Bild bestehen bleiben, während das Ultrabook sich in C7 befindet. Die Zeitspanne zum Aufwecken aus dem C7 Modus und zum Schalten in andere C-Modi hat Intel dabei um 25% beschleunigt.

Durch neue Idle-States - S0ix Active Idle - und eine neue C-State-Intelligenz möchte man den Stromverbrauch weiter senken - und schafft dies gegenüber Ivy Bridge auch massiv im Idle-Power-Bereich. Bei S0ix Active Idle wird der Energieverbrauch des Rechners auf S3/S4-Niveau abgesenkt, aber es gibt keine lange Aufwachzeit. Intel realisiert dies vollautomatisch in der Hardware in feinen Abstufungen. Durch die generelle Beschleunigung zwischen den C-States um 25% und neue Power-Management-Funktionen für die Peripherie sind deutlich schnellere Wechsel innerhalb der C-States möglich.

System Agent (ehem. Uncore-Bereich)

Der System Agent Bereich der CPU hat zwar einige Optimierungen bezüglich der Stromspartechniken erhalten, ansonsten bleibt er aber größtenteils unverändert:

Memory Controller

Keine Änderungen gibt es beim Speicherinterface. Intel setzt immer noch auf den bekannten DDR3-1333/1600, auch Low-Voltage-Dimms und SO-Dimms (AIO-Plattformen) können weiterhin eingesetzt werden. Im Dual-Channel-Betrieb sind somit weiterhin rechnerisch 25,6 GB/s maximale Transferrate möglich. Interessant ist, dass auch weiterhin als größte Speicherkonfiguration nur 8-GB-Speichermodule (Dual-Rank x8 unbuffered non-ECC) eingesetzt werden können. In Z87-Mainboards und Mainboards mit den anderen Chipsätzen können also weiterhin nur 32 GB maximale Bestückung erreicht werden. Als Timings gibt Intel für DDR3-1600 10-10-10 mit 1t oder 2t Command Rate in der Spezifikation an, hier hat sich also ebenso nichts verändert.

PCI-Express-Interface

Auch hier bohrt Intel Haswell nicht auf: Schon Ivy Bridge bekam hier ein Update auf PCI-Express 3.0 - und da dieser Standard momentan immer noch State-of-the-Art ist, bleibt es bei 8 GT/s pro PCIe-Lane, also 984 MB/s. Mit einer theoretischen Bandbreite von 16 GB/s bei PCIe-3.0-x16 pro Richtung kommt man somit auf 32 GB/s Bandbreite insgesamt. Mit Intels Z87-Chipsatz ist auch ein Aufsplitten der Lanes für SLI und CrossFire möglich, die anderen Chipsätze unterstützen diese Aufsplittung nicht.

Direct Media Interface

An der Anbindung zwischen CPU und dem (Z87-)Chipsatz hat Intel keine Veränderungen durchgeführt. Hier kommt die bekannte DMI 2.0 x4-Verbindung zum Einastz. Der Platform-Controller-Hub wird also mit 5 GT/s angebunden, wobei diese Technik insgesamt auf 4 GB/s Übertragungsrate kommt. Das Intel hier keine schnellere Anbindung gewählt hat, ist etwas verwirrend, denn in den letzten Jahren war ein Argument gegen eine größere Anzahl USB3.0- und SATA-6G-Ports die Anbindung zum Prozessor: Man wolle den DMI-Bus nicht zum Flaschenhals werden lassen. Mit den neuen Chipsätzen hat Intel nun reichlich USB3.0- und SATA-6G-Ports, trotzdem geht man wohl davon aus, dass die 4 GB/s Übertragungsrate zum Prozessor kein Problem darstellen.