Werbung

Nachdem wir uns zwei Xeon Platinum 8380 mit jeweils 40 Sunny-Cove-Kernen der neuen Ice-Lake-Plattform von Intel angeschaut haben, hier aber zunächst nur den Vergleich zu den beiden Vorgänger-Generationen bieten konnten, folgt heute die direkte Gegenüberstellung mit AMDs aktuellen EPYC-Prozessoren der 7003-Serie. Gleich vier Modelle im Dual-Socket konnten wir uns seitens AMD anschauen, sodass wir hier eine deutlich breiter aufgestellte Marktübersicht bekommen, als dies für Intels Ice Lake-SP der Fall war. Wo die Stärken liegen und in welchen Bereichen AMD dem Branchenführer Intel derzeit voraus ist, klären wir im nun folgenden Test.

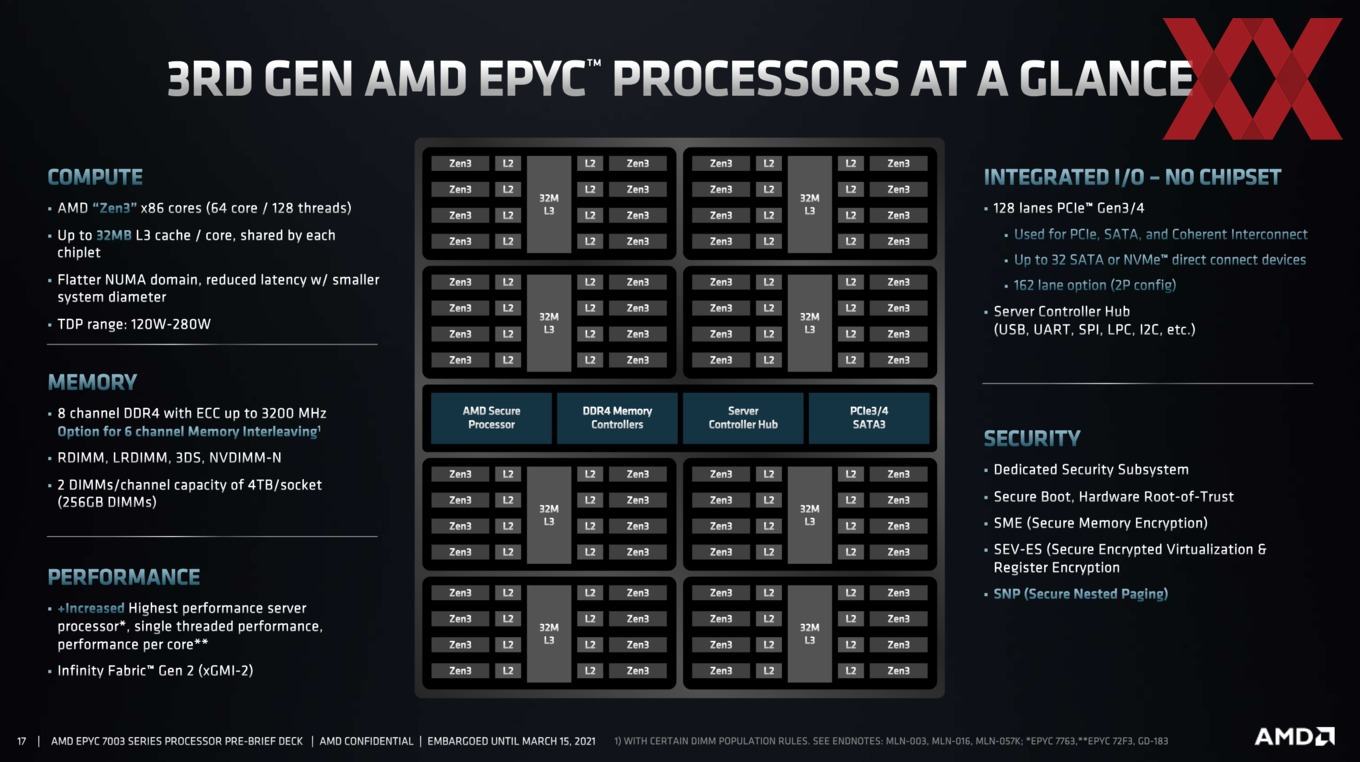

Mitte März stellte AMD seine neue EPYC-Generation alias 7003-Serie alias Milan offiziell vor. Mit bis zu 64 Kernen pro Sockel ist man Intel noch immer voraus, auch wenn der Konkurrent mit seinen 40 Sunny-Cove-Kernen hier aufgeholt hat. Acht Speicherkanäle für DDR4-3200 bieten inzwischen beide Hersteller, aber die 128 PCI-Express-Lanes nach dem 4.0-Standard sind hinsichtlich der I/O-Funktionalität noch immer ein deutlicher Pluspunkt für AMD. Aber trotz dieser technischen Überlegenheit hat es AMD bisher erst geschafft etwa 10 % des Marktanteils für sich zu gewinnen. Das Datacenter-Geschäft ist träge und wenig wechselwillig. Hinzu kommt, dass Intel einige Speziallösungen abdecken kann, welche die Unzulänglichkeiten der Skylake- und Cascade-Lake-Generation gekonnt übertüncht haben. Die AVX-512-Befehlssätze, AVX-512-VNNI bzw. DL-Boost und Optane Persistent Memory 200 sind daher auch in unserem Test ein Bestandteil gewesen.

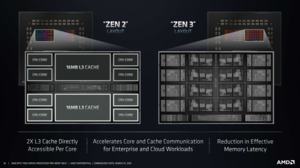

Die langfristig ausgelegten Pläne bei AMD trage inzwischen Früchte. Mit der Zen-3-Architektur ist man auf Augenhöhe mit Intel und setzt diese als zentralen Bestandteil auf allen Mobile-, Desktop- und Serverprozessoren ein. AMD beschriebt die Zen-3-Architektur mehrfach als erste vollständige Neuentwicklung nach der ersten Zen-Generation. Der neue 8-Kern-Core-Complex (CCX), der sich einen gemeinsamen und 32 MB großen L3-Cache mit weiteren CCX-Ausbaustufen teilt, ist ein wichtiger Bestandteil der Weiterentwicklung.

Alle Details der Zen-3-Architektur haben wir bereits zum Start der Ryzen-5000-Serie genauer beleuchtet. Zu den EPYC-Prozessoren zeigen sich darin keinerlei Unterschiede, wenngleich die beiden Produktgruppen von den gebotenen Funktionen der Zen-3-Architektur jeweils anders Gebrauch machen.

Die Fertigung ist mit 7 nm identisch geblieben. Das durchschnittliche IPC-Plus kommt ohnehin rein über die Mikroarchitektur zustande und teilt sich auf die verschiedenen Maßnahmen auf. Zu diesen gehören Änderungen der Load/Store-Units, im gesamten Front End, dem Micro-op Cache, der Sprungvorhersage (Branch Predictor), den ausführenden Recheneinheiten und dem nun einheitlichen Cache.

Ein CCD bestand bisher aus zwei CCX-Clustern mit jeweils vier Kernen. Die vier Kerne haben sich jeweils 16 MB an L3-Cache geteilt, sodass wir von 2x 16 MB L3-Cache pro CCD sprechen. Für Zen 3 wechselt AMD auf ein CCX mit acht Kernen, die sich insgesamt 32 MB an L3-Cache teilen. Es gibt vor allem keine Crossbar mehr zwischen den zwei L3-Cache-Clustern, wenn Kerne aus einem anderen CCX auf den Speicher zugreifen wollen.

Dies reduziert die Latenz bei Zugriffen im L3-Cache. Je mehr Kerne auf einen gemeinsamen Cache zugreifen, desto höher werden die Latenzen. Acht Kerne für 32 MB sieht man als derzeitigen Sweet Spot. Alle Kerne im CCX-Complex sind direkt miteinander verbunden. Es gibt acht Slices zu jeweils 4 MB pro Kern. Ein Vorteil dieser Zusammenführung des L3-Caches ist aber auch, dass ein Kern mit Zen 3 maximal 24 MB an exklusivem L3-Cache für sich verwenden kann, während die restlichen 8 MB weiterhin unter allen Kernen geteilt werden.

An der Cache-Hierarchie vom L1- bis zum L3-Cache hat sich nichts getan. Hier werden die Daten jeweils mit 32 Byte pro Takt untereinander ausgetauscht. Die L1-Anbindung setzt sich also in Sachen Bandbreite bis zum L3-Cache fort.

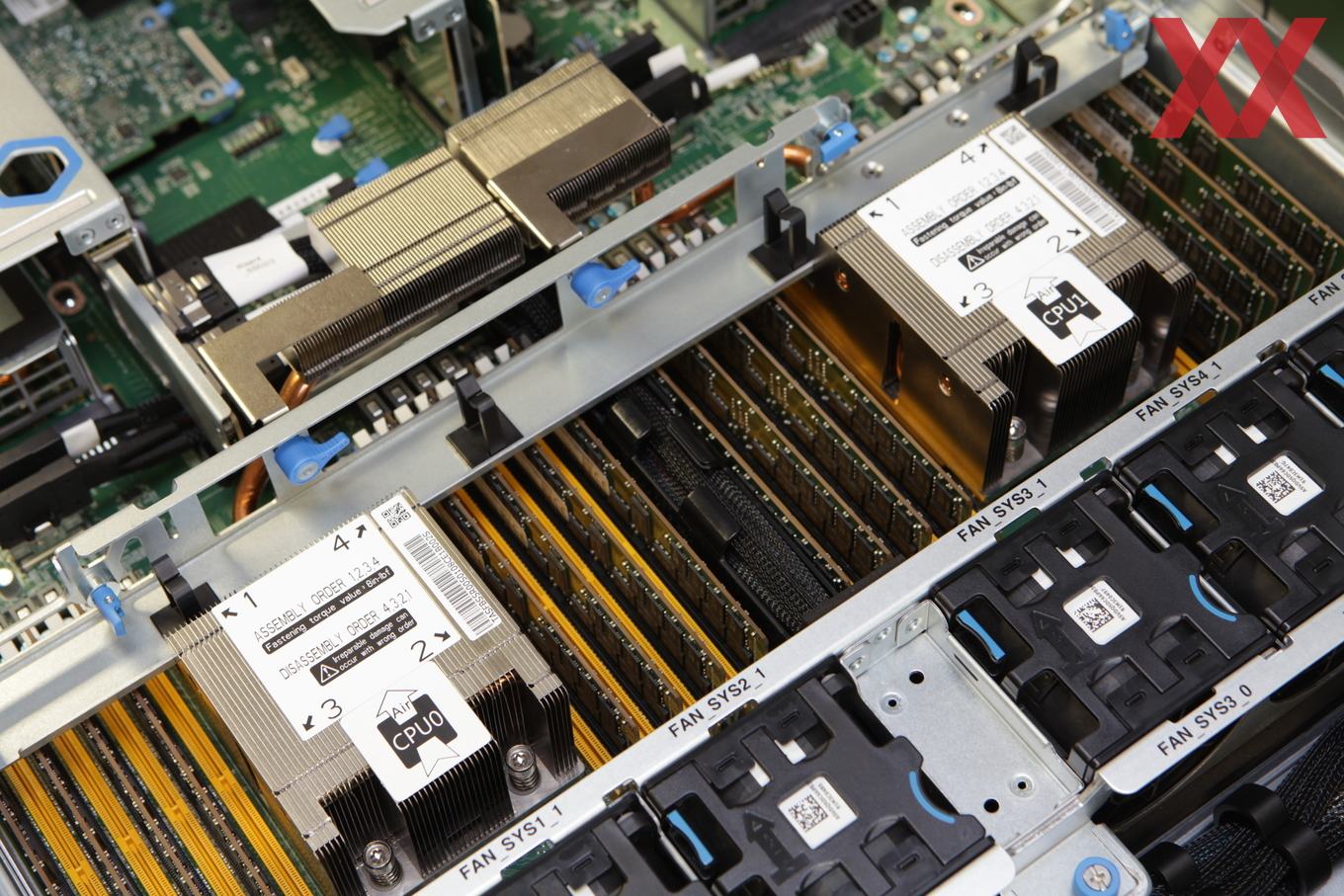

Am Aufbau hat sich von der zweiten auf die dritte EPYC-Generation auf den ersten Blick wenig getan:

Es bleibt bei maximal 64 Kernen pro EPYC-Prozessor. Diese können jeweils zwei Threads verarbeiten, was bei 64 Kernen eben 128 Threads bedeutet. Die TDP-Spanne reicht weiterhin von 120 bis 280 W und bereits bestehende SP3-Mainboards und Systeme können die EPYC-Prozessoren der 7003-Serie aufnehmen.

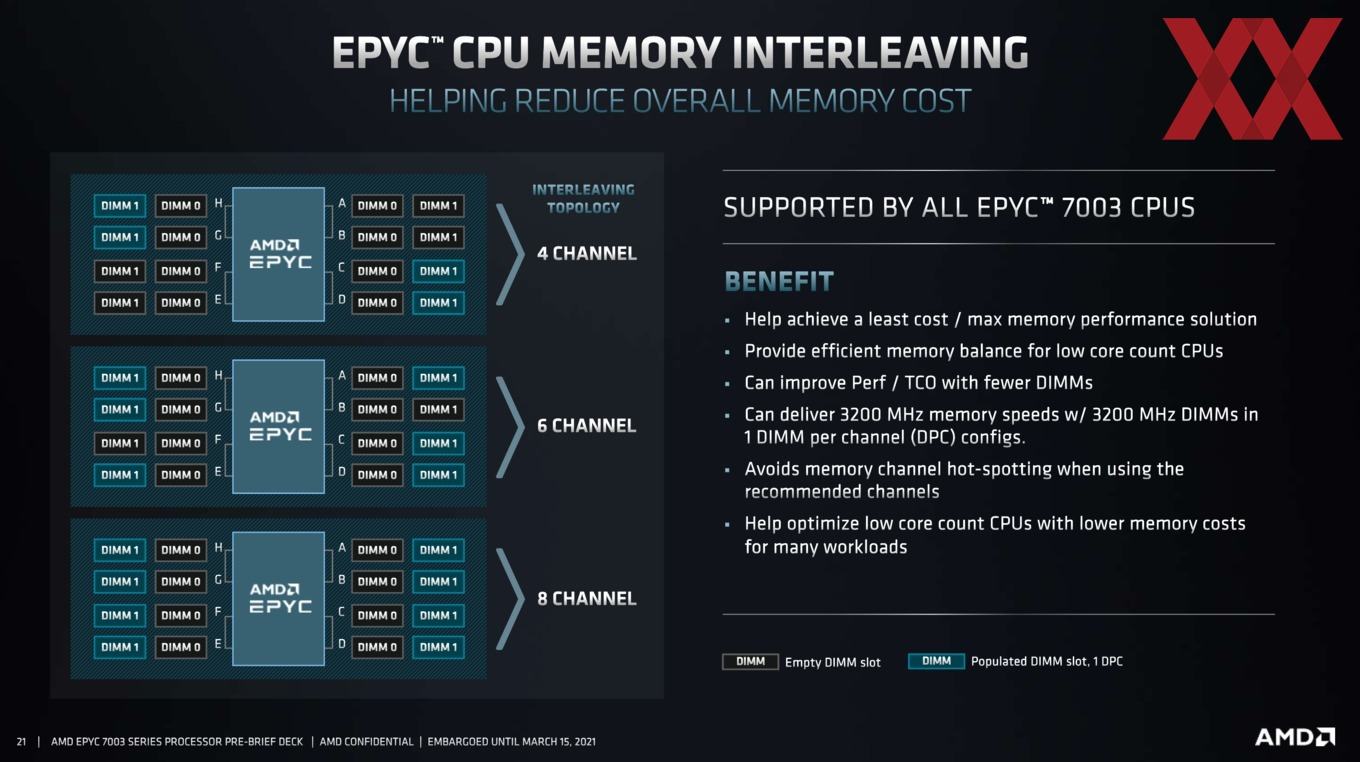

Grundsätzlich bleibt es auch bei den acht Speicherkanälen die, DDR4-3200 (RDIMM, LRDIMM, 3DS und NVDIMM-N) mit einer maximalen Kapazität von 256 GB ansprechen können. Damit ist ein Maximalausbau von 4 TB pro Sockel möglich. Neu ist, dass AMD nun ein Memory Interleaving unterstützt. Was sich genau dahinter verbirgt, schauen wir uns noch an.

Die Plattform als solches bleibt in den weiteren Punkten unangetastet. So stehen weiterhin 128 PCI-Express-Lanes nach dem 4.0-Standard zur Verfügung. Ein Dual-Sockel-System bietet 162 PCI-Express-Lanes.

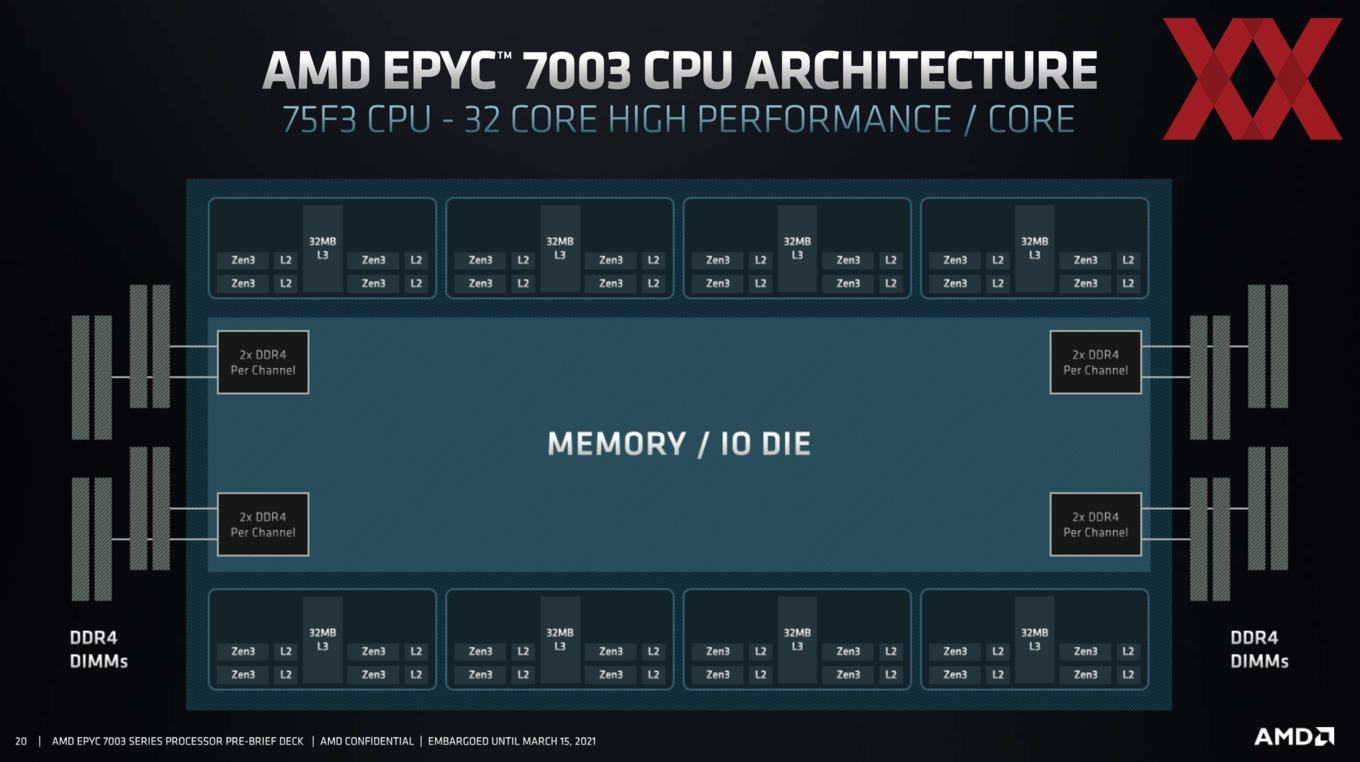

Grundsätzlich hat sich beim IOD für die 7003-Serie nichts bis wenig getan. Weiterhin ist der das zentrale Bestandteil für die Anbindung der acht CCDs und stellt nach Außen hin die Speicherkanäle und PCI-Express-Lanes zur Verfügung. Der IOD des Vorgängers kommt auf eine Chipfläche von 416 mm² und besitzt 8,34 Milliarden Transistoren.

Der IOD der 7003-Serie ist nicht identisch, wird aber weiterhin in 14 nm gefertigt. Laut AMD ist die Größe identisch, allerdings hat sich die Anzahl der Transistoren durch das Memory Interleaving leicht erhöht.

| Die-Größe | Transistoren | |

| CCD (Zen) | 212 mm² | 4,8 Milliarden |

| CCD (Zen+) | 212 mm² | 4,8 Milliarden |

| CCD (Matisse & Rome) | 74 mm² | 3,9 Milliarden |

| CCD (Vermeer & Milan) | 80,7 mm² | 4,15 Milliarden |

| IOD (Matisse) | 125 mm² | 2,09 Milliarden |

| IOD (Vermeer) | 125 mm² | 2,09 Milliarden |

| IOD (Rome) | 416 mm² | 8,34 Milliarden |

| IOD (Milan) | 416 mm² | 8,34 Milliarden* |

| Rome insgesamt: 8x CCD + IOD | 1.008 mm² | 39,54 Milliarden |

| Milan insgesamt: 8x CCD + IOD | 1.061,6 mm² | 39,54 Milliarden* |

| Intel XCC-Die (Skylake) | 694 mm² | - |

| NVIDIA GA100-GPU | 826 mm² | 54,2 Milliarden |

*Genaue Anzahl der Transistoren des Milan IOD bisher nicht bekannt

Mit Veröffentlichung der Ryzen-5000-Prozessoren verkündete AMD die Größe des Zen-3-CCDs mit 80,7 mm². Außerdem soll jedes einzelne dieser Chiplets über 4,15 Milliarden Transistoren verfügen. Die CCDs mit den Kernen sind also etwas größer und komplexer geworden. Laut AMD ist der IOD zwischen Rome und Milan nahezu identisch. Durch die größeren CCDs ergeben sich dennoch Änderungen in der Gesamtgröße und Gesamtkomplexität der Chiplet-Konstruktion.

Rome kommt auf 1.008 mm² bei insgesamt 39,54 Milliarden Transistoren. Bei Milan sind es nun 1.061,6 mm² bei 39,54 Milliarden Transistoren. Am Package tut sich allerdings nichts. Unter dem Heatspreader rücken die einzelnen Chiplets nur marginal enger zusammen. Die Gesamtleistungsaufnahme ist ebenfalls identisch und durch die größeren CCDs sollte es sogar einfacher sein, die Abwärme abzuführen.

IMC beherrscht weiteres Memory Interleaving

Mit den EPYC-Prozessoren der 7003-Serie führt AMD das Memory Interleaving für die Nutzung von nur sechs der acht zur Verfügung stehenden Speicherkanälen ein. Bei den vorherigen EPYC-Generationen war es natürlich möglich, auch weniger als acht Speicherkanäle zu verwenden. Während nur mit acht belegten Speicherkanälen die maximale Speicherbandbreite erreicht werden konnte, war es aber auch mit nur vier genutzten Speicherbänken möglich, noch in etwa 50 % der Speicherbandbreite zu erreichen. Dazu musste von den jeweils vier Speichercontrollern mit jeweils zwei Kanälen immer ein Kanal pro Speichercontroller belegt werden. Wurden zwei Speichercontroller mit jeweils zwei Speicherkanälen verwenden, führte dies zu einer Asymmetrie, die sich negativ auf die Leistung auswirkte. Je nach Anwendungen, wenn diese nicht sensitiv auf die Speicheranbindung sind und auch die Kapazität nicht ausgeschöpft werden musste, konnte eine solche Konfiguration (die Bestückung eines Speicherkanals mit einem DIMM) Sinn machen.

Problematisch wurde es bisher aber, wenn sechs der acht Speicherkanäle verwendet werden sollten. Hier kam es zu besagter Asymmetrie, da die Hälfte der Speichercontroller mit einem Kanal arbeiteten und die andere Hälfte auf beiden Kanälen bestückt war. Anstatt also 75 % der theoretischen Leistung konnten hier schlimmstenfalls nur zwischen 40 und 60 % der zu erwarteten Speicherbandbreite realisiert werden.

Das nun neue Memory Interleaving kommt auch mit der unbalancierten Sechskanal-Bestückung zurecht und soll auf das volle Speicherinterface bezogen, eine Leistung von bis zu 75 % ermöglichen. Dies soll es Kunden ermöglichen, ihre Kosten für den Speicherausbau besser anpassen zu können. Die Interleaving-Technologie hilft zugleich dabei die Auslastung auszugleichen. Außerdem bietet es nun bei einer Bestückung auf nur sechs Kanälen die möglichst ideale Leistung.