Werbung

Neben der Vorstellung der ersten Umsetzung eines Back Side Power Delivery Network (BSPDN) in der A16-Fertigung verkündet TSMC laut Anandtech auf dem 2024 Technology Symposium deutliche Verbesserungen für die geplanten N2-Fertigungsschritte, die mittels NanoFlex-Technologie deutlich effizienter werden sollen.

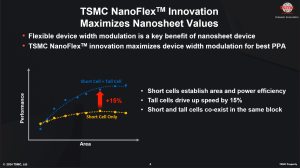

Alle bisher geplanten N2-Fertigungsschritte (N2, N2P, N2X) werden NanoFlex unterstützen. Dabei handelt es sich um eine Technologie, die es einfacher ermöglicht, verschiedene unterschiedliche Zell-, bzw. Transistor-Bibliotheken zu verwenden. Für den Logikbereich eines Prozessors werden andere Bibliotheken verwendet als für die Caches. Einige Bereiche müssen einen besonders hohen Takt erreichen können, andere wiederum will man möglichst eng packen können.

Da die N2-Fertigungsschritte allesamt auf die neuen Nanosheet-Transistoren setzen werden, hat TSMC die FinFlex-Technologie so weiterentwickelt, dass sie als NanoFlex für die neuen Transistoren funktioniert. Je nach Funktionsbereich soll die NanoFlex-Technologie die Chips um 15 % schneller machen oder für eine höhere Effizienz sorgen können.

Die Fertigung in N2 soll in 2025 in die Risikofertigung gehen. Ab der zweiten Jahreshälfte rechnet TSMC mit der Massenproduktion. Ab 2026 ist dann mit den ersten Geräten zu rechnen, die mit diesen Chips ausgestattet sind. Eine leistungsgesteigerte Variante N2P sowie eine spannungsoptimierte Variante N2X sollen kurz darauf folgen. Auf N2P wird dann die Fertigung in A16 folgen, die erstmals auf die rückseitige Stromversorgung via Super Power Rail (SPR) setzt.

Für N2 werden wie gesagt erstmals die Nanosheet-Transistoren zum Einsatz kommen. Um diese besser, bzw. stabiler versorgen zu können, setzt TSMC auf SHPMIM-Kondensatoren (Super-High-Performance Metal-Insulator-Metal), die in die Versorgungsebene eingearbeitet sind. Bei Intel heißen diese in ähnlicher Form ausgeführten Komponenten Super Metal Insulator Metal (MIM). Im Vergleich zu den aktuell von TSMC eingesetzt SHDMIM-Kondensatoren (Super-High-Density Metal-Insulator-Metal) haben die neuen SHPMIM-Kondensatoren eine doppelt so hohe Kapazität bei geringerem Widerstand.

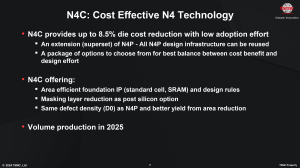

Kostengünstiger N4C-Prozess für 2025 geplant

Zudem hat TSMC für 2025 einen kostengünstigen N4C-Prozess angekündigt. Dieser basiert, wie alle N4-Fertigungsschritte, auf einem 5-nm-Prozess. TSMC hat für N4C für die Standard- und SRAM-Zellen ein neues Design erstellt, welches die Kosten in der Fertigung eines Wafers in N4C um 8,5 % reduziert. Ein weiterer Faktor ist die Reduzierung der Masken-Layer. Diese Kostenreduzierung soll natürlich an den Auftraggeber weitergegeben werden.

Chips, die aktuell in N4P gefertigt werden, können problemlos in N4C überführt werden. TSMC spricht von einer besseren Ausbeute und selben Defekt-Dichte (D0) wie bei N4P. Zudem können Kunden direkt auf N4C springen, ohne dass ihr Chip-Design zuvor auf N4P gefertigt wurde. Die Massenprodukt der ersten Chips in N4C soll 2025 beginnen.