Werbung

Bereits in der vergangenen Woche veranstaltete TSMC in den USA eines seiner Technology Symposium, die üblicherweise im Wochenrythmus dann auch in Europa und Asien abgehalten werden. Bereits aus den USA bekommen wir die Neuheiten, die dann inhaltsgleich zu den anderen Terminen verkündet werden.

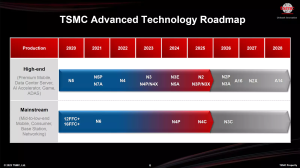

In der Fertigung lag der Fokus auf N2 als nächster großer Schritt. Zwar hat TSMC bereits die Nachfolger A16 und A14 namentlich erwähnt, in der zweiten Jahreshälfte 2025 werden jedoch die ersten Chips aus der N2-Fertigung erwartet und so nannte TSMC hierzu die meisten Details.

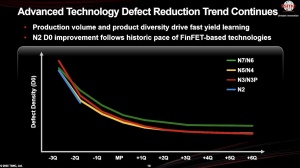

So soll die Defect Density (D0) für N2 auf Niveau der Vorgänger liegen. D0 ist ein Indikator für Defektrate, welche bei einer gewissen Chipgröße ermittelt wird und die nicht zwangsläufig mit den Zahlen anderer Fertiger wie zum Beispiel Intel verglichen werden kann. Da TSMC ab der zweiten Jahreshälfte 2025 mit der Massenproduktion in N2 beginnen möchte, legte man einen Graphen vor, der die Defektrate für die zwei vorherigen Quartale im Vergleich zur Defektrate von N3/N3P, N4/N5 und N6/N7 zum gleichen Entwicklungszeitpunkt darlegen soll. Demnach liegt die Fertigung in N2 derzeit auf Niveau von N4/N5.

N2 bietet gegenüber N3E eine um 18 % höhere Leistung bei gleicher Leistungsaufnahme, eine um 36 % geringere Leistungsaufnahme bei gleichem Takt, eine um 20 % höhere Transistordichte für Logikeinheiten und 15 % für den gesamten Chip. Dies liegt vermutlich daran, dass die Dichte für SRAM und analoge Komponenten nicht so stark gesteigert werden konnte. Für einen SRAM mit 256 MB soll die Ausbeute bei mehr als 90 % liegen.

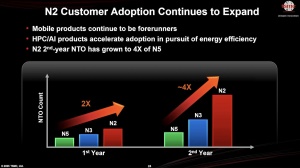

Die ersten Kunden für die Chips aus der N2-Fertigung werden die SoC-Auftraggeber und hier allen voran Apple sein. Große Chips, wie die für GPUs und KI-Beschleuniger, werden sicherlich auf die Varianten N2P und N2X warten, die für HPC-Anwendungen ausgelegt sind. N2P soll in der zweiten Jahreshälfte 2026 folgen und zusätzliche Leistungs- und Effizienzsteigerungen vorzuweisen haben. N2X wird dann ab 2027 noch einmal etwa 10 % höhere Taktraten ermöglichen.

Durch die enormen Verbesserungen in der N2-Fertigung und die ohnehin starke Nachfrage geht TSMC davon aus, dass man deutlich mehr Kunden für eine Fertigung in N2 wird gewinnen können.

Nach dem etwas holprigen Start von N3 sollen die Varianten N3X, N3A und N3C ebenfalls deutlich an Volumen hinzugewinnen. N3E befindet sich aktuell in der Massenproduktion und wird von zahlreichen Kunden bereits verwendet, bzw. angefragt. Die Fertigung in N3P ist im vierten Quartal 2024 gestartet und wird sukzessive die N3E-Fertigung ersetzen. N3X wird für Client-CPUs (allen voran die CCDs von AMD) verwendet werden, während N3A eine auf den Automotive-Bereich ausgelegte Variante ist. Mit N3C will TSMC die eher kostenbewussten Kunden anlocken

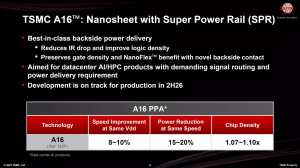

A16 läuft parallel mit N2-Optimierungsschritten

Aber TSMC ließ es sich nicht nehmen, zumindest einen ersten Eindruck dessen zu vermitteln, was Kunden von der Fertigung in A16 erwarten können. Neben den Nanasheets soll erstmals ein Backside Power Delivery Network (BSPDN) namens Super Power Rail (SPR) zum Einsatz kommen. Mit 16A adressiert TSMC KI- und HPC-Chips, die von der rückseitigen Versorgung aufgrund der höheren Effizienz und Signalintegrität profitieren.

Im Vergleich zu N2P soll A16 eine um 8 bis 10 % höhere Leistung vorzuweisen haben. Die Leistungsaufnahme soll bei gleicher Leistung um 15 bis 20 % zurückgehen. Bei der Transistordichte fallen die Fortschritte etwas geringer aus. Hier geht TSMC von 7 bis 10 % aus.