Werbung

Auf dem Technology Symposium 2022 hat TSMC seine Roadmap für die Fertigung in den kommenden drei Jahren offengelegt. Für diese wird der Grundbaustein die Fertigung in 3 nm sein. Um auf die Anforderungen der Kunden besser eingehen zu können und die Wegstrecke bis zur Nutzung von Nanosheets überbrücken zu können, wird es neben N3 noch vier weitere Fertigungsschritte in der 3-nm-Klasse geben.

Eine moderne Fertigung wird immer komplexer und somit auch teurer. Dementsprechend strecken Auftragsfertiger und Halbleiterhersteller mit eigener Fertigung die großen Entwicklungsschritte über einen größeren Zeitraum und versuchen durch verschiedene Maßnahmen die Lebensdauer einer Fertigung zu verlängern. Natürlich ist nicht jeder Kunde bereit oder hat die Möglichkeiten, immer gleich auf die neuste Fertigung zu wechseln. Daraufhin will TSMC sein Angebot in den kommenden Jahren auslegen.

Neben der bereits angelaufenen Fertigung in 3 nm wird TSMC über die Jahre 2023, 2024 und 2025 hinweg die Fertigungen in N3E, N3P, N3S und N3X anbieten. Die Fertigung in N3 soll in der zweiten Jahreshälfte 2022 in die High Volume Manufacturing (HVM) übergehen, so dass 2023 mit den ersten Chips zu rechnen ist. Kunden sind solche, die aus den verschiedensten Gründen immer gerne die aktuellste Fertigung nutzen, um die PPA-Vorteile (Performance, Power, Area) mitzunehmen und die bereit sind, den entsprechenden Preis dafür zu zahlen. Apple wäre hier ein möglicher Kandidat.

Bereits vor einiger Zeit vorgestellte wurde N3E. Die Fertigung in N3E soll Verbesserungen in Performance und/oder eine reduzierte Leistungsaufnahme bieten. Die Transistordichte kann hier allerdings nicht in der Form erhöht werden, dass dies ein wichtiger Vorteil von N3E gegenüber N3 wäre. Die Risiko-Produktion erster Chips in N3E soll in den kommenden Wochen starten. Die HVM wird für Mitte 2023 erwartet.

N3S und N3X als Speziallösungen

N3P wird die Performance-optimierte Variante von N3 werden, während N3S in Sachen Transistordichte weitere Verbesserungen bieten soll. Genauere Details nennt TSMC hier nicht, bis N3P und N3S in 2024 zur Verfügung stehen, vergeht aber auch noch einige Zeit.

Analog zu N4X, eine Performance-Variante von N4, wird es auch eine Fertigung in N3X geben. Die X-Varianten ermöglichen hohe Kollektor-Ströme und hohe Spannungen – sind somit auf Hochleistungschips optimiert, bei denen die Leistungsaufnahme eine untergeordnete Rolle spielt. Auch zu N3X gibt es noch keine Angaben zum Leistungsplus oder dergleichen.

FinFlex-Technologie

Als wäre das Angebot aus N3, N3E, N3S, N3P und N3X noch nicht genug, stellt TSMC mit der FinFlex-Technologie noch eine weitere Möglichkeit vor, die Fertigung auf die spezifischen Bedürfnisse des Auftraggebers anzupassen. Dies geschieht für Großkunden ohnehin, denn werden hier mehrere tausend Wafer mit hunderttausenden Chips bestellt, arbeiten TSMC und der Kunde im Rahmen der Fertigung an einer maßgeschneiderten Lösung, die NVIDIA und AMD dann einen speziell auf sie angepassten Prozess nennen.

Die FinFlex-Technoloie soll ähnlich funktionieren und es dem Kunden erlauben, einen Fertigungsschritt noch genauer auf die eigenen Bedürfnisse auszulegen.

Ein moderner Prozessor wird längst nicht mehr aus einer Art Transistor gefertigt. Es gibt sogenannte Bibliotheken für den Logik-Bereich, die auf eine hohe Leistung/Taktfrequenz bei möglichst niedriger Leistungsaufnahme ausgelegt sind und solche für den SRAM und die Caches, die eine hohe Packdichte der Transistoren aufweisen sollen.

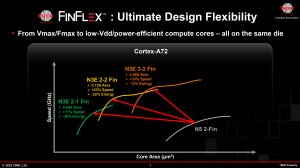

TSMC beschreibt die FinFlex-Technologie anhand der N3E-Fertigung. N3E 2-1 Fin hat das größte Einsparpotenzial für die Fläche und die Leistungsaufnahme, bietet aber nur ein geringes Leistungsplus. N3E 2-2 Fin hingegen beschreibt einen Mittelweg in der PPA-Kurve. Schlussendlich gibt es noch N3E 3-2 Fin, wo die Packdichte der Transistoren am geringsten ist, das Einsparpotential für die Leistungsaufnahme ebenso, dafür die Leistung am höchsten ausfällt.

Obiges Schaubild veranschaulicht den Aufbau eines SoCs unter Verwendung verschiedener Bibliotheken. Für die Performance-Kerne kommen die 3-2-FinFETs zum Einsatz, für die Efficiency-Kerne 2-2-FinFETs und für die weiteren IP-Blöcke im SoC (I/O, etc. pp.) 2-1-FinFETs mit besonders niedriger Leistungsaufnahme.

N2 als nächstes großes Ziel

Für 2024/2025 zielt TSMC auf den Wechsel von den FinFETs auf GAA-Transistoren ab. Das Nanosheet-Design scheint hier für TSMC die primäre Form der Umsetzung eines GAA-Transistors zu sein. Details nennt man noch nicht, aber genau wie bei Intel und Samsung werden mit dem Einsatz eines neuen Transistortyps Änderungen im Aufbau des Chips einhergehen. Burried Power Rails, also die Strom- und Spannungsversorgung der Transistoren, sind hier das Stichwort – bei Intel als PowerVia bezeichnet. Aber damit steigt nicht nur die Komplexität der Transistoren als solches, sondern die gesamte Fertigung und das Wafer-Handling werden deutlich schwieriger. Details dazu werden in den kommenden Jahren erwartet.

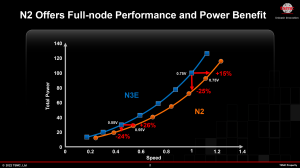

Für N2 will TSMC im Vergleich zu N3E die Leistungsaufnahme um 25 bis 30 % reduzieren. Die Performancen soll um 15 bis 26 % steigen. Zugleich peilt TSMC eine Packdichte der Transistoren um den Faktor 1,1 an. Dies klingt nach extrem wenig, wenngleich man hier schon gegen die optimierte Fertigung in N3E vergleicht. Allerdings sei auch erwähnt, das TSMC bei diesen Zahlen einen Mix aus 50 % Logik-Bereichen, 30 % SRAM und 20 % analogen Komponenten angibt. Vor allem der Analogbereich ließ sich auch in den aktuellen Fertigungsschritten kaum noch kleiner gestalten. Dies relativiert die Angabe zum Faktor 1,1 für die Packdichte etwas.