Werbung

Kaum ein Thema hat in der vergangenen Woche die Berichterstattung bei den PC-Komponenten derart dominiert, wie die neuen Ryzen-7000X3D-Prozessoren. Bisher hatten wir den Ryzen 9 7950X3D im Test, ein Ryzen 9 7900X3D ist im Zulauf und den Ryzen 7 7800X3D schauen wir uns aktuell in simulierter Form an, denn er wird erst Anfang April erhältlich sein.

Aus technologischer Sicht ist das Package der Ryzen-7000X3D-Prozessoren ein echtes Highlight. Mit der Chiplet-Strategie hat sich AMD in weiten Teilen Vorteile verschafft, die sich von den Desktop- bis hin zu den Server-Prozessoren ziehen. Die Ryzen-Prozessoren bieten einen zentralen IOD sowie bis zu zwei CCDs mit den eigentlichen Zen-4-Kernen. Auf einem der CCDs kommt nun noch der 3D V-Cache hinzu, der in Form eines SRAM-Chips auf dem Compute-Chiplet sitzt. TSVs verbinden den SRAM-Chip mit dem CCD.

Nun hat AMD gegenüber TomsHardware einige Details zum SRAM-Chip verraten. Dieser wird genau wie der SRAM-Chip der ersten Generation in 7 nm gefertigt. Die Größe des Chips liegt bei 36 mm². In der ersten Generation soll er noch 41 mm² bemessen haben, wenngleich AMD während der ersten Präsentation des 3D V-Cache im Juni 2021 schon von 36 mm² sprach. Die Anzahl der Transistoren ist mit 4,7 Milliarden identisch. Mit einer Transistordichte von etwas mehr als 130 Millionen Transistoren pro Quadratmillimeter ist der SRAM-Chip extrem dicht gepackt. Allerdings kann für solche reinen SRAM-Chips eine gut optimierte Fertigung angewendet werden.

| 1. Generation des 3D V-Cache | 2. Generation des 3D V-Cache | |

| Chipgröße | 41 mm² *1 | 36 mm² |

| Anzahl der Transistoren | 4,7 Milliarden | 4,7 Milliarden |

| Transistorendichte | 114,6 Millionen/mm² | 130,6 Millionen/mm² |

| Einsatz in | Ryzen 7 5800X3D Milan-X | Ryzen 7 7000X3D Genoa-X *2 |

*1: AMD machte bereits 2021 für die erste Generation die Angaben von 36 mm².

*2: Noch nicht offiziell vorgestellt

AMD hat die Bandbreite zwischen dem CCD- und dem SRAM-Chip ebenfalls erhöht. Ausgehend von 2 TB/s für die erste Generation der 3D-V-Cache-Umsetzung sollen es nun 2,5 TB/s sein. Diese 2,5 TB/s sind auch in unserem Messungen zur Cache- und Speicherbandbreite zu erkennen.

Da der CCD durch die Änderung der Fertigung vom 7 auf 5 nm von 80,7 mm² auf 66,3 mm² geschrumpft ist, muss AMD auch einige Änderungen im Placement der TSVs vornehmen. In der ersten Generation der 3D-V-Cache-Umsetzung führt AMD die TSVs für die Signale und Power/Control allesamt im Bereich des L3-Caches auf dem CCD aus. Durch die Verkleinerung des CCD muss AMD die TSVs anders platzieren. Die TSVs für das Signaling befinden sich weiterhin Bereich des L3-Caches. Die für Power/Control sind in den Bereich des L2-Cache gewandert.

Durch weitere Optimierungen soll der Bereich der TSVs in den CCDs auf Basis von Zen 4 in etwa 50 % kleiner ausfallen, das dies beim CCD auf Basis von Zen 3 der Fall war.

Die Auswirkungen aller Verbesserungen mögen sich in den Ryzen-7000X3D-Prozessoren positiv auf die Leistung auswirken, isolieren lassen sich aber nicht gut darstellen. Einzig die Messungen zur Cache- und Speicherbandbreite zeigen eine Verbesserung auf. Alles andere geht mit in die Leistung auf.

Neue Informationen zum IOD

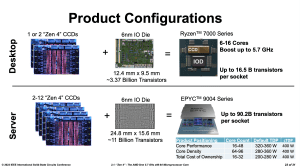

Im Rahmen der International Solid-State Circuits Conference 2023 hielt AMD eine Präsentation zur Zen-4-Architektur und veröffentlichte darin einige Informationen zum IOD für die Ryzen- und EPYC-Prozessoren. Die Größe und Anzahl der Transistoren für den cIOD, also die Variante wie sich bei den Ryzen-Prozessoren zum Einsatz kommt, kennen wir bereits. Nun kommen die Informationen zum sIOD, der Server-Variante, hinzu.

Der IOD der Ryzen-Prozessoren (cIOD) ist von der Ryzen-5000- auf die Ryzen-7000-Serie von 117,8 mm² auf 125 mm² sogar in der Größe angewachsen – und das obwohl die Fertigung von 12 auf 6 nm geändert wurde. Aber das Hinzufügen einer integrierten Grafikeinheit dürfte hier ebenso eine Rolle spielen wie einige weitere I/O-Funktionen, die hinzugekommen sind.

| Die-Größe | Transistoren | |

| sIOD (Rome) | 416 mm² | 8,34 Milliarden |

| sIOD (Milan) | 416 mm² | 8,34 Milliarden |

| sIOD (Genoa) | 383,9 mm² | 11 Milliarden |

Für den Server-IOD (sIOD) findet ebenfalls ein Wechsel in der Fertigung statt. Von 12 geht es auch hier auf 6 nm. Die Chipgröße sinkt hier allerdings von 416 mm² auf 383,9 mm². Die Anzahl der Transistoren steigt allerdings von 8,34 Milliarden auf 11 Milliarden Transistoren an.

Ryzen aktuell ohne Option auf drei CCDs

Im Vorfeld der Ryzen-7000-Prozessoren gab es immer wieder Gerüchte zu einer möglichen Variante mit drei CCDs. Damit hätte AMD bis zu 24 Kerne auf den Desktop bringen können. Bei den Ryzen-9-Modellen wurde aber recht schnell klar, dass die Leistungsaufnahme bereits jetzt ein limitierender Faktor ist. Mit acht zusätzlichen Kerne hätte sich diese Situation nicht weiter verbessert – eher im Gegenteil.

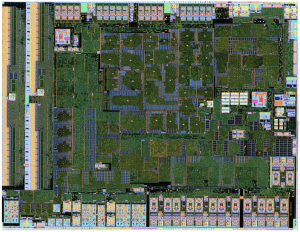

Der Die-Shot des cIOD zeigt zudem nun eindeutig auf, dass AMD hier nur zwei GMI3-Links vorgesehen hat (oben mittig) und demnach nur zwei CCDs an den cIOD anbinden kann. Damit dürften die Gerüchte zu einem Ryzen-Prozessor mit drei CCDs zumindest in dieser Generation ausgeräumt sein.