I just got an mdie 8200 kit Hoping it would get me 8400 stable in VT3 but just like Adie it ended up hard walling at 8200. I have mrc fast boot enabled. I touched CPU SA tx and mc as well as dimm voltages and plls. Nothing has helped. Any suggestions as to what I should try next? It works perfectly at 8200. Just won't even pass one cycle vt3 at 8400. My mc SP is 89.

Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: this_feature_currently_requires_accessing_site_using_safari

-

Hardwareluxx führt derzeit die Hardware-Umfrage 2025 (mit Gewinnspiel) durch und bittet um eure Stimme.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

[Sammelthread] Intel DDR5 RAM OC Thread

- Ersteller even.de

- Erstellt am

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Hmmmm.Ich komme darauf weil du hier einfach und oft etwas auf den Tisch legst, und so soll das dann sein und Punkt.

Sehe ich auch so. Ohne Kommentare bzw Herleitung.Das Niveau war schon mal besser hier

Wenn es das ist was ihr fühlt. Schade;

Es scheint wohl wirklich daran zu liegen dass man Probleme hat die Texte zu folgen oder gezielt skippt.

Kann sein. Die Anschuldigungen wären für mich weiterhin unerklärlich.

Es kann sein, dass man darauf kommt dank dem erneuerten zusammengefassten wiederholen von schon alter und detailerter Information.

Welche wohl mittlerweile 25-30 Pages zurück sitzt.

Es kann auch sein dass man zwar versucht gefiltert danach zu suchen, aber dem Forum hier "Show message from user only" , sowie eine Bildliche Previews bei der "Gepostete Nachrichten von X" fehlt.

Welches die Bildliche Suche von Visueller Infromation erschwert ... und nun wöglich diese Frust verstärkt.

Dank beidem sehe ich zwar eine Möglichkeit der Pragmatik

// Für mich ja ebenso lästig alte Posts zu suchen um diese als Quote darzulassen. Würde mir Zeit ersparren anstelle des erneuerten wiederholen und wiederholen von alter Information.

Allerdings tue ich mir sehr schwer zu verstehen weswegen man andere für die Bestätigung eigener Sorgen, nun ... in den Topf werfen möchte.

Nur wie gesagt,

Das Problem des nicht gezielten Fragen

Und die Generalizisierung der Masse aka "das Niveau" abgeleitet mittels eigener Unzufriedenheit

~ liegt leider weiterhin bei euch.

So ungern ich auch zu diesem Entschluss komme,

Ich verstehe nicht weswegen man sich darüber beschwert nicht wiederholt und wiederholt alles in die Wiege zu bekommen, oder andere (Gäste in diesem Forum) dafür Beschuldigt dass kein "Writeup" dafür exisitiert.

Es kann an der eigenen Frusst liegen, jedoch habe ich es weiterhin schwer zu verstehen weswegen man andere für seine eigene fehlende Zeit anschuldigt.

Ich von mir aus weiß genau dass ich Sachen zuu detailiert erkläre weswegen die Posts für viele zuu lang sind. (Aus Erfahrung von ehmaligen Beschwerden)

Und sobald man gezielt kurz und zusammengefasst schreibt, ist es zuu schwer abzuleiten.

Gezielte Fragen ? jedoch sehe ich keine.

Ja, das kann sein~

Wenn man unbedingt seine Sources suchen möchte, dann empfehle ich wie schon 1x erwähnt,

Forschungsdokumente auf IEEE sich durchzulesen; (im Durchschnitt 180-200 Seiten Lang)

Im süd-östlichen Raum auf Chinesich und Koreanisch nach der Information zu suchen;

Oder einfach als Individum schwerer zu arbeiten, sodass man seine Arbeit im gegenzug zu information austauschen kann.

Mit alleinigem beschweren, wird es nichts.

Please work harder and actively research~

Übrigens, Guten Morgen~

Zuletzt bearbeitet:

zebra_hun

Profi

Veii, ich lese gerne immer dein "Teacher" Linie.

Man lernt immer neues.

Danke

~Morgen!

Man lernt immer neues.

Danke

~Morgen!

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

@ceti (danke), jedoch @torti

www.hardwareluxx.de

~ RAS [EN]

www.hardwareluxx.de

~ RAS [EN]

https://www.hardwareluxx.de/community/threads/intel-ddr5-ram-oc-thread.1306827/post-30210600 [EN] Mem-Spannungen 1/X

www.overclock.net

[EN] ODT, RTT, Training

www.overclock.net

[EN] ODT, RTT, Training

www.hardwareluxx.de

[EN] Training , tWR, tWTR, tWRWR

www.hardwareluxx.de

[EN] Training , tWR, tWTR, tWRWR

www.hardwareluxx.de

[EN] tFAW & Pagesize

www.hardwareluxx.de

[EN] tFAW & Pagesize

www.hardwareluxx.de

[EN] VRef, VDDQ delta , RTL ~ work suggestions

www.hardwareluxx.de

[EN] VRef, VDDQ delta , RTL ~ work suggestions

www.hardwareluxx.de

[GER] MemBurst, WR-WR, RD-RD

www.hardwareluxx.de

[GER] MemBurst, WR-WR, RD-RD

www.hardwareluxx.de

[EN] Guardbands, Fixed voltage is bad, V/F Curve Part 1/X

www.hardwareluxx.de

[EN] Guardbands, Fixed voltage is bad, V/F Curve Part 1/X

www.hardwareluxx.de

[EN] RAS, RCD, Wr & Rd

www.hardwareluxx.de

[EN] RAS, RCD, Wr & Rd

www.hardwareluxx.de

[EN] SVID, Vout, V/F Tuning

www.hardwareluxx.de

[EN] SVID, Vout, V/F Tuning

www.hardwareluxx.de

[EN] More V/F Curve Tuning ~ practical

www.hardwareluxx.de

[EN] More V/F Curve Tuning ~ practical

[GER] Hynix Class A/V ?

[GER] Hynix Class A/V ?

www.hardwareluxx.de

[GER] Was ist SNR, Mem-Spannungen tuning, Was ist ODT, RTT?

www.hardwareluxx.de

[GER] Was ist SNR, Mem-Spannungen tuning, Was ist ODT, RTT?

www.hardwareluxx.de

[EN] 8nCK ?, Mem als Kinderbuch, Kühlschrank Beispiel

www.hardwareluxx.de

[EN] 8nCK ?, Mem als Kinderbuch, Kühlschrank Beispiel

www.overclock.net

[EN] RAS & Mem als Kinderbuch, Elevator Example

www.overclock.net

[EN] RAS & Mem als Kinderbuch, Elevator Example

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht. Was hat es mit RRD & WTR aufsich

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht. Was hat es mit RRD & WTR aufsich

www.hardwareluxx.de

[GER] Timings zu niedrig ?

www.hardwareluxx.de

[GER] Timings zu niedrig ?

www.hardwareluxx.de

[GER] Wie testet man timings, wieso skallieren meine Timings nicht 2/3

www.hardwareluxx.de

[GER] Wie testet man timings, wieso skallieren meine Timings nicht 2/3

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht Part 3/4

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht Part 3/4

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht 4/4

www.hardwareluxx.de

[GER] Wieso skallieren meine Timings nicht 4/4

www.overclock.net

[EN] What is CPU leakyness ? What does MC-SP factor in ?

www.overclock.net

[EN] What is CPU leakyness ? What does MC-SP factor in ?

www.hardwareluxx.de

[GER] ASUS RTL Training. DQS über RAM ?, CCDL ?, _DD & _DR minimums

www.hardwareluxx.de

[GER] ASUS RTL Training. DQS über RAM ?, CCDL ?, _DD & _DR minimums

www.hardwareluxx.de

[GER] tWPRE , Weitere SC, SD/DD, DR, SC_Long erklärung, RDRD _SG erklärung

www.hardwareluxx.de

[GER] tWPRE , Weitere SC, SD/DD, DR, SC_Long erklärung, RDRD _SG erklärung

www.hardwareluxx.de

[GER] VDDQ, VDDQ Distanz, Thermal-Scaling ~ Superconductor ?

www.hardwareluxx.de

[GER] VDDQ, VDDQ Distanz, Thermal-Scaling ~ Superconductor ?

www.hardwareluxx.de

[EN] Memory Voltages Cheatsheet , Meanings explained, PMIC ?

www.hardwareluxx.de

[EN] Memory Voltages Cheatsheet , Meanings explained, PMIC ?

www.hardwareluxx.de

[GER] tWR, tWTR, Writes ?

www.hardwareluxx.de

[GER] tWR, tWTR, Writes ?

... usw und so fort~

Bei jeglichem Respekt . . .

Was erwartest du von mir ?

Dass vieles auf englisch ist, ist nun ja ~ defacto der Standart in 2024.

Alternative Weltsprachen wären Chinesisch oder Russisch. Russisch kann ich nur lesen und verstehen.

Mandarin noch am lernen.

Wenn man auf deutsch Fragt, bekommt man eine deutsche Antwort. Bei englisch wäre die Antwort englisch.

Mir, wessen Posts er nicht nur dank Linebreaks in Chunks unterteilt um einfachereres Auffassen zu garantieren

Sondern auch fehlende Erklärungen zu unterstellen,

Ist einfach nur Abenteuerlich mit Foundation einer schlechten Laune

Sollte die Motivation exisiteren , so findet man was man möchte

Der Rest liegt bei dir/euch.

Arbeite hart , diszipliniert und wenn interesse besteht, findet man seine Antwort auf seine Fragen.

Irgendwo im Netz wird sie schon zu finden sein 🤭

PS ~ Die Informationen oben wurde hier vor 50-60 Seiten gepostet.

Mir halt fehlende Arbeit bzw fehlende Erklärungen zu unterstellen ~ finde ich mehr als nur Abenteuerlich

Wenn, dann bin ich eher überarbeitet für wortwörtlich Lau. Ich hab absolut nichts davon meine Zeit hier zu Investieren.

Diese 900 Posts Ziffer, 400 davon gehören diesem Forum und fast alles davon diesem Thread.

EDIT:

Bitte bekomme nicht die 3% in unserer Economy welche den Tag anderer verschlechtern.

Tut mir leid dass du an mir zweifelst~~

Aber genauer erklärt habe ich es schon mehrere Male 🤭

[Sammelthread] - Intel DDR5 RAM OC Thread

Sind sicher 60-70h testen drin Y-cruncher ? Zuu hohe PLL = CPU debug 00h ASUS & ASRock sowie MSI? , benutzen ganzzahlige Werte. Keine Offsets. Unsicher bei EVGA, Gigabyte und Biostar. Ein Board welches auf PLLs angesetzt ist, bzw diese nicht selbstständig beim Training korrigiert; Ist ein...

https://www.hardwareluxx.de/community/threads/intel-ddr5-ram-oc-thread.1306827/post-30210600 [EN] Mem-Spannungen 1/X

*Official* Intel DDR5 OC and 24/7 daily Memory Stability...

[Sammelthread] - Intel DDR5 RAM OC Thread

Sind sicher 60-70h testen drin Y-cruncher ? Zuu hohe PLL = CPU debug 00h ASUS & ASRock sowie MSI? , benutzen ganzzahlige Werte. Keine Offsets. Unsicher bei EVGA, Gigabyte und Biostar. Ein Board welches auf PLLs angesetzt ist, bzw diese nicht selbstständig beim Training korrigiert; Ist ein...

[Sammelthread] - Intel DDR5 RAM OC Thread

Sind sicher 60-70h testen drin Y-cruncher ? Zuu hohe PLL = CPU debug 00h ASUS & ASRock sowie MSI? , benutzen ganzzahlige Werte. Keine Offsets. Unsicher bei EVGA, Gigabyte und Biostar. Ein Board welches auf PLLs angesetzt ist, bzw diese nicht selbstständig beim Training korrigiert; Ist ein...

[Sammelthread] - Intel DDR5 RAM OC Thread

Nicht schwer zu verstehen eigentlich, eintragen und auslesen ist etwas anderes als das was der Controller bzw. die Intel CPU tatsächlich macht mit den Werten. Die tRTP ist ebenfalls ein schlechtes Beispiel. da kann man auch eintragen was man möchte der valide Wert ist für jede Intel CPU bei DDR5...

[Sammelthread] - Intel DDR5 RAM OC Thread

@ captn1ko ....lass mal Geekbench 3 mit den 8600er Setting laufen und sag mal was bei dem Memory-Scrore raus kommt ? kann ich heute mal machen :) Karhu lief durch @8600 CL38

[Sammelthread] - Intel DDR5 RAM OC Thread

@ captn1ko ....lass mal Geekbench 3 mit den 8600er Setting laufen und sag mal was bei dem Memory-Scrore raus kommt ? kann ich heute mal machen :) Karhu lief durch @8600 CL38

[Sammelthread] - Intel DDR5 RAM OC Thread

Class A, A-Dies können ~8400-9000 je nach binning. Alle können 8000MT/s // OEM Green Class V A-Dies beginnen timing Probleme ab 7800MT/s zu bekommen. Sorry, Schwartz, aber egal denke ich. Ich werde irgendwann den Kühler abbauen. Vielleich ich habe etwas falsch gebaut. Ich habe noch einen...

[Sammelthread] - Intel DDR5 RAM OC Thread

Gibts die Excel irgendwo zum Download? And OC Tool, too. I can't find... Thanks

[Sammelthread] - Intel DDR5 RAM OC Thread

Gibts die Excel irgendwo zum Download? And OC Tool, too. I can't find... Thanks

[Sammelthread] - Intel DDR5 RAM OC Thread

Es gibt auch eine verbesserte Version von HCI : RunMemtestPRO ( RunMemtestPRO 7.0 + DANGWANG 1.0 ) Ich weiss auch nicht so richtig das mit Karhu,...Karhu ist von ~ 2018 ...und ob das so richtig passt zu den neuen Systeme ??? Erklär mir mal lieber einer warum die tester in Fernost immer nur...

[Sammelthread] - Intel DDR5 RAM OC Thread

mhmhm ,, seit wann sind die 9000 gefallen ? https://www.overclock.net/threads/official-asus-strix-maximus-z790-owners-thread.1800191/post-29277243 24°C max 😆

AMD DDR5 OC And 24/7 Daily Memory Stability Thread

[Sammelthread] - Intel DDR5 RAM OC Thread

Hat hier eigentlich jemand die 2x24Gb M-dies mit 8400+ stable bekommen?/ Tue mich schon schwer mit 8200mhz CL 38 😵💫 Momentan 1.5v MC, 1.3 SA, 1.47v VDD, 1.45v VDDQ, 1,4 TX für 8200mhz. Wie hoch kann man mit der MC voltage gehen für 24/7 Betrieb? Ich, bis jetzt seit 2 Wochen mit meinem...

[Sammelthread] - Intel DDR5 RAM OC Thread

Oki ganz einfach holzi die Sache aus dem Weg zu räumen. Wir hätten gerne einen 4036% karhu Run von dir mit allen Infos auf dem Screen Oki? Mit welchem Takt den jetzt?

[Sammelthread] - Intel DDR5 RAM OC Thread

Oki ganz einfach holzi die Sache aus dem Weg zu räumen. Wir hätten gerne einen 4036% karhu Run von dir mit allen Infos auf dem Screen Oki? Mit welchem Takt den jetzt?

[Sammelthread] - Intel DDR5 RAM OC Thread

Oki ganz einfach holzi die Sache aus dem Weg zu räumen. Wir hätten gerne einen 4036% karhu Run von dir mit allen Infos auf dem Screen Oki? Mit welchem Takt den jetzt?

[Sammelthread] - Intel DDR5 RAM OC Thread

Oki ganz einfach holzi die Sache aus dem Weg zu räumen. Wir hätten gerne einen 4036% karhu Run von dir mit allen Infos auf dem Screen Oki? Mit welchem Takt den jetzt?

[OFFICIAL] Asus Strix/Maximus Z790 Owners Thread

[Sammelthread] - Intel DDR5 RAM OC Thread

"Das Produkt reift beim Kunden" ist ja nix neues. Trotzdem frech womit so geworben wird und wie es in der Praxis wirklich ausschaut

[Sammelthread] - Intel DDR5 RAM OC Thread

"Das Produkt reift beim Kunden" ist ja nix neues. Trotzdem frech womit so geworben wird und wie es in der Praxis wirklich ausschaut

[Sammelthread] - Ryzen DDR5 RAM OC Thread

Das teste ich gleich morgen Abend mal und gebe dir Bescheid. Und wenn wir es ohne GDM zum laufen kriegen, gebe ich dir einen aus :) @z3r0.c0m , kannst du bitte hier öffentlich Updates darlassen ? Ich bin ungerne Techsupport und weitaus weniger gern helfe ich Privat. Keine techsupport PMs...

[Sammelthread] - Ryzen DDR5 RAM OC Thread

Etwas zu viel :d Danke dir :) Findest du es selber zuu viel ? Ja ist aber ein ziemliches Gefummel das richtig hinzubekommen ( oder ich weiß noch nicht wie ).

[Sammelthread] - Ryzen DDR5 RAM OC Thread

Habe mal beobachtet, dass der CPU Test vom TimeSpy schwer unter IF Fehlercorrektur leidet. Müsste mal einer Verifizieren : ) Was bedeutet "leiden"? Ich hatte dort immer sehr konstante CPU Werte von 18.500 - 18.800. 1705241798 sollte dann PyPrime aber nicht derbe schwanken? 1705237059 VSoC...

... usw und so fort~

Was erwartest du von mir ?

Dass vieles auf englisch ist, ist nun ja ~ defacto der Standart in 2024.

Alternative Weltsprachen wären Chinesisch oder Russisch. Russisch kann ich nur lesen und verstehen.

Mandarin noch am lernen.

Wenn man auf deutsch Fragt, bekommt man eine deutsche Antwort. Bei englisch wäre die Antwort englisch.

Mir, wessen Posts er nicht nur dank Linebreaks in Chunks unterteilt um einfachereres Auffassen zu garantieren

Sondern auch fehlende Erklärungen zu unterstellen,

Ist einfach nur Abenteuerlich mit Foundation einer schlechten Laune

Sollte die Motivation exisiteren , so findet man was man möchte

Der Rest liegt bei dir/euch.

Arbeite hart , diszipliniert und wenn interesse besteht, findet man seine Antwort auf seine Fragen.

Irgendwo im Netz wird sie schon zu finden sein 🤭

PS ~ Die Informationen oben wurde hier vor 50-60 Seiten gepostet.

Mir halt fehlende Arbeit bzw fehlende Erklärungen zu unterstellen ~ finde ich mehr als nur Abenteuerlich

Wenn, dann bin ich eher überarbeitet für wortwörtlich Lau. Ich hab absolut nichts davon meine Zeit hier zu Investieren.

Diese 900 Posts Ziffer, 400 davon gehören diesem Forum und fast alles davon diesem Thread.

EDIT:

Bitte bekomme nicht die 3% in unserer Economy welche den Tag anderer verschlechtern.

Tut mir leid dass du an mir zweifelst~~

Aber genauer erklärt habe ich es schon mehrere Male 🤭

Zuletzt bearbeitet:

Nichts. Du postest Zahlen oder Diagramme ohne wenigstens mal zu zeigen worauf bzw auf welchen Post diese sich beziehen. Das ist nicht immer so, aber es gibt Post's die beziehen sich auf Beiträge welche länger her sind. Mir ging es nur darum, das es auch User gibt die nicht so in der Materie drinn stecken, den Überblick behalten.

Das Du da gleich angepisst bist, war mir nicht klar.

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Angepisst war ich nie und bin ich nichtDas Du da gleich angepisst bist, war mir nicht klar.

Weder am morgen, noch zu Mittag, oder sogar momentan am Abend.

Man merkt es wenn man keine Smileys einfügt und der Text roh und kurz ist.

Auf anta's schreibweise oder auf hochdeutsch.

Dann ja. Definitiv.

Heute absolut nicht~

Lästig ist es, alles rauszusuchen. Aber angefressen oder angepisst, nein.

Enttäuscht ja. Aber habe schon schlimmeres auf OCN erlebt.

Da man sich nicht kennt und die andere Seite nicht verstehen wird weswegen man auf eine Entschuldigung warten würde.

Ist es unwichtig. Leben und leben lassen. 🤭

Infin1tum

Enthusiast

mach dir kein Kopf, es steckt einfach nicht jeder so tief in der Materie drin. Sind einfach unterschiedliche Niveaus die versuchen zu kommunizieren. Ich versteh auch nur die Hälfte aber mehr muss ich auch nicht verstehen. Deswegen bin ich nicht frustriert.

snakeeyes

Enthusiast

- Mitglied seit

- 02.12.2017

- Beiträge

- 4.360

- Details zu meinem Desktop

- Prozessor

- 13900k

- Mainboard

- MSI Unify-X z690

- Kühler

- MoRa IV 600 2xDDC 3.25pwm

- Speicher

- Acer Predator 6800@ 8200c34

- Grafikprozessor

- 4090

- Display

- LG 34GN850-B

- Soundkarte

- SoundblasterX G6

- Gehäuse

- Fractal Design Define S2 Vision RGB

- Netzteil

- Seasonic Prime 1000w px

- Betriebssystem

- W11

Wem es nicht passt, der kann es doch einfach überlesen oder ihn auf die Ignorliste setzen. Dann sieht man es auch nicht mehr.

Recht unverständlich warum man jemanden der helfen will so angeht. Ob es nun Zielführend ist oder nicht mit seiner Hilfestellung, aber er bietet sie an.

Wem die Art und weise nicht passt, einfach selber forschen und probieren .

.

Recht unverständlich warum man jemanden der helfen will so angeht. Ob es nun Zielführend ist oder nicht mit seiner Hilfestellung, aber er bietet sie an.

Wem die Art und weise nicht passt, einfach selber forschen und probieren

.

.Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Alles gut dankemach dir kein Kopf, es steckt einfach nicht jeder so tief in der Materie drin.

Nein nein

Weswegen man mir mit "entitlement" kommt wie ich meine Arbeit oder Schreibweise zu führen habe, ist schwer zu verstehen

Wäre ja nicht mal das erste mal hier im Thread.

Aber leben und leben lassen.

Man muss den Thread nicht mit beschwerden füllen.

Konstruktive Kritik ist ja total fein.

Aber man sollte nicht etwas von jemanden erwarten nur weil man selber ein Problem damit hat.

Ich möchte ja auch keinen ignorieren. Aber verständlich ist es mir nicht.

Beitrag automatisch zusammengeführt:

Wie kann ich das ausbessern ?Mir ging es nur darum, das es auch User gibt die nicht so in der Materie drinn stecken, den Überblick behalten.

Eine Idee ?

Ahm,Du postest Zahlen oder Diagramme ohne wenigstens mal zu zeigen worauf bzw auf welchen Post diese sich beziehen.

Ja - eine Forum Problematik

Aber ... bin ich schuld daran wie ich meine Posts führe ?

Oder ?

Bezahlt mich irgendwer dass ich hier als Reviewer tätig bin ?

Der Thread gehört ja ebenfalls nicht mir, um den Main Post zu Pflegen.

Jeder Nutzer hat auch seine eigenen Fragen und Erwartungen.

Wo kommst du hier ins Spiel , ich verstehe nicht. Forum-moderator ?

Ich möchte es verstehen

Wieso kümmert es dich wie ich schreibe

Oder wieso Fragst du nicht gezielt wenn etwas nicht verstanden wird ?

Ich möchte verstehen~

Verbesserungsvorschläge ?

Zuletzt bearbeitet:

X909

Urgestein

- Mitglied seit

- 27.06.2005

- Beiträge

- 4.860

- Desktop System

- X909

- Laptop

- M909

- Details zu meinem Desktop

- Prozessor

- 14900KS - 6.2 / 4.8 / 5.4 Ghz

- Mainboard

- ASUS Z790 Apex Encore, 1901

- Kühler

- Thermal Grizzly Mycro Direct-Die, Aquaduct XT 360 + 2x MoRa 360

- Speicher

- 2x24 GB G.Skill 8200 @ 8533 36-49-42-62 & scharfe Subtimings

- Grafikprozessor

- ASUS ROG Astral 5090 OC - Bykski watercooled, 720W PL

- Display

- Samsung PS64F8500 :D, Pimax 8kx, LG27UK850

- SSD

- 1 TB WD SN850X + 2x2 TB WD SN850X @ RAID0 + WD SN520 Müllhalde

- HDD

- 12 TB WD Elements Backupdrive

- Gehäuse

- Jonsbo U4 Plus Silver

- Netzteil

- Enermax PlatiGemini 1200W

- Betriebssystem

- Win 11 Pro

- Internet

- ▼600 MBit ▲120 MBit

Ist ein zweischneidiges Schwert... fachliche Expertise ist natürlich Gold wert und am Ende ist ein Forum Freizeit und niemand hier muss posten oder wird dafür bezahlt.

Aber ja... etwas strukturierter und kürzer würde ich auch besser nachvollziehen können. Or native language... but others might have their issues with english

Aber ja... etwas strukturierter und kürzer würde ich auch besser nachvollziehen können. Or native language... but others might have their issues with english

Braegnok

Profi

- Mitglied seit

- 22.01.2021

- Beiträge

- 103

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 7950X

- Mainboard

- Asus ROG Crosshair X670E Gene

- Kühler

- MO-RA3 420 Pro

- Speicher

- 48GB DDR5

- Grafikprozessor

- Nvidia RTX 3090 FE

- Display

- Asus PG32UQX

- SSD

- Crucial T700

- Gehäuse

- Primochill WetBench

- Netzteil

- SeaSonic Prime TX-1600

- Keyboard

- Keychron Q1 HE

- Mouse

- G502 Lightspeed

- Betriebssystem

- Windows 11 Pro 64-Bit

- Sonstiges

- http://www.3dmark.com/pcm10b/1944567

It's a double-edged sword... professional expertise is of course worth its weight in gold and in the end a forum is free time and nobody here has to post or gets paid for it.

But yes... I would be able to understand something more structured and shorter. Or native language... but others might have their issues with english

I'm on forums around the world and use Google Chrome with the Google Translate app. Setting up your language is very easy. Then simply right-click on the translate icon to translate the entire page

Zuletzt bearbeitet:

Furyos

Experte

- Mitglied seit

- 14.09.2017

- Beiträge

- 1.437

- Desktop System

- "Arbeit"srechner

- Details zu meinem Desktop

- Prozessor

- Ryzen 7 9800x3d

- Mainboard

- Asus Strix B650E ITX

- Kühler

- MSI MAG 360r

- Speicher

- Kingbank 2x24GB@6200 Cl30

- Grafikprozessor

- MSI RTX 2080 Ti

- Display

- Acer XV282KK

- SSD

- Samsung 2tb SSD

- Gehäuse

- Corsair 2000D

- Netzteil

- MSI 850W

- Betriebssystem

- Windows 11

Also ich würde hier erst mal Danke an Veii sagen für die ganze Zeit die er hier hilft und erklärt.

Für jemand der hier als Anfänger einfach mal reinschaut sind seine Posts viel Input und gehen sehr tief in die Materie. Entweder macht man sich die Mühe und versucht mit seinen Posts bzgl. der Regeln fürs OC etwas Eigenes hinzubekommen oder man kann hier die Beiträge von Usern anschauen die selbst ihre Ergebnisse inkl. Einstellungen gepostet haben ( die Pre Veii Ära 😄)

geizhals.de

geizhals.de

Für jemand der hier als Anfänger einfach mal reinschaut sind seine Posts viel Input und gehen sehr tief in die Materie. Entweder macht man sich die Mühe und versucht mit seinen Posts bzgl. der Regeln fürs OC etwas Eigenes hinzubekommen oder man kann hier die Beiträge von Usern anschauen die selbst ihre Ergebnisse inkl. Einstellungen gepostet haben ( die Pre Veii Ära 😄)

Beitrag automatisch zusammengeführt:

Also 8000@Cl38 habe ich zum Laufen gebracht. Kit ist folgendes:OK, nach Auswahl von Microcode 104 geht auch Undervolting 😁

G.Skill Trident Z5 RGB silber DIMM Kit 32GB, DDR5-7800 ab € 155,89 (2025) | Preisvergleich Geizhals Deutschland

✔ Preisvergleich für G.Skill Trident Z5 RGB silber DIMM Kit 32GB, DDR5-7800 ✔ Produktinfo ⇒ Typ: DDR5 DIMM 288-Pin, on-die ECC • Übertragung: 7800MT/s (7800MHz effektiv - abgeleitet von 3900MHz I/O… ✔ Speicher ✔ Testberichte ✔ Günstig kaufen

Anhänge

Zuletzt bearbeitet:

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Native is german, well bilingual.Or native language... but others might have their issues with english

English (polyglot) got more comfortable to call things by their name where globally you get understood. Maybe~

Danke und tut mir leid.( die Pre Veii Ära 😄)

Sobald Moderatoren sagen , englisch wäre hier nicht erwünscht ~ schaue ich mir gerne das Gras auf anderen Foren an.

Ich wäre hier auch nur aus reiner Freizeit und persönlichem Interesse.

Eigentlich war LUXX nur mein/unser RDNA Forschungsfelt mitsammt Igorslab.

Auf der Memory OCing Sektion hatte ich nichts verloren.

Bekannt war mir diese Community nur durch weitergeleitete screenshot zu den MemOC Discord Zeiten.

Da man aber von einem Mitglied hier ein Intel System geliehen bekaam, und ja mit großen (man helfe sich nicht) Beschwerden hier hin-und-her umsich warf

Musste ich entweder Ersatz leisten, oder zu meinen Worte stehen.

🙌Also 8000@Cl38 habe ich zum Laufen gebracht. Kit ist folgendes:

Du brauchst kein Delay auf tRDRD oder tWRWR einzufügen.

Solange du nicht RRDS über 8 stellst, muss auch Read to Read (2* CCDS, CCDS = RRDS) ~ nicht höher

Memory rennt auf 8nCK , doppeltem und dreifachen.

Bei 10nCK würde es im besten Fall abwarten, im schlimnsten Fall ein Cycle aussetzen.

Im aller schlimmsten Fall laufen andere gleichzeitig aktive Timings ab, und es gibt errors

tWRWR entweder doppelt oder gleich auf zu RDRD

Beide _DG (different bankgroup, short instant jump) wären auf den CCDS (der strobe) minimum. In dem Fall Wert 8.

Somit sind _SG (same group, roundtrip) auf tBurstLength . Der Strobe delay für eine komplette Aktion. Wert 16

Aber timings sind nicht soo wichtig,

solange du nichts abstraktes oder fehlerhaftes machst.

Well done !

Minimum REFI wäre 8192 (-1 da Bios Wert. Ziffer 0 ist auch ein Wert, decimal to binary translation)

REFI schritte wären somit

usw.

Bei 65536 wären das dann 65535 als Bios Wert.

Dafür hat der Controller ein Binary mapping.

Nicht jeder zufällig Wert, ist ein korrekter Wert.

Zuletzt bearbeitet:

X909

Urgestein

- Mitglied seit

- 27.06.2005

- Beiträge

- 4.860

- Desktop System

- X909

- Laptop

- M909

- Details zu meinem Desktop

- Prozessor

- 14900KS - 6.2 / 4.8 / 5.4 Ghz

- Mainboard

- ASUS Z790 Apex Encore, 1901

- Kühler

- Thermal Grizzly Mycro Direct-Die, Aquaduct XT 360 + 2x MoRa 360

- Speicher

- 2x24 GB G.Skill 8200 @ 8533 36-49-42-62 & scharfe Subtimings

- Grafikprozessor

- ASUS ROG Astral 5090 OC - Bykski watercooled, 720W PL

- Display

- Samsung PS64F8500 :D, Pimax 8kx, LG27UK850

- SSD

- 1 TB WD SN850X + 2x2 TB WD SN850X @ RAID0 + WD SN520 Müllhalde

- HDD

- 12 TB WD Elements Backupdrive

- Gehäuse

- Jonsbo U4 Plus Silver

- Netzteil

- Enermax PlatiGemini 1200W

- Betriebssystem

- Win 11 Pro

- Internet

- ▼600 MBit ▲120 MBit

I prefer to read original text.... such translations are not precise.Ich bin in Foren auf der ganzen Welt vertreten und verwende Google Chrome mit der Google Translate-App. Die Einrichtung Ihrer Sprache ist sehr einfach. Klicken Sie dann einfach mit der rechten Maustaste auf das Übersetzungssymbol, um die gesamte Seite zu übersetzen

Furyos

Experte

- Mitglied seit

- 14.09.2017

- Beiträge

- 1.437

- Desktop System

- "Arbeit"srechner

- Details zu meinem Desktop

- Prozessor

- Ryzen 7 9800x3d

- Mainboard

- Asus Strix B650E ITX

- Kühler

- MSI MAG 360r

- Speicher

- Kingbank 2x24GB@6200 Cl30

- Grafikprozessor

- MSI RTX 2080 Ti

- Display

- Acer XV282KK

- SSD

- Samsung 2tb SSD

- Gehäuse

- Corsair 2000D

- Netzteil

- MSI 850W

- Betriebssystem

- Windows 11

Um Gottes Willen, das war nicht negativ gemeint! Nicht viele konnten erläutern warum sie was verstellt haben und wie die Zusammenhänge sind.Native is german, well bilingual.

English (polyglot) got more comfortable to call things by their name where globally you get understood. Maybe~

Danke und tut mir leid.

Sobald Moderatoren sagen , englisch wäre hier nicht erwünscht ~ schaue ich mir gerne das Gras auf anderen Foren an.

Ich wäre hier auch nur aus reiner Freizeit und persönlichem Interesse.

Eigentlich war LUXX nur mein/unser RDNA Forschungsfelt mitsammt Igorslab.

Auf der Memory OCing Sektion hatte ich nichts verloren.

Bekannt war mir diese Community nur durch weitergeleitete screenshot zu den MemOC Discord Zeiten.

Da man aber von einem Mitglied hier ein Intel System geliehen bekaam, und ja mit großen (man helfe sich nicht) Beschwerden hier hin-und-her umsich warf

Musste ich entweder Ersatz leisten, oder zu meinen Worte stehen.

🙌

Du brauchst kein Delay auf tRDRD oder tWRWR einzufügen.

Solange du nicht RRDS über 8 stellst, muss auch Read to Read (2* CCDS, CCDS = RRDS) ~ nicht höher

Memory rennt auf 8nCK , doppeltem und dreifachen.

Bei 10nCK würde es im besten Fall abwarten, im schlimnsten Fall ein Cycle aussetzen.

Im aller schlimmsten Fall laufen andere gleichzeitig aktive Timings ab, und es gibt errors

tWRWR entweder doppelt oder gleich auf zu RDRD

Beide _DG (different bankgroup, short instant jump) wären auf den CCDS (der strobe) minimum. In dem Fall Wert 8.

Somit sind _SG (same group, roundtrip) auf tBurstLength . Der Strobe delay für eine komplette Aktion. Wert 16

Aber timings sind nicht soo wichtig,

solange du nichts abstraktes oder fehlerhaftes machst.

Well done !

Minimum REFI wäre 8192 (-1 da Bios Wert. Ziffer 0 ist auch ein Wert, decimal to binary translation)

REFI schritte wären somit

Anhang anzeigen 970321Anhang anzeigen 970322

usw.

Bei 65536 wären das dann 65535 als Bios Wert.

Dafür hat der Controller ein Binary mapping.

Nicht jeder zufällig Wert, ist ein korrekter Wert.

Bei den Timings habe ich (glaube ich zumindest) nur von CL36 auf 38 und TRas auf 84 runter, der Rest ist noch vom XMP Profil.

Schaue aber gerne mal ob ich deine Tipps anwenden kann ;-)

Es ist halt einfach nervig das jeder Error die kompletten custom settings zurücksetzt :-(

Glaube nicht dass ich das noch lange aushalte mit dem Colorful.

Zuletzt bearbeitet:

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Ah nur generell.Es ist halt einfach nervig das jeder Error die kompletten custom settings zurücksetzt :-(

Ja , sehr.

Wie kann man ein Bios ohne Biosprofile erstellen

F9, F10, STRG+F-iwas, muss doch gehen.

scewin bleibt dir dann noch übrig.

So kannst du dir die NVRAM (Profile) direkt von Wíndows aus reinladen.

AMI tools sind Proprietary - aber ich wette du kannst sie finden

vorsegenQq

Neuling

- Mitglied seit

- 12.02.2024

- Beiträge

- 2

Hallo, kann mir jemand helfen, zu verstehen, wie Degradierung geschieht auf der IMC, begann ich vor kurzem übertakten meinen Speicher und machte einen Fehler, indem Sie 1.8 von SA Spannung statt 1.18 und traf speichern Ausfahrt. Mein Board scheiterte beim POST und bootete im BIOS im abgesicherten Modus, ich stellte alles auf die Standardeinstellungen zurück, trainierte MC SP neu, es änderte sich nichts, also bootete ich in Windows und führte ein paar Tests mit der Standardfrequenz durch, alles scheint zu funktionieren, aber ich habe immer noch Angst, dass ich einen Schaden angerichtet habe...

Ich verstehe, dass dies eine sehr dumme Art von Fehler ist und ich könnte in den falschen Thread fragen, so werde ich sehr dankbar für jede Art von Beratung sein.

Ich verstehe, dass dies eine sehr dumme Art von Fehler ist und ich könnte in den falschen Thread fragen, so werde ich sehr dankbar für jede Art von Beratung sein.

Infin1tum

Enthusiast

Wenn der IMC was abgekommen hätte, dann hättest dus schon gemerkt. Degrading passiert nicht von jetzt auf gleich sondern bei dauerhafter Belastung über einen längeren Zeitraum. Bei massivem Overvolting macht der halt einfach gleich die Biege. Also sollte erstmal alles gut sein.

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

SA wäre der gesamte Chip. System Agent ~ System on Chip.Hallo, kann mir jemand helfen, zu verstehen, wie Degradierung geschieht auf der IMC, begann ich vor kurzem übertakten meinen Speicher und machte einen Fehler, indem Sie 1.8 von SA Spannung statt 1.18 und traf speichern Ausfahrt.

Solange der Ring nichts abbekaam, sehr unwarscheinlich

SA ist loadbalanced (eine VID)

Hohe Spannungen sollten nichts ausmachen.

Da der Boot dann auch failt, und es kein 00 Debug gab ~ ist alles ok.

Im Alternativfall müsste ME die CPU schützen , selbst wenn du 1.6vcore anlegst (bitte nicht über sub zero versuchen)

Der IMC nimmt seine eigene Spannung von VDDCR

Zuletzt bearbeitet:

vorsegenQq

Neuling

- Mitglied seit

- 12.02.2024

- Beiträge

- 2

Wenn der IMC was abgekommen hätte, dann hättest dus schon gemerkt. Degrading passiert nicht von jetzt auf gleich sondern bei dauerhafter Belastung über einen längeren Zeitraum. Bei massivem Overvolting macht der halt einfach gleich die Biege. Also sollte erstmal alles gut sein.

Danke, ich werde den Ring OC dann testen, es scheint, als gäbe es tatsächlich keinen 00 q-code, also hoffe ich, dass alles in Ordnung sein wird.SA wäre der gesamte Chip. System Agent ~ System on Chip.

Solange der Ring nichts abbekaam, sehr unwarscheinlich

SA ist loadbalanced (eine VID)

Hohe Spannungen sollten nichts ausmachen.

Da der Boot dann auch failt, und es kein 00 Debug gab ~ ist alles ok.

Im Alternativfall müsste ME die CPU schützen , selbst wenn du 1.6vcore anlegst (bitte nicht über sub zero versuchen)

Der IMC nimmt seine eigene Spannung von VDDCR

tibcsi0407

Semiprofi

Once I killed a 13900K with TurboVcore.Alternatively, ME would have to protect the CPU, even if you apply 1.6vcore (please don't try above sub zero).

It had some issue with Hwinfo EC. Falkentyne said it's a bug when you apply a Voltage and Hwinfo opened it can mess up the Voltage settings. Set the Voltage, applied then I saw it jumped to a high number and the screen turned off. 00 and no more boot on poor CPU...

It had some issue with Hwinfo EC. Falkentyne said it's a bug when you apply a Voltage and Hwinfo opened it can mess up the Voltage settings. Set the Voltage, applied then I saw it jumped to a high number and the screen turned off. 00 and no more boot on poor CPU...------------

Yesterday I fine tuned the 8533 profile.

Lowered SA to 1.18V and tightened tRFC and some timings were not good acc.to tRFC mini, so I fixed it.

VDD2 on 1.493V, the others are the same.

8600 is still a no-go even on this foundation. Looks like I am walling there for some reason.

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Good timezone.Yesterday I fine tuned the 8533 profile.

Lowered SA to 1.18V and tightened tRFC and some timings were not good acc.to tRFC mini, so I fixed it.

VDD2 on 1.493V, the others are the same.

8600 is still a no-go even on this foundation. Looks like I am walling there for some reason.

mm mm

What crashes then

Tm5 does pass.

Training issue, still channel issue, mc-link issue ?

tibcsi0407

Semiprofi

Could be the in mem delta. I tried the good old 1.52V/1.47V. Tried lowering the VDDQ_MEM too.Good timezone.

mm mm

What crashes then

Tm5 does pass.

Training issue, still channel issue, mc-link issue ?

Ran some cycles with the same bitrates like 8533, so it could be catchable, bit need some time to find out.

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

It will not be "an issue"Could be the in mem delta

It will be just a variable to resolve ~ where the resolve is finetuning RTTs, soo it retains stability.

As mentioned ~ according to ASUS max allowed inside PMIC is 200mV

According to specifications an what i read , max allowed is 300mV for in-mem delta.

Then based on (my) user(s) experience on AM5 (1y work), where VDDQ_CPU is auto adapted

Hence we only work with in-mem delta and separated ODTs (things that are auto on Intels side)

// ^ which is what also became common work approach on Intel EVGA Boards with them forcing 100mV delta in mem by default

Mem delta of 60mV will always work

Mem delta of 105mV may always work, if powering is correct

Mem delta of 180mV can work

i've seen up to 225mV too, but that was on low clock and not with my 1.62v testing. Soo cant verify how good it was.

Also was on a toxic discord field, where i am not sure if i can trust neutral analytics vs emotional preference. 🤭

Basically

"it will not be an issue"

But if it becomes a variable, its resolvable with powering work~

All on all, it will not be whats holding you back, unless there is an urgent need to redo RTTs for given mem-pcb.

Beitrag automatisch zusammengeführt:

Now once VDDQ_CPU is a certainty

And RON (for same VDDQ) is a certainty

CTL0 fixing needs to be verified. If distance to downs remain.

Messing there with CTL0 DQ ODT, makes little sense as it creates a mess with internal ODT predictions

It can be helpful on SA bug, given bug is an ODT issue mostly for target voltage on specific samples

But its nothing i would recommend to touch. Its per sample unique.

Only DQ Vref is , well universal & linear scaling ~ once user has a solid buildin block (their VDDQ)

Basically, put now CTL0 in

Verify it retains stability, and then keep that scale

It should "just work" but who knows at this point. Trust nothing~~

If Bios team messed a lot with MR10-12 (% factor of VDDQ for Vref), then Downs may indeed have shifted vs our collected targets

Or they may even be dynamically training still. Forcing them will remove that uncertain variable.

Lets see what errors 8600 spills.

Now if 48-40-40-48 or stronger 40-34-34-40 is still needed on apex's, to preserve huge VDDQ to VDDQ (Mainboard) delta on high clock.

Only time will tell. I very much expect the better PCB to be fine with 48-40, but theory vs testing.

You also still have your RX-DFE as joker card for later.

But reworked DFE need on mem, just means signal is bad.

If you improved the foundation and in mem delta can retain ~ then signal was not bad

just logic

just logicHigher stable in-mem delta, better signal quality. Its quite simple~

Soo work wasnt waste for nothing.

Zuletzt bearbeitet:

Hey man. So I've tested individual channels on my encore+14900KF. It has MC 89 so I was super excited it would do 8400 but chB does 8400 no problem and chA fails no matter what I try. I've only touched CPU SA/tx/mc and ram.voltages. mrc FB on + MCH check on. Nothing else touched. Is there any suggestion you have that I could try to get chA to not inta fail VT3 @ 8400? I'm posting my current OC below it's 5.4/4.2/48 1.27 llc4 and 1.1SA 1.2TX 1.3MC 8200 36-48. Rn I have both mdie and Adie at hand.48-40-40-48 maybe ?

Anhänge

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Its not that easymrc FB on + MCH check on. Nothing else touched. Is there any suggestion you have that I could try to get chA to not inta fail VT3 @ 8400?

Need to know V/F curve, to know how leaky sample is = voltage suggestions

Need to know personal reasons why you keep MRC fastboot enabled.

How long does MCH full check take ?

The option kind of never worked for ppl i talk with and never for me.

MEM PMIC stay in steps of 30mV, so they have their -/+ 15mV jumps to correct values.

(that is 1.44 VDDQ_MEM)

Is ring fixed strap ?

Ring strap is based on core clk's V/F curve.

ICCMAX used ?

PLL ever touched ?

Is mem on watercooling ?

What bios is this ?

If it behaves how i read it behaves, you run constant voltage on it with c-states + LLC4 ?

Please do not run constant voltage.

EDIT:

With constant voltage, outside of breaking DFVS (dynamic VFS) or how they call it now (i forgot actually)

Old picture [Source: Private researcher ~ Andrea Bartolini; Daniele Cesarini; Luca Benini]

~ higher potential freq, nearly equal to bit better CyclePerInstruction, lower required SIMD Instructions for target work, near equal mem access bandwidth, less potential jitter and predictable powerdraw

You are breaking for CPU which strap to align to which clock (because curve is broken due to VID requests doing nothing)

So you also break throttling behavior due to XYZ clock being fixed ~ outside of causing instability (clock can not be dynamic when you ignore its dynamic requests)

Clock not being loadaware on high (A)

And when thats done, you harm cpu as it can not dynamically throttle or dynamically shift voltage to preserve stability or mitigate noise

= stop running fixed clock or fixed voltage~

It is approach of 2015 ~ Skylake era. 9 years ago.

Intel knew about this in ~2014 already.

Zuletzt bearbeitet:

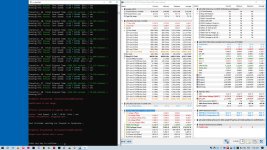

Attached VF to this reply. And yes it's 1.27llc4 with cstates on + manual vcore and LLC. Iccmax is default possibly 511A. Bios 0081, dimms are cooled with a fan hit as high as 50+ in karhu.ring is set to 48/48 min max with down bin auto. MCH full check? It boots in seconds, extremely fast. Even 8800 boots extremely fast on all auto voltages except dram. It's very slow with MRC off, takes like 15 seconds or so, but with MRC it trains in 10 seconds or so and once done next boot is extremely quick.Its not that easy

Need to know V/F curve, to know how leaky sample is = voltage suggestions

Need to know personal reasons why you keep MRC fastboot enabled.

How long does MCH full check take ?

The option kind of never worked for ppl i talk with and never for me.

MEM PMIC stay in steps of 30mV, so they have their -/+ 15mV jumps to correct values.

(that is 1.44 VDDQ_MEM)

Is ring fixed strap ?

Ring strap is based on core clk's V/F curve.

ICCMAX used ?

PLL ever touched ?

Is mem on watercooling ?

What bios is this ?

If it behaves how i read it behaves, you run constant voltage on it with c-states + LLC4 ?

Please do not run constant voltage.

EDIT:

With constant voltage, outside of breaking DFVS (dynamic VFS) or how they call it now (i forgot actually)

You then breaking for cpu which strap to align to which clock (because curve is broken)

So you also break throtting behavior due to XYZ clock being fixed ~ outside of causing instability

Clock not being loadaware on high (A)

And when thats done, you harm cpu as it can not dynamically throttle or dynamically shift voltage to preserve stability or mitigate noise

= stop running fixed clock or fixed voltage~

It is approach of 2015 ~ Skylake era. 9 years ago.

Anhänge

zebra_hun

Profi

OFF---> für Spaß

Ich habe entlich Zeit hatte zu meinem 13700k/z690 D4 einbauen. Es war gut bischen D5 Pause machen.

Nach einem Stunden ein Screen noch gemacht, leider in 82 Mins VST Error. Egal, es ist Spaß. Bits/sec ich weiss es nicht, ob es gut o. schlegt ist. Nie gesehen D4 I7 Ergebnis.

LG zeb

ON---> Sorry

Ich habe entlich Zeit hatte zu meinem 13700k/z690 D4 einbauen. Es war gut bischen D5 Pause machen.

Nach einem Stunden ein Screen noch gemacht, leider in 82 Mins VST Error. Egal, es ist Spaß. Bits/sec ich weiss es nicht, ob es gut o. schlegt ist. Nie gesehen D4 I7 Ergebnis.

LG zeb

ON---> Sorry

Anhänge

Veii

Enthusiast

- Mitglied seit

- 31.05.2018

- Beiträge

- 1.480

- Desktop System

- QA Platform

- Laptop

- ASUS 13" ZenBook OLED [5600U]

- Details zu meinem Desktop

- Prozessor

- Intel Core Ultra 9 285K

- Mainboard

- ASRock OC Formula

- Kühler

- Alphacool T38 280mm

- Speicher

- G.Skill Z5 CK 9600

- Grafikprozessor

- GTX1080ti KP [XOC ROM] // EVGA GTX 650 1GB [UEFI GOP]

- Display

- KOORUI GN10 miniLED

- SSD

- Samsung EVO 850

- Soundkarte

- ESI Ambier i1 & AKG P820

- Gehäuse

- Open-Bench

- Netzteil

- Corsair SF85 // Seasonic GX-550

- Keyboard

- Topre Realforce 108UBK 30g [Silenced]

- Mouse

- Endgame-Gear OP1 8K

- Betriebssystem

- Win11

- Internet

- ▼42 MBit ▲15 MBit

Medium-High leaky sample.Attached VF to this reply. And yes it's 1.27llc4 with cstates on + manual vcore and LLC. Iccmax is default possibly 511A. Bios 0081, dimms are cooled with a fan hit as high as 50+ in karhu.ring is set to 48/48 min max with down bin auto. MCH full check? It boots in seconds, extremely fast. Even 8800 boots extremely fast on all auto voltages except dram. It's very slow with MRC off, takes like 15 seconds or so, but with MRC it trains in 10 seconds or so and once done next boot is extremely quick.

8200 probably around 1.15 to 8400 around 1.18 SA

8200MT7s probably near 1.39-1.4v VDD2_CPU & 8400 near 1.44-1.46v.

Should be plenty before you reach first wall

So because VID (prioritizing) is effectively broken with fixed voltage

And nearly all voltages in CPU are dynamically supplied ~ it will happen that IMC gets too little voltage.

Check spoiler in #13.324 if you look for something specific to read through. Its "some" posts i found, not all.

It does link ~50-60 pages pack on how to work with V/F curve. How to tune how to test

To figure it out its probably requiring you to read 10+ pages in back and forth, how to proceed and what to test.

The talk with zebra_hun & later tibcsi0407

ICCMAX limit to first 400A then work on curve ~ likely 8000MT/s.

VR MAX limit 1550mV

Ignore VDDQ topic for now, till cores are solid

No DC_Loadline telemetry faking. No fixed clock. No voltage offsets, no PLL.

Track scaling on dynamic clock with GB3, GB6, CB23, CB15 extr and pyprime 2B (last 3 on benchmate)

Come back later once you finished the first part - that is CPU tuning.

Then you can limit to 364A for normal (high-temp) watercooling, if you want. Or 400A with MoRa and similar.

I don't want to help you any further degrading your CPU. Because it likely already will be happening.

510A "default Apex" limit is huge. Its not good. But capping it to intel standards would prevent memOC or loose perf = user complains

Can't win on both fronts.

tibcsi0407

Semiprofi

Agreed. The work what we did to get this 8533 with manual RON tuning could be really important to go further.It will not be "an issue"

It will be just a variable to resolve ~ where the resolve is finetuning RTTs, soo it retains stability.

As mentioned ~ according to ASUS max allowed inside PMIC is 200mV

According to specifications an what i read , max allowed is 300mV for in-mem delta.

Then based on (my) user(s) experience on AM5 (1y work), where VDDQ_CPU is auto adapted

Hence we only work with in-mem delta and separated ODTs (things that are auto on Intels side)

// ^ which is what also became common work approach on Intel EVGA Boards with them forcing 100mV delta in mem by default

Mem delta of 60mV will always work

Mem delta of 105mV may always work, if powering is correct

Mem delta of 180mV can work

i've seen up to 225mV too, but that was on low clock and not with my 1.62v testing. Soo cant verify how good it was.

Also was on a toxic discord field, where i am not sure if i can trust neutral analytics vs emotional preference. 🤭

Basically

"it will not be an issue"

But if it becomes a variable, its resolvable with powering work~

All on all, it will not be whats holding you back, unless there is an urgent need to redo RTTs for given mem-pcb.

Beitrag automatisch zusammengeführt:

Now once VDDQ_CPU is a certainty

And RON (for same VDDQ) is a certainty

CTL0 fixing needs to be verified. If distance to downs remain.

Messing there with CTL0 DQ ODT, makes little sense as it creates a mess with internal ODT predictions

It can be helpful on SA bug, given bug is an ODT issue mostly for target voltage on specific samples

But its nothing i would recommend to touch. Its per sample unique.

Only DQ Vref is , well universal & linear scaling ~ once user has a solid buildin block (their VDDQ)

Basically, put now CTL0 in

Verify it retains stability, and then keep that scale

It should "just work" but who knows at this point. Trust nothing~~

If Bios team messed a lot with MR10-12 (% factor of VDDQ for Vref), then Downs may indeed have shifted vs our collected targets

Or they may even be dynamically training still. Forcing them will remove that uncertain variable.

Lets see what errors 8600 spills.

Now if 48-40-40-48 or stronger 40-34-34-40 is still needed on apex's, to preserve huge VDDQ to VDDQ (Mainboard) delta on high clock.

Only time will tell. I very much expect the better PCB to be fine with 48-40, but theory vs testing.

You also still have your RX-DFE as joker card for later.

But reworked DFE need on mem, just means signal is bad.

If you improved the foundation and in mem delta can retain ~ then signal was not badjust logic

Higher stable in-mem delta, better signal quality. Its quite simple~

Soo work wasnt waste for nothing.

Maybe I should aim 8600 C36 where I can use high in-mem delta again. But first I need to find the TM5 stability for that. Last time I tried it was okay until 45-50 mins, so could be possible.

tRP and tRCD should be the key, probably 49 is too tight at this speed.

Maybe I should find the current RTT's too manually.

Is it possible to test only one of them at a time and leave the others on auto, or should I change all of them together?

Would be much easier to hunt them down one by one.

Ähnliche Themen

[Sammelthread]

Intel Core Ultra (Arrow-Lake-S) S.1851 OC- und Laberthread

- Antworten

- 526

- Aufrufe

- 38K