Werbung

Die auf der GeForce RTX 3090 verwendete GA102-GPU basiert auf der Ampere-Architektur, die sich aber wiederum von der Datacenter-Variante unterschiedet, wie sie in der GA100-GPU zum Einsatz kommt.

Der Ampere Streaming Multiprocessor (SM) verzichtet nahezu komplett auf die FP64-Recheneinheiten, die in der GA100-GPU für den HPC-Einsatz noch wichtig sind, im Endkundenbereich aber keine Rolle spielen. Wir sehen 1/60 der FP32-Leistung, dafür wird bei Berechnungen aber auch die doppelte Genauigkeit geboten.

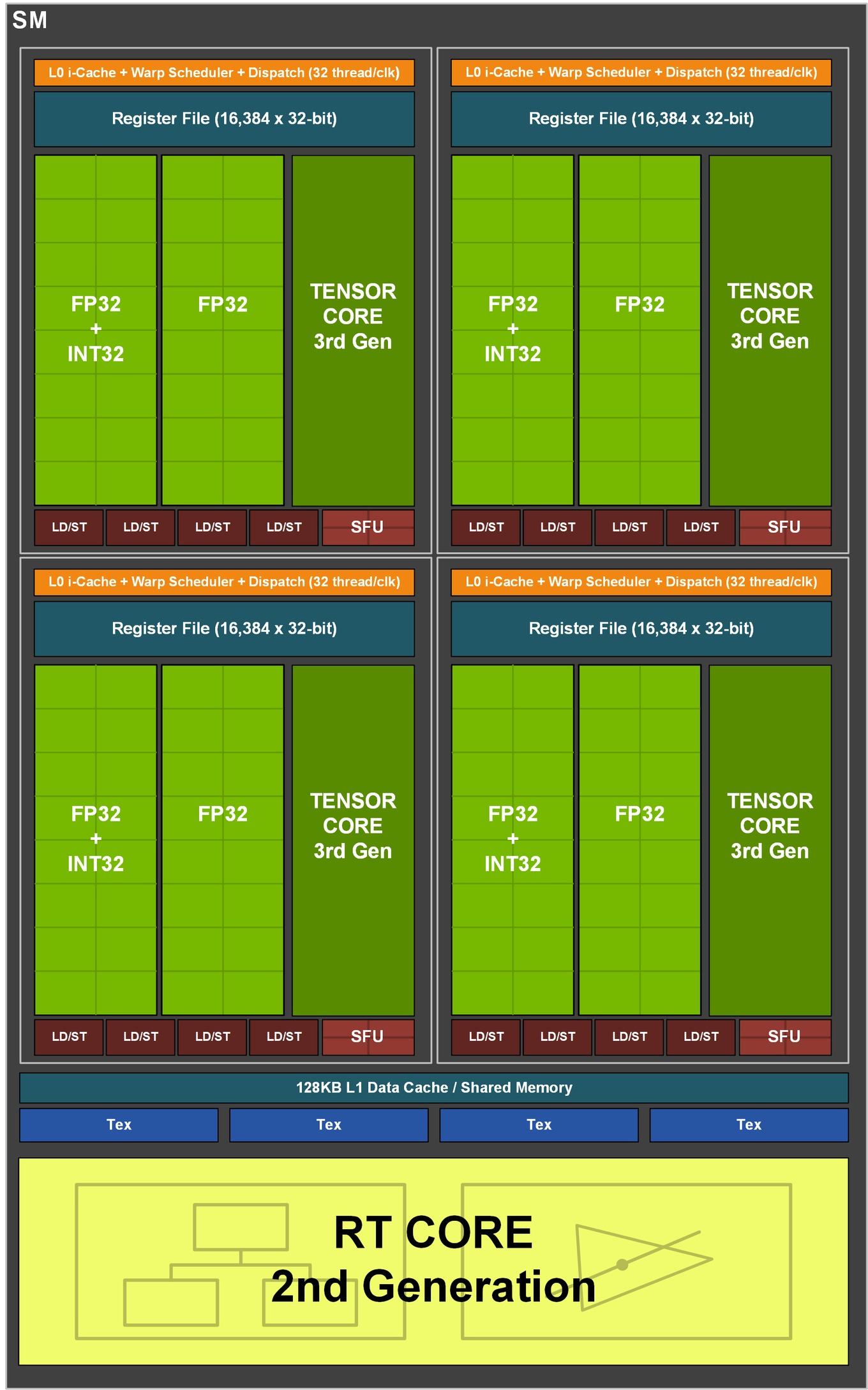

Stattdessen hat man die Anzahl der FP32-Recheneinheiten verdoppelt. Statt 64 der FP32-Einheiten pro SM gibt es nun 128. Hinzu kommen 64 INT32-Einheiten. Es gibt nun zwei Datenpfade pro Quadrant eines SMs, die teilweise parallel angesprochen werden können. Einer der Datenpfade besteht aus 16 FP32-Einheiten. Hier können also 16 FP32-Berechnungen pro Takt bearbeitet werden. Ein zweiter Datenpfad besteht aus jeweils 16 FP32- und INT32-Einheiten. Jeder der SM-Quadranten kann entweder 32 FP32-Operationen ausführen oder jeweils 16 FP32- und INT32-Operationen pro Takt. Für den gesamten SM bedeutet dies die mögliche Ausführung von 128 FP32-Operationen oder jeweils 64 FP32- und INT32-Operationen pro Takt.

Die GA102-GPU verfügt über sieben GPCs (Graphics Processing Clusters) mit jeweils 12 SMs. Bei der GeForce RTX 3090 und GeForce RTX 3080 sind aber nicht alle SMs aktiviert. Die GA102-GPU käme theoretisch auf insgesamt 10.752 FP32-Einheiten (7 GPCs x 12 SMs x 128 FP32-Einheiten). Für die GeForce RTX 3090 aber sind zwei SMs deaktiviert worden und somit kommt die Karte auf "nur" 10.496 FP32-Einheiten. NVIDIA tut dies, um die Ausbeute der Chips so hoch wie möglich zu halten.

Weiterhin pro SM vorhanden sind vier Tensor Cores der dritten Generation, deren Anzahl pro SM nun also halbiert wurde, die aber mindestens doppelt so leistungsfähig sein sollen. Es bleibt bei einem RT Core pro SM, aber auch hier gibt es für die nun zweite Generation einige Verbesserungen. Die Details dazu findet ihr in unserem Launch-Artikel der GeForce RTX 3080 Founders Edition.

Neben den Änderungen in den SMs gibt es auch solche im Aufbau der ROPs bzw. der Kopplung zwischen den ROPs und den Speichercontrollern. Bis zur Turing-Generation sind die ROPs immer am Speicherinterface angeschlossen. Pro 32-Bit-Speichercontroller waren acht ROPs vorhanden. Änderte sich die Anzahl der Speichercontroller und damit die Größe des Speicherinterface, galt dies auch für die ROPs. Für die Ampere-Architektur sind die ROPs im GPC untergebracht. Pro GPC gibt es zwei ROP-Partitionen, die jeweils acht ROPs enthalten. Damit ergibt sich auch eine andere Berechnung für die Anzahl der ROPs bei den Ampere-Karten. Wir sprechen hier von sieben GPCs mit jeweils 2x 8 ROPs also 112 ROPs ingesamt.

NVIDIA hat die Integration der ROPs in dieser Form ausgeführt, um das Render-Backend nicht mehr derart abhängig vom Speicherinterface zu machen. So hat man nun zwar ein 320 Bit breites Speicherinterface für die GeForce RTX 3080 umgesetzt, kann aber 96 anstatt nur 80 ROPs verwenden. Für das 384 Bit breite Speicherinterface der GeForce RTX 3090 hätte dies nach dem alten Schema nur 96 ROPs bedeutet, faktisch vorhanden sind aber nun derer 112.