digitalbath

Mr. Oldschool-Bios

- Mitglied seit

- 04.05.2008

- Beiträge

- 4.121

- Ort

- Moers

- Details zu meinem Desktop

- Prozessor

- AMD R7 5800X

- Mainboard

- ASRock B550 Steel Legend

- Kühler

- Scythe Fuma 2 + Noctua

- Speicher

- Crucial Ballistix DDR4 3600 32GB

- Grafikprozessor

- AMD XFX RX6600

- Display

- BenQ 24" XL2410t

- SSD

- 2x500GB; 1x1000GB

- HDD

- Ja, für Datengrab

- Soundkarte

- O2 + AKG K702 / K340

- Gehäuse

- Deepcool Matrexx 55 V3 RGB

- Netzteil

- BeQuiet! SystemPower11 Platinum 550W

- Keyboard

- Corsair K90

- Mouse

- Kingston Plastikmüll-X

- Betriebssystem

- Win11

- Webbrowser

- der rote Fuchs

Thank you for the clarification! I will add this to my post.

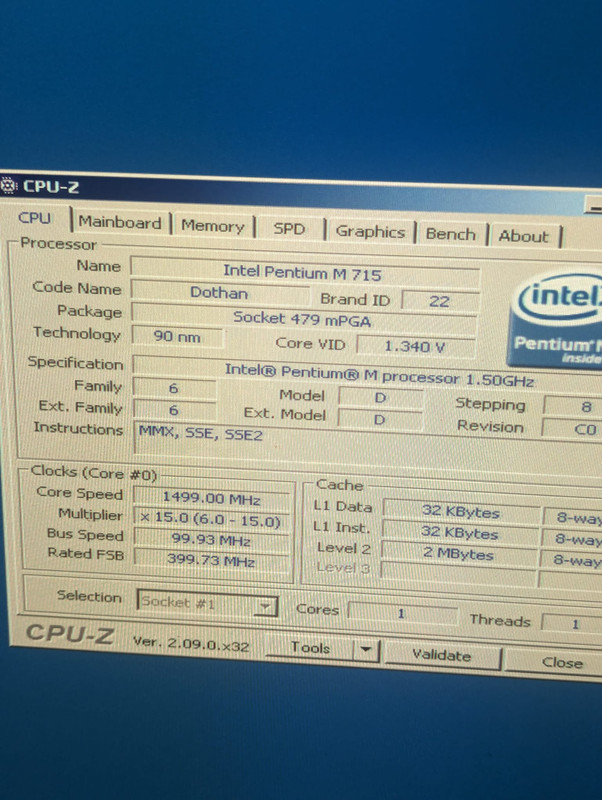

When I did the tests with the ASUS board, I saw, that both settings are unclear or wrong. I wasn't able to figure it out.

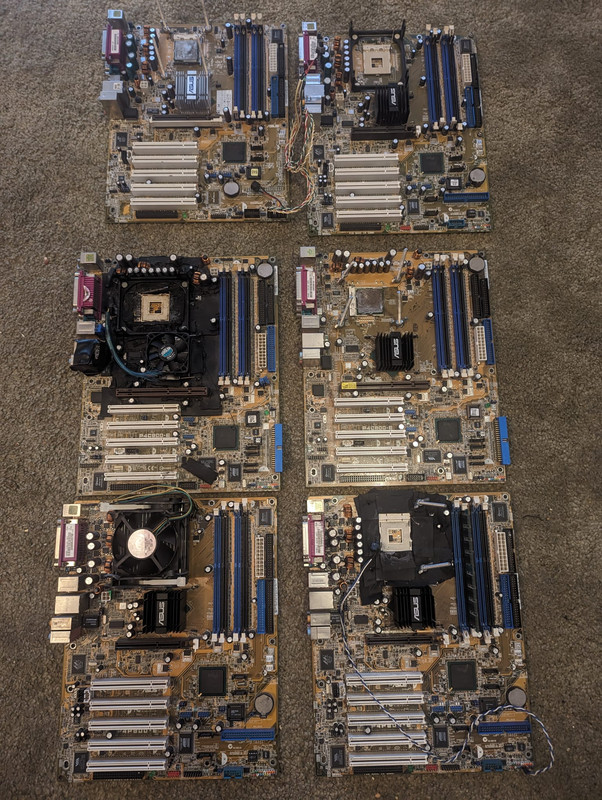

I still have the Gigabyte board. Someday I want to test this board if it is good for OC and if it differs from AMI BIOS ASUS board. I need a new BIOS chip for it first though.

edit. is this part correct?

When I did the tests with the ASUS board, I saw, that both settings are unclear or wrong. I wasn't able to figure it out.

I still have the Gigabyte board. Someday I want to test this board if it is good for OC and if it differs from AMI BIOS ASUS board. I need a new BIOS chip for it first though.

edit. is this part correct?

Code:

Burst length

Register b0d6f0 54h [19:16]

1111 = disable (8 Clocks)

0000 = enable (4 Clocks)

Zuletzt bearbeitet: