Also erstmal ist der Wiki Artikel Kacke. Alleine schon weil Banks und Ranks in einen Topf geworfen wird.

Banks sind auf Chipebene, Ranks auf Modulebene.

Ich habe den Artikel vor mehreren Jahren korrigiert bis dann jemand die technisch korrekte Version verworfen hat mit der Begründung ich hätte nicht genug nachweise eingefügt. Die JEDEC DDR3 Norm war dem wohl zu kompliziert.

Anyway, kurze Zusammenfassung:

1) Mehr Ranks = schneller

Grund: Von Rank0 auf Rank1 wechseln geht schneller als von Modul0 auf Modul1. Zudem hat ein DR Modul bessere Subtimings als ein gleich großes SR Modul (siehe tRFC Erkläung oben).

2) Dass die Subtimings nicht im SPD stehen ist nur teilweise richtig. Im SPD stehen mehr Timings als nur die bekannten 4. Aber auch darüber hinaus gibt es noch mehr "Sub-Sub-Timings". Die stellt das Board ein. Einfach mal ein Modul mit Thaiphoon Burner auslesen statt mit CPU-Z (es hat nen Grund dass es CPU-Z und nicht RAM-Z heißt

).

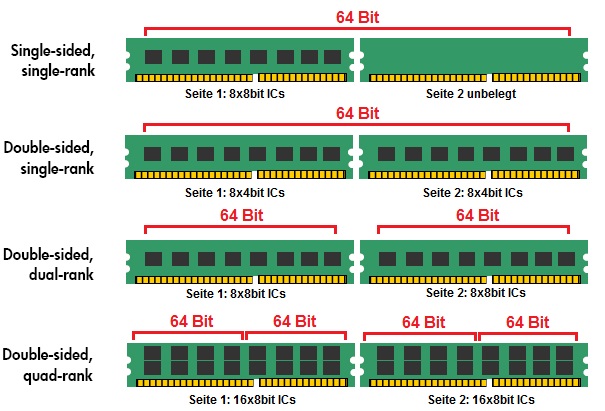

3) Zum Thema einseitig / beidseitig:

Man KANN vieles bauen. Aber es gibt Design Vorlagen an die sich die Hersteller eigentlich halten müssen.

2 Ranks auf einer Seite ist z.B. nicht freigegeben. 1 Rank auf 2 Seiten ist nur für Server- und Notebookspeicher freigegeben.

Kurzfassung:

Bei handelsüblichem unbuffered RAM für PCs ist einseitig = Single Rank und beidseitig = Dual Rank.

Handelsübliche SO-DIMMs für Notebooks sind IMMER beidseitig, einfach aus Platzmangel.

Keiner der bekannten Hersteller weicht davon ab, weil es das ganze teurer und/oder inkompatibel machen würde. Beispiel sind hier die "Nur für AMD" DDR2 Module. Diese haben 16 Chips in 1 Rank auf 2 Seiten verteilt. Läuft aber eben deshalb auf vielen Boards nicht.

Octal Rank (fehlt auf Wiki auch) und Quad Rank gibts nur für Serverspeicher.

4) Was in dem Wiki Artikel korrekt ist:

Mehr Ranks = Mehr Last auf dem Speichercontroller.

Das ist insbesondere bei OC relevant, denn dann

kann die höhere Last zu weniger Maximaltakt (RAM Takt und teilweise auch CPU Takt!) führen.

5) Warum SR und DR?

Ganz einfach: Single Rank ist billiger. 8 Stück 8 Gbit Chips sind billiger als 16 Stück 4 Gbit Chips.

Zudem gibt es ein paar Atom CPUs die nur SR können. Wurde von Intel künstlich beschnitten um die TDP weiter drücken zu können (mehr Last = mehr Strom = mehr Abwärme).