Werbung

Bisher hatten wir noch keine Gelegenheit die RDNA-3-Architektur genauer zu beleuchten. Zum Start der ersten beiden Karten wollen wir dies aber nun nachholen.

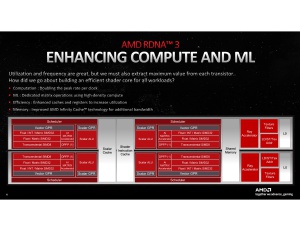

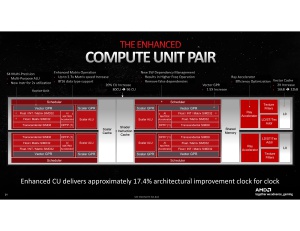

Fangen wir bei den kleinsten Elementen der Architektur an: Den Compute Units. AMD legt diese schon etwas länger als Dual Compute Unit aus. Zu jeder Compute Unit gehören zwei Scheduler, welche die Zuteilung der Rechenoperationen vornehmen und jeweils eine Vector- und Scalar-Recheneinheit.

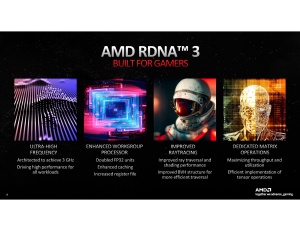

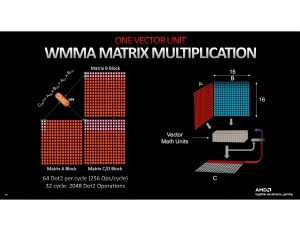

Die Vector-Einheiten übernehmen beispielsweise die Fließkomma-Berechnungen mit einer Genauigkeit von bis zu 32 Bit (FP32). Neben diesen Recheneinheiten gehören auch noch die Raytracing-Beschleuniger, ein Matrix-Beschleungier und die Load- und Store-Einheiten zu diesem Block, die sich dann auch den L0-Cache teilen. Der L0-Cache ist pro Dual Unit 32 kB groß, was einer Verdopplung gegenüber RDNA 2 entspricht.

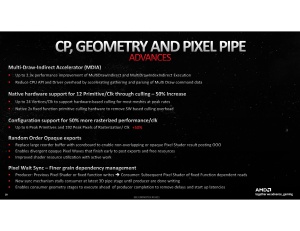

In diesen kleinsten Recheneinheiten werden die heruntergebrochenen Berechnungen durchgeführt. In der Geometrie- und Pipel-Pipeline hat AMD aber auch einen Multi-Draw-Indirect-Accelerator (MDIA) eingebaut, der die sogenannten Primitives (also kleinsten Elemente, aus denen eine Szene besteht bzw. mit denen gearbeitet wird) zu beschleunigen. In diesem Bereich will AMD große Fortschritte gemacht haben, die dazu führen, dass die Geometrie- und Pixelleistung um 50 bis über 100 % steigt.

Die IPC-Leistung der RDNA-3-CUs soll um 17,4 % höher ausfallen, als bei den RDNA-2-CUs.

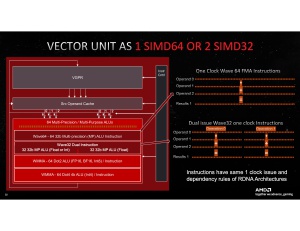

Eine der wichtigsten Änderungen in der RDNA-3-Architektur betrifft die Workgroup Prozessoren (WGP). Die FP32-Recheneinheiten können nun ein "Dual Issue" ausführen – zwei anstatt nur einen Rechenbefehl demzufolge. Dazu müssen diese Rechenbefehle aber identisch sein, was zu einem gewissen Grad in einer GPU bei den entsprechenden Berechnungen aber auch der Fall ist. Die RDNA-3-Architektur ist für die Nutzung des Instruction Level Parallelism (ILP) also darauf angewiesen, dass die Wavefronts möglichst parallel arbeiten, da sonst Ressourcen ungenutzt liegen bleiben. Im Idealfall kann eine Compute Unit (CU) somit 128 anstatt wie bisher 64 FP32-Rechenbefehle ausführen.

Ein ILP ist ein relativ einfacher Weg, um den Durchsatz an Berechnungen zu erhöhen. Allerdings ist man hier darauf angewiesen, dass der Prozentsatz an möglichen Doppel-Berechnungen relativ hoch ist, damit man von dem Umstand zwei Berechnungen pro Recheneinheit machen zu können, auch Gebrauch macht. Es dürfte interessant zu sehen sein, wie hoch die Nutzung von ILP in der Praxis sein wird. AMD wird eigene Zahlen dazu haben, hat sich bisher aber noch nicht weiter dazu geäußert.

Um die Recheneinheiten besser auslasten zu können, hat AMD die VGPR (Vector General-Purpose Registers) um 50 % größer gestaltet. Jede Compute Unit verfügt zudem über zwei nicht näher beschriebene KI-Einheiten, die einfache INT8- und BFLOAT16-Berechnungen schneller ausführen können. Vergleichbar mit den Tensor-Kernen sind diese KI-Einheiten wohl nicht - und dennoch will AMD den Durchsatz der entsprechenden Berechnungen um den Faktor 2,7 gesteigert haben. Für FSR kommt aktuell noch keine KI zum Einsatz, aber das könnte sich in Zukunft auch ändern. Inzwischen gibt es auch einige weitere Anwendungen, vor allem im professionellen Bereich, die von den KI-Einheiten Gebrauch machen können.

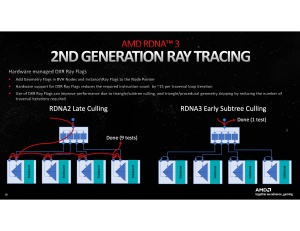

Die verbesserte Raytracing-Leistung wird dadurch erreicht, dass die entsprechenden Einheiten 50 % mehr Strahlen pro Takt berechnen können. Die BVH-Struktur einer jeden Raytracing-Berechnung wird weiterhin in den Shadereinheiten berechnet. Über die RT-Einheiten beschleunigt werden vor allem das Ray Box Sorting sowie das Ray Traversal.

Die gesamte Cache-Hierarchie hat eine große Überarbeitung erfahren. Den um 50 % größere L0-Cache haben wir bereits angesprochen, aber auch der L1-Cache ist mit 256 kB pro WGP und insgesamt 3 MB doppelt so groß, wie bei RNDA 2 und zudem auch noch mit 6.144 Bit/Takt 50 % schneller angebunden.

Diese 50 % an Bandbreite setzen sich auch zum L2-Cache fort, der nun 6 MB groß ist und somit um 50 % anwächst. Am wichtigsten aber ist die Anbindung zum Infinity Cache, die nun mit 2.304 Bit/Takt stattfindet, was einer Steigerung um 225 % entspricht. Zwar fällt die Kapazität mit 96 zu 128 MB etwas geringer aus, durch die schnellere Anbindung soll dieser Nachteil aber wieder wettgemacht werden.

Letztendlich wird auch das Speicherinterface schneller. 384 Bit erreichen nun 960 GB/s, was einem Plus von abermals 50 % entspricht. Den Caches aber kommt eine besondere Bedeutung zu, denn Daten, die innerhalb des L0- bis L2-Caches und schlussendlich auch des Infinity Caches verbleiben können, müssen nicht vom GDDR6 gelesen oder in diesen geschrieben werden.

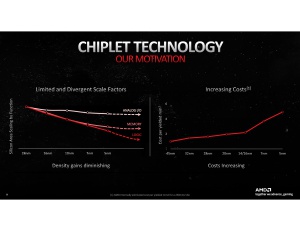

Das Chiplet-Design

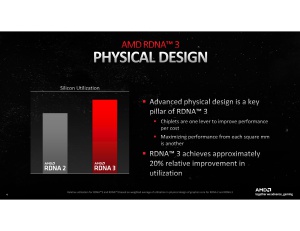

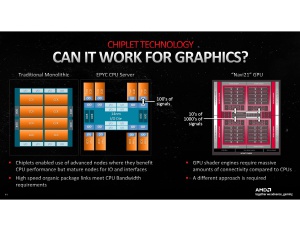

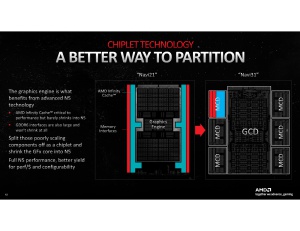

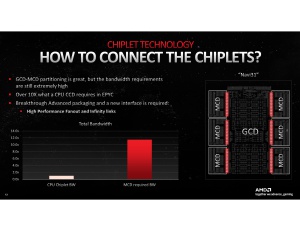

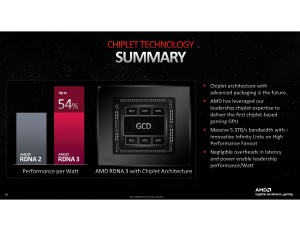

Das, was die Navi-3x-GPUs auf Basis der RDNA-3-Architektur aber sicherlich ebenfalls auszeichnet ist der Chiplet-Ansatz, den AMD für eine GPU erstmals im Endkundenbereich einsetzt. Es ist auch nicht ganz trivial die Anforderungen an die Interconnect-Geschwindigkeiten von den erfolgreichen CPU- auf die GPU-Designs zu übertragen.

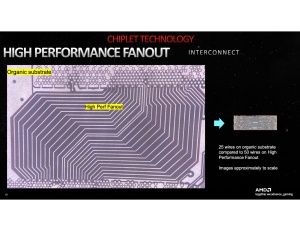

Zwischen den CCDs und dem zentralen IOD verwendet AMD den Infinity Fabric. Physikalisch umgesetzt wird diese Verbindung über mehrere hundert Kontakte zwischen dem CCD und dem IOD. Für die GPUs und hier spezifisch für die Verbindung zwischen dem GCD und den MCDs sind aber höhere Bandbreiten erforderlich. Diese setzen mehr Verbindungen voraus, im Falle der Navi-3x-GPUs reden wir von mehreren zehntausend Routen zwischen einem MCD und dem GCD.

Die klassischen Methoden mittels eines organischen Substrats sind unzureichend, um mehrere zehntausend Verbindungen zwischen mehreren Chips herzustellen. Hier kommt AMDs mit TSMC gemeinsam durchgeführte Entwicklung der 2.5D Elevated Fanout Bridge (EFB) ins Spiel. Diese verwendet AMD schon bei den Radeon-Instinct-MI200-Beschleunigern.

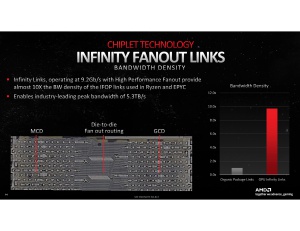

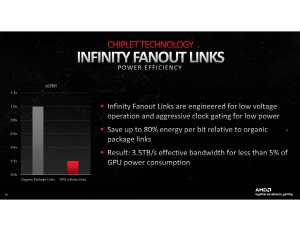

Über diese EFB schickt AMD 9,2 GBit/s pro Link und kommt somit insgesamt auf 5,3 TB/s an Bandbreite über die gesamten Infinity Links. Im Vergleich zu anderen Interconnect-Methoden ist die EFB auch extrem effizient, sodass AMD hier nicht einen Großteil der Leistungsaufnahme für die Verbindungen aufbringen muss.

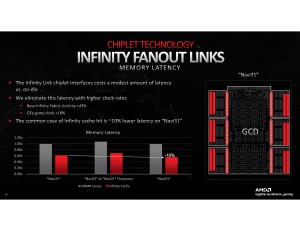

Aber ein Chiplet-Design hat auch Nachteile und auch diese kennen wir schon von den Ryzen- und EPYC-Prozessoren. Die Latenzen steigen, sobald eine Chip-zu-Chip-Kommunikation notwendig wird. Im Falle der Navi-3x-GPUs befinden sich der Infinity Cache und die Speichercontroller in den MCDs, die an den GCD angebunden sind.

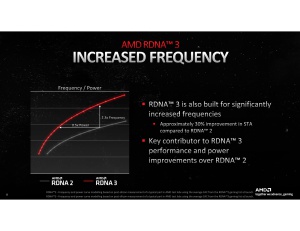

Durch gesteigerte Taktraten des Infinity Fabric sowie der GPU als solches, kann AMD die Latenzen im Vergleich zu Navi 21 sogar um 10 % reduzieren.

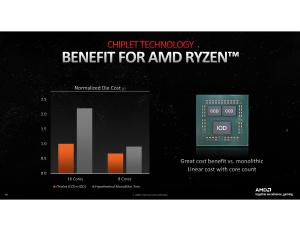

Das Package besteht letztendlich aus einem zentralen Graphics Chiplet Die (GCD) und mehreren Memory Chiplet Dies (MCD). Der GCD wird in 5 nm bei TSMC gefertigt, der MCD in 6 nm – ebenfalls bei TSMC. Das Chiplet-Design soll laut AMD die Flexibilität erhöhen. Man fertigt viele kleine und identische MCDs, die einfach zu fertigen sind und in der gewünschten Anzahl eingesetzt werden können, während der zentrale GCD in der gewollten Ausbaustufe gefertigt wird und mit den MCDs in der gewünschten Anzahl kombiniert wird. Der GCD kommt auf eine Fläche von 300 mm², die MCDs auf jeweils 37,5 mm².

Die Navi-31-GPU der Radeon RX 7900 XTX bringt es somit auf insgesamt 525 mm² (300 mm² + 6x 37,5 mm²). Zum Vergleich: Die AD102-GPU der GeForce RTX 4090 kommt auf 608,3 mm². NVIDIA lässt seine monolithischen Chips bei TSMC in 4 nm fertigen.