Werbung

Vor etwas mehr als einer Woche erschienen die ersten Tests des Ryzen 7 5800X3D, dem ersten Prozessor mit 3D V-Cache, der explizit auf Spiele ausgelegt ist und hier seine Stärken haben soll. Inzwischen ist der Prozessor auch im Handel verfügbar. Heute wollen wir unseren Test des Einhorns für AM4 präsentieren, denn es dürfte das letzte Hurra für den Sockel AM4 sein, bevor AMD alles auf die neue Plattform umstellt. Der Ryzen 7 5800X3D dürfte auch eine Art Testballon für die Zen-4-Generation sein, denn AMD wird die 3D-V-Cache-Strategie fortsetzen und sogar ausbauen wollen. In welchen Marktsegmenten dies aber Sinn macht, dürften aktuelle Erfahrungen festlegen.

Zur Computex 2021 präsentierte AMD den ersten Ryzen-Prozessor mit 3D V-Cache. Damals war noch nicht ganz klar, in welchem Umfang AMD die neue Technik einsetzen wird. Die ersten Prozessoren war für Ende 2021 angedacht. Es sollte nun aber bis zum 20. April 2022 dauern, bis der Ryzen 7 5800X3D als erstes Modell in den Handel gekommen ist – zehn Monate nach der ersten Vorstellung. Diese lange Wartezeit und frühe Ankündigungsphase ist sicherlich einer der Hauptkritikpunkte am Produkt selbst, denn es kommt reichlich spät und kann nicht mehr alle Vorteile in der Form ausspielen, wie dies noch Ende 2021 der Fall gewesen wäre.

Für eine erste Ryzen-Generation mit 3D V-Cache hat sich AMD für die Umsetzung eines Modells mit nur einem CCD entschieden. Acht Kerne sind also das Ziel und für einen Gaming-Prozessor reicht dies wohl auch aus. Im vergangenen Jahr präsentierte man die 3D-V-Cache-Technik noch mit einem Modell mit 12 Kernen und nutzte dazu auch entsprechend zwei CCDs, am Ende aber dürfte die knappe Verfügbarkeit hier auch eine Rolle gespielt haben, denn die EPYC-Prozessoren mit mehr Cache sind ebenfalls bereits verfügbar und versprechen eine bessere Marge. Im Rahmen der Modellpalette stellt sich der Ryzen 7 5800X3D wie folgt dar:

| Kerne | Basis / Boost | L3-Cache | TDP | Preis | |

| Ryzen 9 5900X | 12 | 3,7 / 4,8 GHz | 64 MB | 105 W | 439 Euro |

| Ryzen 7 5800X3D | 8 | 3,4 / 4,5 GHz | 96 MB | 105 W | 489 Euro |

| Ryzen 7 5800X | 8 | 3,8 / 4,7 GHz | 32 MB | 105 W | 339 Euro |

Der Ryzen 7 5800X3D hat genau wie das 5800X-Gegenstück acht Zen-3-Kerne, diese arbeiten aber mit einem geringeren Basis- und Boost-Takt. Die TDP von 105 W bleibt unverändert und somit dürfte die Leistungsaufnahme des zusätzlichen Caches sowie die Temperaturen der Grund dafür sein, dass AMD hier nicht mit den identischen Taktraten aufwarten kann. Die 32 MB L3-Cache des CCDs im Ryzen 7 5800X werden um 64 MB an 3D V-Cache ergänzt, sodass man beim Ryzen 7 5800X3D auf 96 MB kommt. Somit hat dieser Prozessor sogar mehr Cache zur Verfügung, als die Modelle mit zwei CCDs (wie zum Beispiel der Ryzen 9 5900X).

Ansonsten gibt es keinerlei Unterschiede in der Ausstattung. Der Ryzen 7 5800X3D unterstützt weiterhin DDR4 über zwei Speicherkanäle und stellt PCI-Express-4.0-Lanes zur Verfügung. Der zusätzliche Cache ist das Alleinstellungsmerkmal des Prozessors.

Preislich positioniert AMD den Ryzen 7 5800X3D mit 489 Euro natürlich deutlich über dem Ryzen 7 5800X und sogar über dem 12-Kern-Modell. Die direkte Konkurrenz sind aber eher der Core i7 12700K (Test) für 380 Euro sowie der Core i9-12900K (Test), der aktuell noch 590 Euro kostet. Der fast 800 Euro teure Core i9-12900KS (Test) spielt preislich in einer ganz anderen Liga. Wie sich das Verhältnis aus Preis und Leistung final darstellen wird, werden wir am Ende des Tests sehen.

Die 3D-V-Cache-Technik im Detail

Wir wollen die Gelegenheit nutzen, die Technik hinter dem 3D V-Cache noch einmal zu erläutern. Als Ausgangspunkt sieht AMD in der Entwicklung die neuen Packaging-Techniken, die man seit einigen Jahren anstrebt und auch ausführt. Sei es der Einsatz von HBM bei den GPUs, der Wechsel auf eine Multichip-Strategie im CPU-Segment oder die Einführung der Chiplet-Strategie – AMD kann sich eine gewisse Vorherrschaft beim Einsatz solcher Techniken auf die Fahnen schreiben. Allerdings sei an dieser Stelle auch noch einmal gesagt, dass AMD dazu auf externe Partner angewiesen ist. Nur im Zusammenspiel mit diesen konnte AMD die Produkte in dieser Form auch ausführen und auf den Markt bringen.

Das 3D-Stacking ist der vorerst letzte Schritt in dieser fortschreitenden Entwicklung. Das Stapeln einer Lage SRAM auf dem Chip stellt aber wiederum nur den ersten Schritt dar. Für zukünftige Generationen werden mehrschichtige SRAM-Chips erwartet, welche die Kapazität des Caches dann deutlich erhöhen sollen.

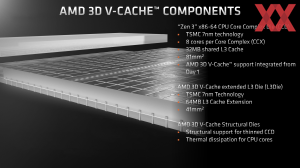

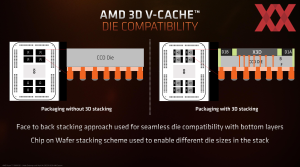

Der 3D V-Cache ist mittels der 3D-Packaging-Technologie direkt über TSVs (Through-silicon Via) mit dem CCD verbunden. AMD nutzt hier die Packaging-Techniken von TSMC. Der in 7 nm gefertigte CCD wird um 180 ° gedreht und 95 % des Chips werden abgeschliffen. Am Ende bleiben nur noch 20 µm des ansonsten 400 µm dicken Chips als aktives Silizium übrig. Auf diese dünne Schicht wird dann der 3D V-Cache (L3D) gestapelt. Auch dieser wird in 7 nm hergestellt und bringt es auf 41 mm².

TSVs aus Kupfer stellen bekanntermaßen die Verbindung zwischen dem CCD und SRAM her. Laut AMD reicht die Adhäsion der Kupfer-Kontaktpunkte der TSVs auf beiden Seiten aus, um die beiden Chips miteinander zu verbinden.Die Datenrate dieser Verbindung beträgt mehr als 2 TB/s. Sogenanntes "Structural Silicon" (D1A und D1B) baut den Bereich höher auf, wo sich kein 3D V-Cache befindet, sodass die Bauhöhe des CCDs wieder gleichmäßig ist.

| Fertigung | Die-Größe | Anzahl Transistoren | |

| CCD | 7 nm | 80,7 mm² | 4,15 Milliarden |

| IOD | 12 nm | 125 mm² | 2,09 Milliarden |

| L3D | 7 nm | 41 mm² | 4,7 Milliarden |

Wie sich die Größe und die Anzahl der Transistoren im Verhältnis zu den restlichen Chiplets darstellt, erläutert obige Tabelle. Der CCD mit seine acht Zen-3-Kernen und 32 MB L3-Cache kommt auf 80,7 mm² und 4,15 Milliarden Transistoren. Der IOD fügt eine Fläche von 125 mm² und 2,09 Milliarden Transistoren hinzu. Ein IOD und ein oder zwei CCDs zusammen ergeben die Komplexität und den Aufbau der Ryzen-Prozessoren ohne den 3D V-Cache. Kommt noch der L3D hinzu, wird auf dem rund 80 mm² großen CCD in etwa die Hälfte durch den zusätzlichen Cache bedeckt. Ebenfalls hinzu kommen 4,7 Milliarden Transistoren. Diese setzen sich wiederum aus dem reinen SRAM, aber auch der Cache Control Logic, Tags, Power Management und vielen anderen Komponenten zusammen.

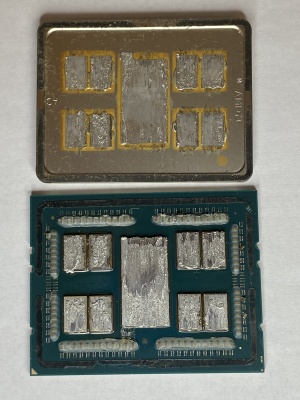

Der Aufbau eines CCDs mit L3D scheint also klar zu sein. Aber offenkundig gibt es Unterschiede zwischen dem, was AMD in den Schaubildern zeigt und der tatsächlichen Umsetzung.

Das Informationsmaterial für den informierten Endkunden zeigt den Aufbau dermaßen, dass auf dem CCD der SRAM platziert wird und zwar genau mittig dort, wo sich der Bereich des L3-Caches befindet. Links und rechts werden dann Structural Silicon aufgebracht, um den Höhenunterschied an diesen Stellen auszugleichen. Seit der Präsentation auf der ISSCC 2022 wissen wir aber, dass sich darüber eine weitere Schicht Silizium befindet. Dieses Support Silicon bringt den gesamten CCD wieder auf die gleiche Bauhöhe wie den CCD ohne 3D V-Cache, sodass das Package in seinen Dimensionen kompatibel zueinander ist.

Obige Fotos zeigen einen AMD EPYC 7473X der geköpft und entsprechend zerschnitten wurde, um den Aufbau des Chips zu analysieren. Das rechte Foto zeigt einen einzelnen CCD mit dem Support Silicon als oberste Schicht. Für den Wärmeübergang spielt dies natürlich eine Rolle, wenngleich der CCD ohne 3D V-Cache ebenfalls so dick ist und zum Heatspreader hin ebenfalls über viel passives Silizium verfügt. Die Fotos stammen von Twitter-Nutzer @wassickt, der solche Analysen von Chips professionell durchführt.