Werbung

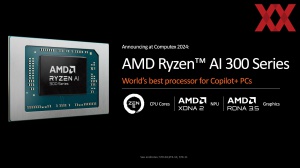

Auf der Computex 2024 im Juni ließ AMD den Vorhang für seine Strix-Point-APUs der Ryzen-AI-300-Familie fallen und gab wenig später alle Details zur Architektur sowie den gemachten Änderungen preis. So langsam trudeln die ersten Geräte auf Basis des Ryzen AI 9 HX 370 und Ryzen AI 9 365 ein. Mit dem heutigen Datum dürfen wir erste Leistungsanalysen veröffentlichen, die einen Ausblick auf das geben, was uns erwarten wird. Wir haben mit dem ASUS Zenbook S16 ein erstes Gerät erhalten.

Anmerkung: Gerne hätten wir einen noch deutlich umfangreicheren ersten Test präsentiert, dafür erreichte uns das Sample aber leider erst deutlich zu spät.

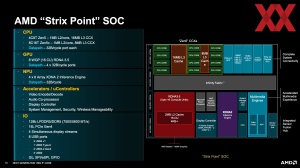

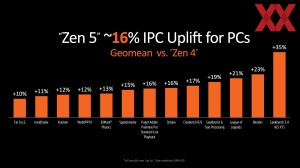

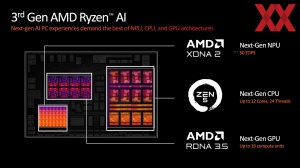

Was zur Computex 2024 angekündigt und kürzlich mit weiteren technischen Details versehen wurde, findet nun in den ersten Produkten Verwendung: Die neuen Strix-Point-SoCs der Ryzen-AI-300-Familie mit Zen-5- und den kompakteren Zen-5c-Kernen. Damit will AMD den Grundstein für seine kommenden Generationen legen und wird diese künftig als Basisarchitektur verwenden. Es handelt sich mitunter um die schnellsten High-Performance-Kerne, die die Chipschmiede bislang entwickelt hat.

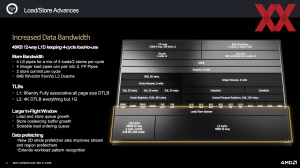

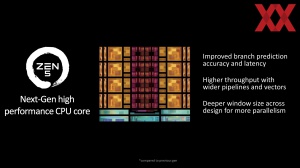

Sie verfügen allesamt über eine neue Sprungvorhersage, die genauer und mit weniger Latenz daherkommen soll. Die Ausführungseinheiten sind breiter und bekommen zusätzliche Vektor-Einheiten. Damit einher geht, dass das Front-End entsprechend mit größeren Caches und Registern ausgestattet wird, um dem breiteren Design Rechnung zu tragen.

Flexible Basisarchitektur für kommende Generationen

Diese Flexibilität nutzt man vor allem für Strix Point, bzw. die Ryzen-AI-300-Prozessoren. Im Zen 5 Core Complex hat man die Architektur so verändert, dass diese jeweils den 256 Bit breiten Fließkomma-Datenpfad verwendet, während für Granite Ridge, bzw. die Ryzen-9000-Prozessoren die volle Breite von 512 Bit verwendet wird. Die Sprungvorhersage macht pro Taktzyklus mehr Vorhersagen und soll eine höhere Genauigkeit erreichen. Ermöglicht wird dies durch einen L1 BTB (Branche Target Buffer) in der Größe des L2-Cache (16K) und einen größeren Adress Stack mit 52 Einträgen. Das Vorhersage-Fenster pro Taktzyklus wächst auf drei an.

Da der L1-Cache für verschiedene Berechnung zu klein wäre, müssten Daten aus dem L2-Cache abgefragt werden, weshalb AMD den L2-Cache ITLB (Instruction Translation Lookaside Buffer) auf 2.048 Einträge erweitert und Instruktionen nun mit 64 anstatt derer 32 Bytes pro Taktzyklus abrufen lässt. Zudem wird die Bandbreite des L1-Instruction-Cache verdoppelt und die Latenz verringert. Die Decode-Einheit ist weiterhin 4-Way breit, wird jedoch verdoppelt.

Dieser Core Complex findet in Granite Ridge, bzw. den Ryzen-9000-Prozessoren seinen Einsatz. In jedem der bis zu zwei CCDs (Core Complex Dies) befinden sich bis zu acht Zen-5-Kerne und jeweils 32 MB an L3-Cache, wobei AMD je nach CPU-Klasse natürlich unterschiedliche Ausbaustufen einsetzt.

Für Strix Point alias Ryzen AI 300 setzt AMD auf einen Core Complex mit vier Zen-5-Kernen und 16 MB L3-Cache sowie einen weiteren Core Complex mit acht Zen-5c-Kernen samt 8 MB L3-Cache. Erstmals in einem SoC-Design von AMD kommt ein asymmetrisches Verhältnis an L3-Cache zum Einsatz. Im SoC-Design für Strix Point sind die beiden CCX mit jeweils 32 Byte pro Taktzyklus für das Lesen und Schreiben an den Infinity Fabric angebunden. Die GPU kommt auf vier Datenpfade mit jeweils 32 Byte pro Taktzyklus.

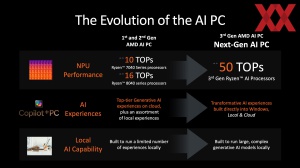

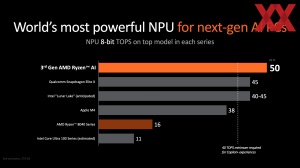

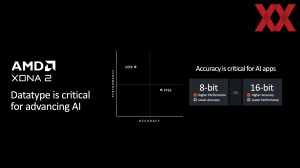

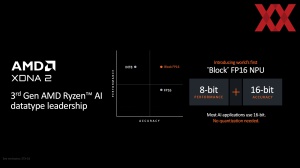

Die NPU namens XDNA2 leistet bis zu 55 TOPS und erreicht vor allem durch mehr Einheiten eine höhere Leistung, aber auch durch eine Erhöhung der Anzahl der AIs von 20 auf 32 und eines 60 % größeren Caches. Angebunden wird die NPU nun mit 32 Byte pro Taktzyklus an den Infinity Fabric.

Auf Seiten der integrierten Grafiklösung setzt AMD erstmals auf die RDNA-3-Architektur, womit sich die AI-APUs von den kommenden Ryzen-9000-Prozessoren absetzen, die noch auf RDNA 2 setzen und sich leider noch ein bisschen verspäten werden. Im Vergleich dazu hat AMD kleinere Änderungen vorgenommen. Diese schließen eine Verdopplung der Texture-Sampler sowie der Interpolation und Comparision Rates ein. Außerdem wurde der Speichercontroller auf die Zusammenarbeit mit LPDDR5 ausgelegt und die Cache-Zugriffe optimiert, was durch ein verbessertes Puffern über eine Verringerung der Zugriffe erreicht werden soll. AMD verspricht eine um 19 bis 32 % höhere Leistung im Vergleich zu Hawk Point.

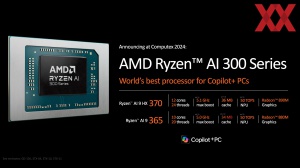

Zum Start gibt es zwei Modelle

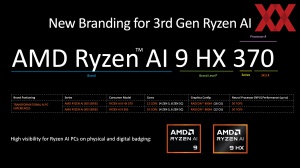

Zum Start von Ryzen AI 300 wird es zunächst zwei Modelle geben, die sich überwiegend im Clusteraufbau unterscheiden. Während der AMD Ryzen AI 9 HX 370 über vier Zen-5- und acht Zen-5c-Kerne verfügt, gibt es beim Ryzen AI 9 365 zwei der kompakteren Cores weniger. Der Takt erreicht im Boost bis zu 5,1 GHz, während die Basisgeschwindigkeit durchgehend bei 2,0 GHz liegt. Die Grafiklösung ist beim kleineren Modell ebenfalls etwas abgespeckt. Statt der 16 CUs gibt es derer nur zwölf.

Konfiguriert sind beide Modelle mit einer TDP von 28 W, wobei diese von den OEMs und damit den Notebook-Herstellern im Bereich von 15 bis 54 W (für kurzfristige Lastspitzen) konfiguriert werden kann. Um die Effizienz weiter zu verbessern, gibt mehr C-States (Active Power Down C-States C8 und C11) und die NPU kann durch ein intelligentes Power-Management in weiteren Sub-Bereichen abgeschaltet werden – ebenso wie einzelne CPU-Kerne.

| Modell | Kerne / Threads | Kern-Typ | Basis-Takt | Boost-Takt | Cache | TDP | cTDP | CUs |

|---|---|---|---|---|---|---|---|---|

| Ryzen AI 9 HX 370 | 12 / 24 | 4x Zen 5 8x Zen 5c | 2,0 GHz | 5,1 GHz | 36 MB | 28 W | 15 - 54 W | 16 |

| Ryzen AI 9 365 | 10 / 20 | 4x Zen 5 6x Zen 5c | 2,0 GHz | 5,0 GHz | 32 MB | 28 W | 15 - 54 W | 12 |

Eingesetzt werden sollen die Ryzen-AI-Chips überwiegend in Notebooks von MSI, HP und ASUS, welche teilweise schon vorgestellt wurden. Mit dem ASUS ZenBook S16 konnten wir nicht ganz zwei Tage vor dem Fall des NDAs ein erstes Gerät in der Redaktion begrüßen und erste Leistungsanalysen anstellen.