Werbung

Auf seinem 2024 Technology Symposium hat TSMC ein Update zu seinen Fertigungsplänen gegeben. Anandtech berichtet über die Neuerungen von einem der ersten Stops des Symposiums in Santa Clara. Trotz aktueller Vormachtstellung in der Wafer-Belichtung sowie dem Packaging (vor allem im Hinblick auf das Auftragsvolumen) gibt man sich wie immer recht zurückhaltend was neue Fertigungsgrößen und Technologien betrifft.

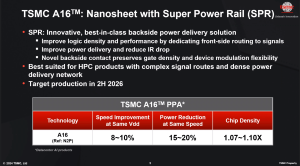

Erstmals von TSMC offiziell genauer spezifiziert wird der erste Fertigungsprozess der Ångström-Ära: A16. Vor einigen Monaten nannte man A14 und A10 bereits in einem Ausblick auf die Skalierung der Fertigungstechnologien. Ab der zweiten Jahreshälfte 2026 sollen die ersten Chips in A16 vom Band laufen. Im Vergleich zu N2P, einem Prozess der aktuell noch nicht in Produktion ist, soll A16 eine 8 bis 10 % höhere Leistung bei gleichem Verbrauch bieten. Umgekehrt ist bei gleicher Leistung eine zwischen 15 und 20 % geringere Leistungsaufnahme möglich. Hinsichtlich der Transistordichte soll diese um den Faktor 1,07 bis 1,1 steigen.

A16 wird TSMCs erster Prozess sein, der sowohl auf Nanosheet-Transistoren wie auch Super Power Rail (SPR) setzt. Bei SPR handelt es sich um ein Back Side Power Delivery Network (BSPDN), ähnlich wie Intels PowerVia. Allerdings gibt es verschiedene Umsetzungen eines BSPDN.

Ursprünglich war der Einsatz der Super Power Rail schon für N2P vorgesehen. Nun verschiebt TSMC dies auf A16. Zu den Gründen macht man keine Angaben.

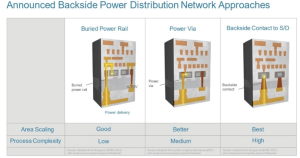

TSMCs SPR ist aus Sicht der Umsetzung und technischen Komplexität auf Niveau von Intels PowerVia. Buried Power Rails wird man also nicht verwenden. Bei diesen befinden sich einige spannungsversorgende Leiterbahnen zwar auf der Rückseite der Transistoren, die Zuführung der Power Rails findet jedoch weiterhin über das Front-End statt. Die Nachteile, dass sich diese Versorgung den Bereich der Datenleitungen teilt, sind also weiterhin vorhanden.

Die zweite Möglichkeit sind Buried Power Rails mit einem BSPDN. Hier findet die Versorgung dann tatsächlich über die Rückseite statt, was die Daten- und Versorgungsbereiche weitestgehend trennt. Für die unterste Ebene (M0) wird weiterhin das Front-End verwendet – das heißt die Ströme werden über vergleichsweise dicke Leitungen auf die Front-End-Seite des Wafers überführt.

Intels Lösung und vermutlich auch TSMCs SPR verbindet die Transistor-Zelle oder den Transistorkontakt mittels Nano-TSV (Through-Silicon Via). Es handelt sich um die aufwändigste Umsetzung eines BSPDN, aber sie bietet auch die meisten Vorteile.

TSMCs Fertigung in A16 ist auf HPC-Produkte ausgelegt. Hier sieht man offenbar weiterhin den größten Wachstumsmarkt in der Fertigung moderner Chips. Das entsprechende Gegenstück wird anhand der Zeitpläne von TSMC und Intel vermutlich Intel 14A sein. Bei Intel 14A wird der Chipriese mit PowerVia eine neue Technologie zur Versorgung des Chips einsetzen. Außerdem wird Intel für diese Fertigung auf High-NA EUV setzen.

Auf dem Symposium sind noch weitere Details zu erwarten. Unter anderem zum Packaging, was neben der eigentlichen Wafer-Belichtung technologisch die zweite große Herausforderung darstellt.

Update:

Nach einigen Nachforschungen im Bereich der BSPDNs deutet sich an: TSMCs Super Power Rail (SPR) geht in der Integration einen Schritt weiter, als dies bei Intels PowerVia der Fall ist.

Zwar binden PowerVia die Stromversorgung über vertikale Nano TSVs an, aber es muss auch eine horizontale Verbindungsebene integriert werden. Ein BSPDN to S/D, oder wie TSMC es nennt SPR, führt die Stromversorgung direkt zu Source und Drain des Transistors. Dadurch wird noch einmal Platz gespart, die Fertigung wird aber deutlich komplexer. Es wird erwartet, dass Intel eine zweite Generation der PowerVia ebenfalls in dieser Form ausführt.