nur dass sich otto-normal-gamer keine äpfel leisten kann.

Nein, es ging um Intel und die Behauptung da hätte sich nichts getan, es wurde nicht auf die Mainstream Plattform Bezug genommen, sondern auf Intel allgemein. Wer mehr Kerne wollte, musste damals eben tiefer in der Tasche greifen, aber so ist es ja immer, wenn man mehr Leistung will, einen AMG bekommt man auch nicht zum Preis des Mercedes Basismodells.

du vergleichst doch auch nicht 12900k mit threadripper und sagst dann intel hängt bei anwendungen total hinterher.

Nein, aber ich gehe auch nicht hin und behaupte AMD würde maximal 16 Kerne bieten, nur weil ich mich dabei alleine auf den Mainstreamsockel beziehe, ohne dies aber anzugeben. Wenn ich sage, AMD bietet im Mainstreamsockel nicht mehr als 16 Kerne, dann ist dies korrekt, wenn aber sage, AMD bietet ja auch nicht als 16 Kerne, dann ist es falsch, da man dann auch die TR (und EPYC) einbeziehen muss und da gibt es CPUs mit mehr als 16 Kernen.

bist du denn nicht der meinung, dass intel sich seit zen stärker bewegt hat als die lauen jahre davor?

Das ist nicht der Punkt, sondern das sich eben auch in der Zeit davor viel getan hat, bei der IPC und der Anzahl der Kerne, nur waren letztere eben nicht im Mainstreamsockel zu finden. Wegen der Probleme mit 10nm, die dann hier schon als bewusstes Zurückhalten hingestellt wurden, hat es sich in der Zeit natürlich gestaut, da neue Architekturen eben für die 10nm Fertigung entwickelt worden waren.

Das wir hier von Mainstream Desktops sprechen und nicht von HEDT Plattformen Richtung Threadripper sollte jedem klar sein, aber die sind auch nicht die Messlatte für den Otto.

Nein, es wurde nicht von Mainstream Desktops gesprochen, sondern allgemein von Intel und wer viele Kerne wollte, für den gab es eben die HEDT Plattform und wenn Otto sich die nicht leisten kann, dann ist das Ottos Problem.

Egal wie man es dreht und wendet, er will auch nicht verstehen das einen Teil der IPC dem shrinking geschuldet ist, also X% mehr Transistoren der gleichen Architektur auf der gleichen Fläche oder größer

du verdrehst echt alles, ich habe immer wieder geschrieben, dass man für mehr IPC mehr Transistoren erkaufen muss, womit es dann aber eine andere Architektur wird und natürlich wird dann entweder die Fläche größer oder man nimmt eine andere Fertigung mit kleineren Strukturen. Die Tatsache das man dann den gleichen Kern auf einer kleineren Fläche unterbringen kann, kann man auch nutzen um mehr Kerne zu realisieren oder eben für beides, man macht eine neue Architektur mit mehr Transistoren und damit mehr IPC und bringt mehr Kerne unter.

Man sieht dies doch bei den e-Kernen in Alder Lake, die haben schon mehr IPC als Skylake, dürften also auch ähnlich viele Transistoren haben und nur ein Viertel der Größe eines Golden Cove P-Kerns. Nur bringen noch viel mehr Kerne irgendwann auch nichts mehr, da keine Anwendung perfekt über viele Kerne skaliert und manche gar nicht, zugleich hat man aber mit den neuen Fertigungsprozessen nun die Möglichkeit noch viel mehr Transistoren unterzubringen und genau deswegen geht das IPC Wachstum ja auch umso schneller, je kleiner die Fertigungsstrukturen werden, da man eben noch größere Kerne mit noch mehr IPC baut. Ein Golden Cove Kern dürfte etwa 4 mal so viele Transistoren wie ein Skylake Kern haben, kommt aber natürlich bei weitem nicht auf die vierfache IPC von Skylake, was zeigt wie extrem viele Transistoren man aufwenden muss, um die IPC zu steigern.

Es geht ja nicht darum das Intel nicht Fortschritt hatte, wie man an Servern/HEDT gesehen hat

Doch, denn die Aussage war:[/QUOTE]

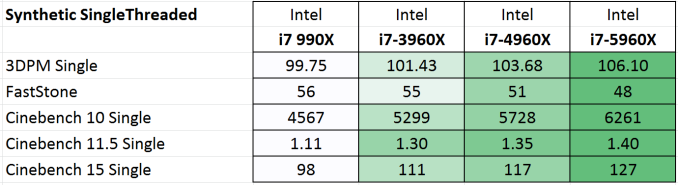

~2008-2016 gab es als Intel meiner Meinung auch nachweislich durch Leistungsvergleiche "IPC" und durch kaum revolutionäre Design, was sich nur durch das shrinking in Leistung umgemünzt hatte... weniger Sprünge als in den letzten 3-4 Jahren als der Wettbewerb fahrt aufgenommen hatte.

Es war nicht vom Mainstream die Rede und bei Intel beinhaltet auch HEDT und Server und warum die IPC in der Zeit weit geringer gestiegen ist als heute, sollte auch klar werden, wenn man sich anschaut wie viele mehr Transistoren pro mm² damals bei einem Shrink möglich waren. Das waren damals auch doppelt so viele, aber absolut viel weniger als heute, weil jeder Transistor damals viel größer war als heute. Das doppelte von einer Millionen sind zwei Mio, aber das Doppelte von einer Milliarden sind zwei Mrd und mit eines Milliarde mehr kann man viel mehr erreichen als mit einer Million Transistoren.

Also...stinkt es dir das es im Mainstream bis 2015/2016 nicht mehr Kerne gab (was der mangelnden Konkurrenz geschuldet war)

Wobei es auch dem Problem mit der 10nm Fertigung geschuldet war, denn mit Cannon Lake war ein 6 Kerner geplant. Die andere Frage ist die der Software, wenn die typische Software für Heimanwender gar nicht in der Lage ist mehr Kerne auszulasten, dann bringt es wenig mehr zu bauen und man verwendet die zusätzlichen Transistoren die man dank eines Shrinks unterbringen kann, besser darauf mehr IPC zu generieren, also mehr Kerne. Dies haben AMDs FX ja auch deutlich gezeigt, 8 langsame Kerne waren gegenüber Intel 4 schnellen Kernen klar im Nachteil!

) ich habe also von 2011 bis 2018 immer die gleiche cpu (überwiegend, nicht ausschließlich) empfohlen, danach mit jeder gen ne andere.

) ich habe also von 2011 bis 2018 immer die gleiche cpu (überwiegend, nicht ausschließlich) empfohlen, danach mit jeder gen ne andere.