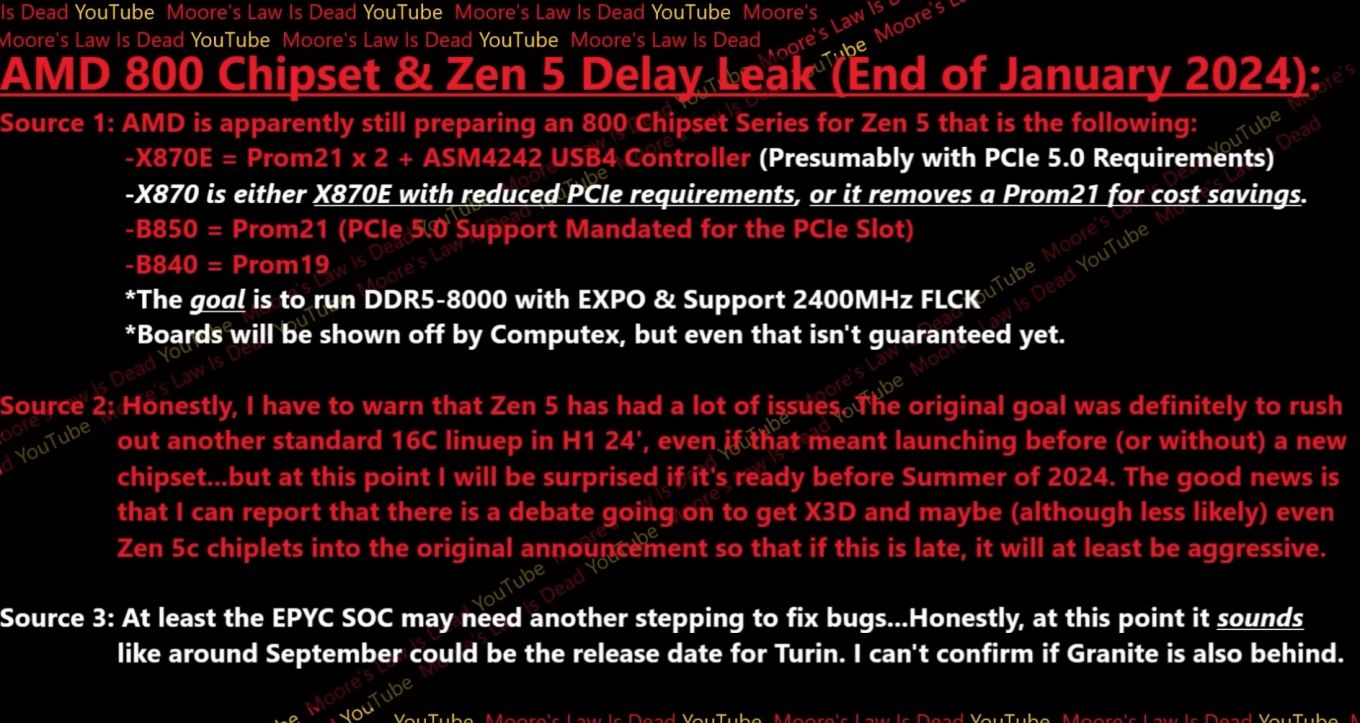

Wobei das mit den 44 nutzbaren PCIe Lanes beim X870E ja auch nicht stimmt, wenn der zwangsweise einen ASM4242 hat, der ja dann 4 PCIe 4.0 Lanes belegt. 44 nutzbare Lanes waren es beim X670E, wo ein ASM4242 eben nicht vorgeschrieben ist. Wieso der X870 (ohne E) jetzt aber nur 36 nutzbare Lanes haben soll, wenn der Unterschied zwischen E und nicht E eigentlich die Geschwindigkeit der PCIe Lanes auf dem Mainboard ist, was sich auf die PCIe 5.0 Lanes direkt von der CPU bezieht, ist mir auch noch nicht klar. Die Chipsätze haben ja sowieso keine PCIe 5.0 Lanes.

Auch frage ich mich ob die Spalte "PCIe 5 insgesamt" insgesamt korrekt ist, da die Aussage auf der AMD Folie darüber ja "PCIe Gen 5 on Grahics and NVMe on all X870 / X870E motherboards" ist, was aber nicht zwangsläufig für die beiden möglichen M.2 Slots mit den Lanes der CPU gelten muss. Wobei sich damit noch mal die Frage stellt, was den X870E vom X870 dann unterscheidet?

Wenn der X870 und X870E jeweils aus zwei Promontory21 bestehen, wir ihr

hier geschrieben habt, dürfte es ja keinen Unterschied bzgl. der Anzahl der PCIe Lanes geben. Sehe gerade das es ein Update gibt, wonach der X870 nur einen Promontory21 Chip hat, aber beide den ASM4242 haben müssen. Dann passt die Anzahl der PCIe Lanes mit 12 aber immer noch nicht, denn jeder Promontory21 Chip 16 PCIe Lanes, von denen offenbar 12 PCIe 4.0 und 4 PCIe 3.0 sind. Beim X670(e) sind es zwei Promontory21 Chips, der einen ist an die CPU angebunden, was 4 oder 16 Lanes belegt, weitere 4 Lanes werden zur Anbindung des zweiten Promontory21 Chips gebaucht, bleiben also 8 Lanes nutzbar und 12 vom zweiten Promontory21 Chip. Mit nur einem Promontory21 Chip hat man also 12 Lanes nutzbar, aber wenn ein ASM4242 verwendet werden muss, sind davon eben nur noch 8 übrig, da ja 4 für die Anbindung der CPU und nochmal 4 für den ASM4242 draufgehen.

Smilie beim Danke Button.

Smilie beim Danke Button.