Werbung

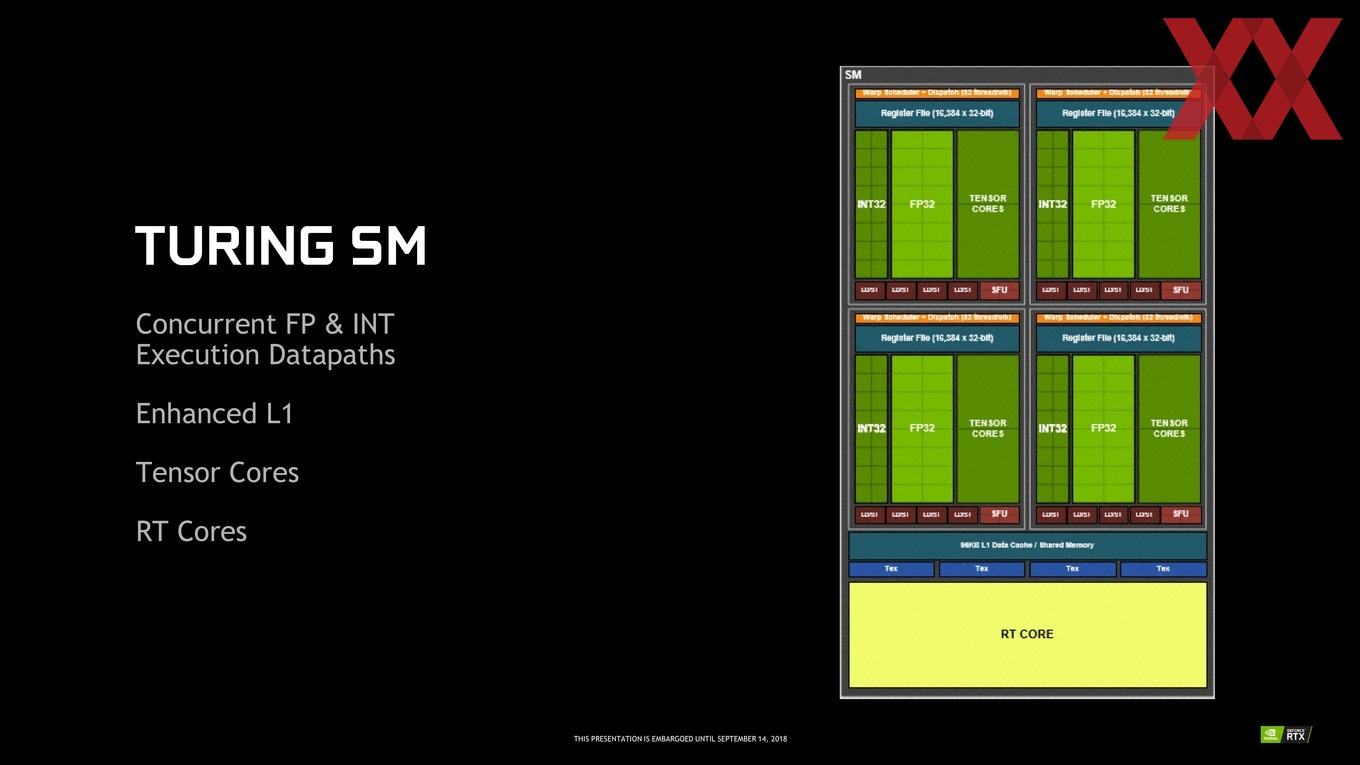

Mit dem Streaming Multiprocessor auf Basis der Turing-Architektur sehen wir eine Weiterentwicklung dessen, was wir im vergangenen Jahr mit der Volta-Architektur gesehen haben. Die Volta-Architektur ist aufgrund der Verwendung von FP64-Recheneinheiten klar für den professionellen Markt konzipiert worden. Was auch wir bisher nicht geahnt haben ist, dass die Tensor Cores eine Rolle bei den Consumer- sprich GeForce-Karten spielen werden. Allerdings hat NVIDIA bei diesen einige Änderungen vorgenommen, auf die wir noch genauer eingehen werden. Richtig gelegen haben wir mit der Erkenntnis, dass NVIDIA zukünftig eine zweigleisige GPU-Strategie fahren wird – wenngleich sich dies auf Volta-Architektur für für die Tesla-Karten und die Turing-Architektur für die Quadro- und GeForce-Serie leicht verändert hat.

Doch was ist nun am Turing SM neu?

Es gibt nun einen gleichzeitigen Pfad für Fließkomma- (FP) und Integer-Berechnungen (INT) in der Pipeline. Darin spielen auch die Tensor- und RT-Cores eine Rolle. Zudem hat NVIDIA die Cache-Hierarchie verändert und gleicht diese in der Turing-Architektur im Vergleich zur Pascal-Architektur nun der Volta-Architektur an.

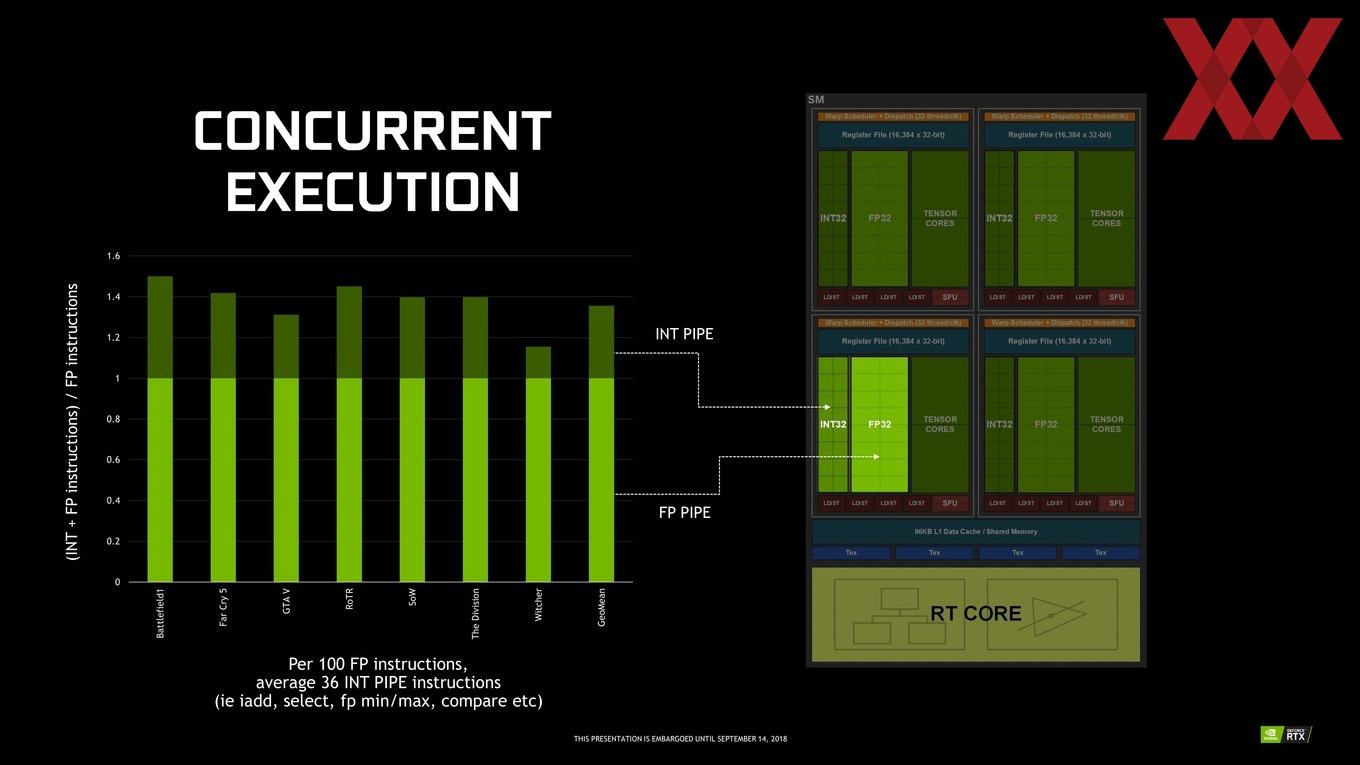

Eine gleichzeitige Berechnung von Fließkomma- und Integer-Datensätzen war bisher in keiner der vorherigen GPU-Architekturen von NVIDIA möglich. NVIDIA hat sich die Ausführung dieser Berechnungen in der Rendering-Pipeline anhand dutzender Spiele angeschaut und konnte dabei feststellen, dass pro 100 FP-Berechnungen etwa ein Drittel an INT-Berechnungen anfallen. Dies entspricht einem Mittelwert, der allerdings auch von 20 % bis 50 % schwanken kann. Ist es nicht möglich FP- und INT-Berechnungen gleichzeitig auszuführen, gibt es hier gewisse Abhängigkeiten, die zu Verzögerungen in der Rendering-Pipeline führen können.

Aus diesem Grund führt NVIDIA mit der Turing-Architektur die gleichzeitige Ausführung von FP- und INT-Berechnungen ein. Der Turing SM besitzt 64 FP32-Einheiten und 64 INT32-Einheiten – nicht ganz entsprechend dem typischen Verhältnis von Anforderungen in der Rendering-Pipeline.

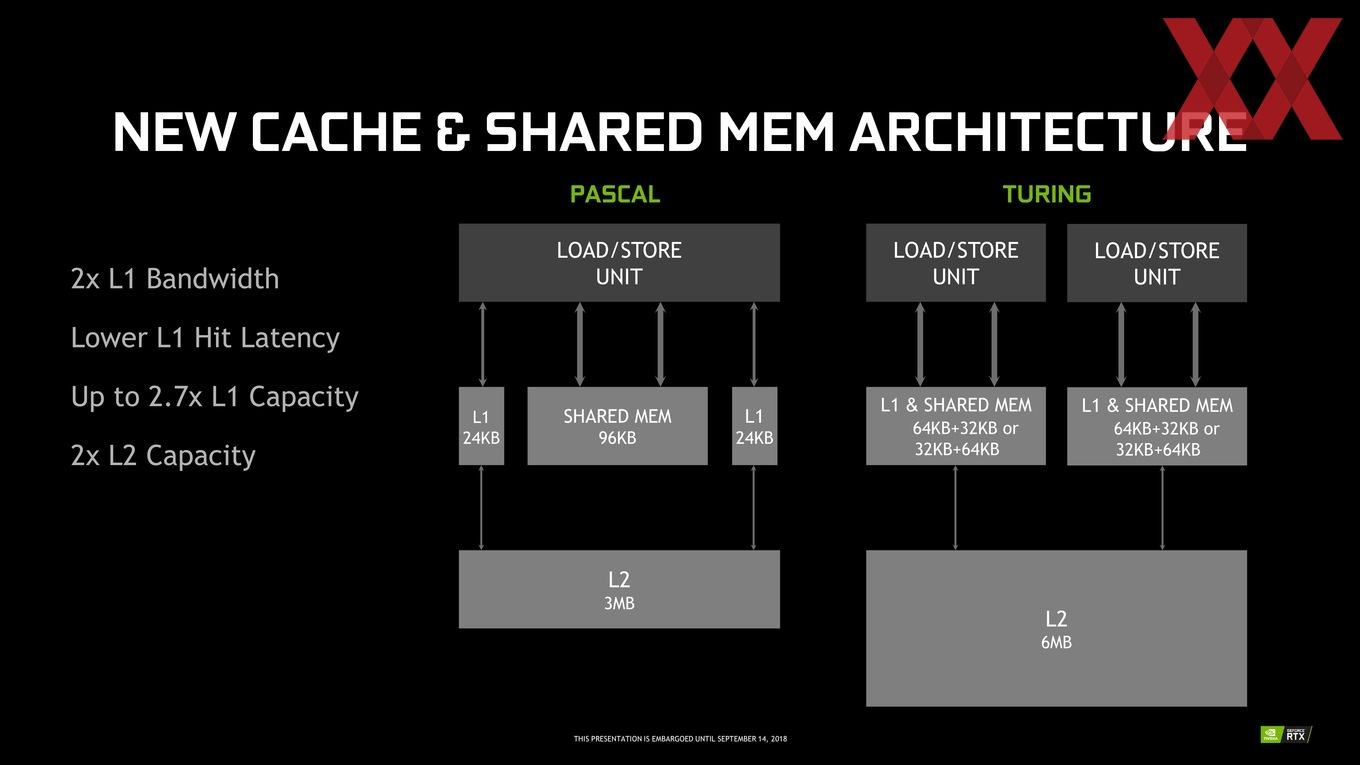

Ebenfalls einige Änderungen gibt es in der Cache-Hierarchie und diese beginnen damit, dass NVIDIA mit der Turing-Architektur die Anzahl der Load/Store-Units reduziert. In der Volta-Architektur sieht NVIDIA pro Volta SM 32 Load/Store-Units vor. Auch die Pascal-Architektur besitzt 32 Load/Store-Units pro SM. Jeder Streaming-Multiprozessor der Turing-Architektur verfügt nun über 16 Load/Store-Units, die für 16 Threads pro Takt die Quell- und Ziel-Adressierung im Speicher und Cache berechnen. Allerdings teilt NVIDIA den L1-Cache und Shared Memory neu auf.

Der L2-Cache wurde bereits mit der Volta-Architektur auf 6 MB vergrößert und findet sich in dieser Form auch in der Turing-Architektur wieder. Änderungen gibt es auch beim L1-Cache – teilweise kennen wir diese ebenfalls bereits von der Volta-Architektur. Handelte es sich bei der Pascal-Architektur noch um einen getrennten L1- und Shared-Cache, legt NVIDIA diese nun zusammen. Dies ist auch schon bei der Volta-Architektur der Fall. L1-Cache und der dazugehörige Shared Memory sind bei Volta 128 KB groß. Die Größe des Shared Memory konnte auf bis zu 96 KB frei konfiguriert werden. Für die Turing-Architektur scheint NVIDIA die Größe wieder etwas zu reduzieren und kommt auf gemeinsame 96 KB, legt diese aber konfigurierbar als 64 KB (L1-Cache) + 32 KB (Shared Memory) oder 32 KB (L1-Cache) + 64 KB (Shared Memory) an.

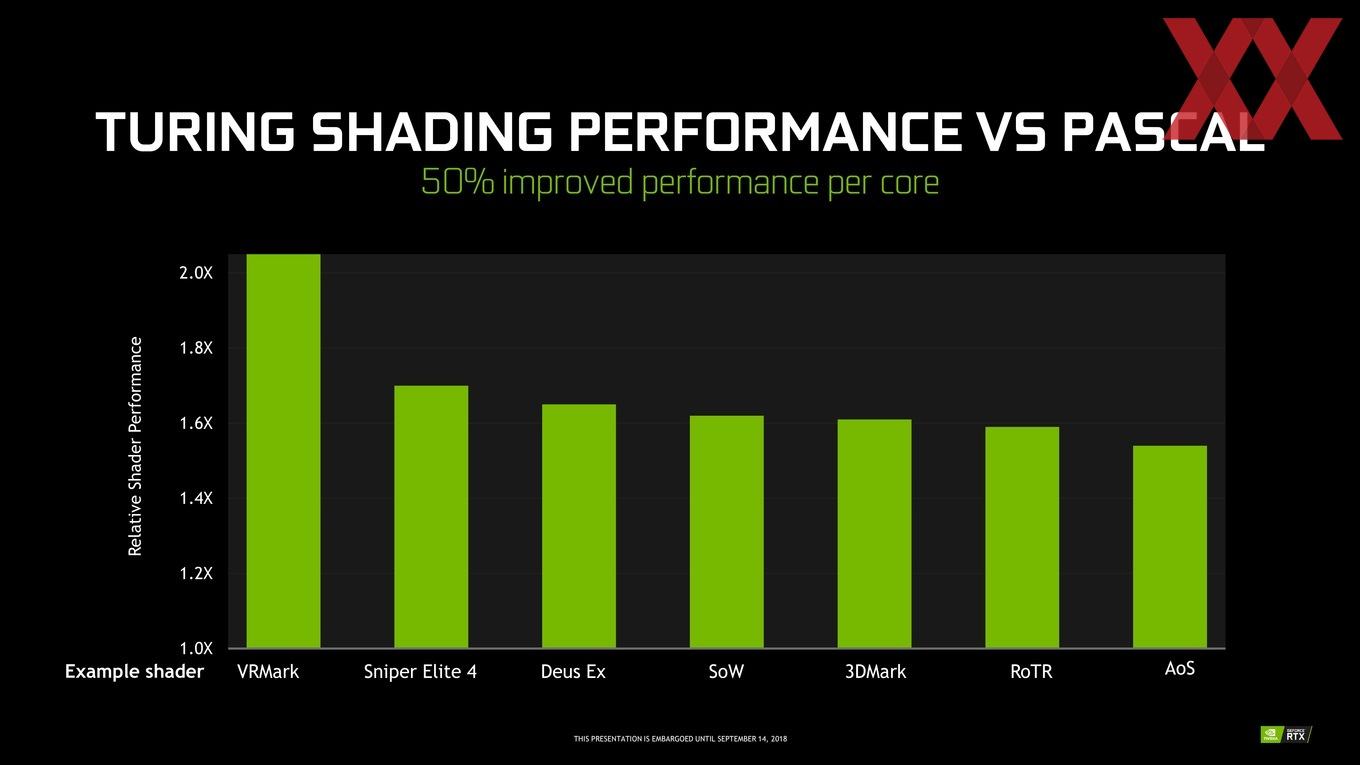

Diese Maßnahmen sollen dazu führen, dass die Shader-Leistung um bis zu 50 % pro „Core“ steigt. Ob sich dies so auch in den Benchmarks zeigen wird, werden wir sehen müssen. Spezielle Vergleiche, die in diese Richtung abzielen, werden wir ebenfalls machen.