Werbung

Im Detail gibt es also viele kleine Änderungen, die teilweise substantieller Natur sind. Schaut man auf den Prozessor als Ganzes und nur auf den Die, sieht alles eigentlich wie gehabt aus. Aber auch hier gibt es teils große Unterschiede.

Ein CCD bestand bisher aus zwei CCX mit jeweils vier Kernen. Die vier Kerne haben sich 16 MB an L3-Cache geteilt, sodass wir von 2x 16 MB L3-Cache pro CCD sprechen. Für Zen 3 wechselt AMD auf ein CCX mit acht Kernen, die sich insgesamt 32 MB an L3-Cache teilen. Es gibt vor allem keine Crossbar mehr zwischen den zwei L3-Cache-Clustern, wenn Kerne aus einem anderen CCX auf den Speicher zugreifen wollen. Dies reduziert die Latenz bei Zugriffen im L3-Cache. Je mehr Kerne auf einen gemeinsamen Cache zugreifen, desto höher werden die Latenzen. Acht Kerne für 32 MB sieht man als derzeitigen Sweet Spot. Alle Kerne im CCX-Complex sind direkt miteinander verbunden. Es gibt acht Slices zu jeweils 4 MB pro Kern.

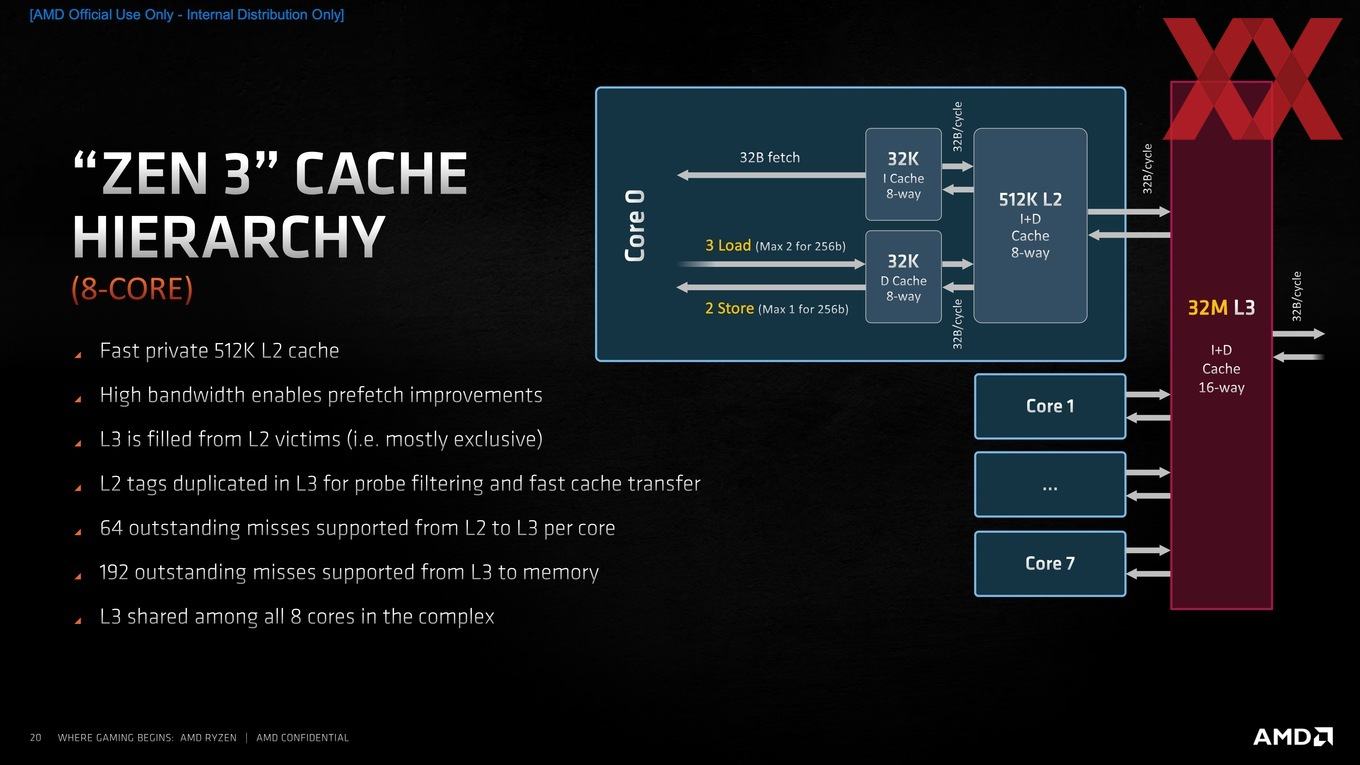

In der Cache-Hierarchie beginnt alles mit Daten aus dem 32 kB großen L1-Instruction-Cache. Über die Load- und Store-Einheiten können Daten aus dem L1-Data-Cache (ebenfalls 32 kB groß) gelesen oder in diesen geschrieben werden. Pro Taktzyklus können hier 32 Byte gelesen, bzw. geschrieben werden. Zwischen dem L1- und L2-Cache werden die Daten ebenfalls mit 32 Byte pro Takt ausgetauscht. Jedem Kern stehen 512 kB an privatem L2-Cache zur Verfügung, der für Daten und Instruktionen genutzt werden kann.

Zwischen dem L2- und L3-Cache werden die Daten wieder mit 32 Byte pro Taktzyklus ausgetauscht, sodass die hohe Bandbreite vom L3-, über den L2- bis in den L1-Cache weitergegeben wird. Der L3-Cache wird per Shadow Tags so aufgeteilt, dass Kerne die Daten untereinander austauschen können.

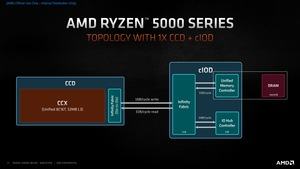

Wie bei den Ryzen-3000-Prozessoren gibt es eine bestimmte Topologie der Ryzen-5000-Prozessoren, die allerdings weitestgehend identisch ist. Ein CCD besteht nun allerdings aus einem CCX und nicht mehr aus bis zu zwei. Es bleibt jedoch bei den acht Kernen und 32 MB an L3-Cache. Die Zusammenführung zweier CCX in ein solches Cluster ist der Kernpunkt. Das Chiplet-Design bleibt also identisch und dies gilt auch für den IOD und dessen Anbindung. Per Infinite Fabric kann mit 16 Byte pro Taktzyklus vom CCD an den IOD geschrieben und vom IOD zum CCD mit 32 Byte pro Taktzyklus gelesen werden. Dies führt natürlich wieder dazu, dass bei nur einem CCD (wie beim Ryzen 7 5800X und Ryzen 5 5600X) die Schreibrate gegenüber der Leserate weiterhin nur halb so hoch ist. Intern kann über den Infinite Fabric mit 32 Byte pro Taktzyklus zum Speichercontroller kommuniziert werden, allerdings erfüllen die Prozessoren mit nur einem CCD die Anforderungen an die Bandbreite für das Schreiben nicht.

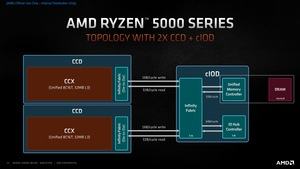

Kommen zwei CCDs zum Einsatz (Ryzen 9 5900X und Ryzen 9 5950X), schreiben diese mit 2x 16 Byte pro Taktzyklus in den Speichercontroller, gelesen werden kann trotz theoretischen 2x 32 Byte aber nur mit insgesamt 32 Byte pro Taktzyklus.

Der IOD ist vollständig identisch zur Ryzen-3000-Serie, im Detail kann es kleinere Detailverbesserungen in der Fertigung gegeben haben. Der IOD dürfte sparsamer arbeiten können, weil weniger Daten von den CCX/CCDs übertragen werden müssen. Dieses – wenn auch kleine Power-Budget des IOD – steht letztendlich wieder dem oder den CCDs zur Verfügung. Ob man die geringere Leistungsaufnahme des IOD aber überhaupt praxisrelevant aufzeigen kann, ist fraglich.

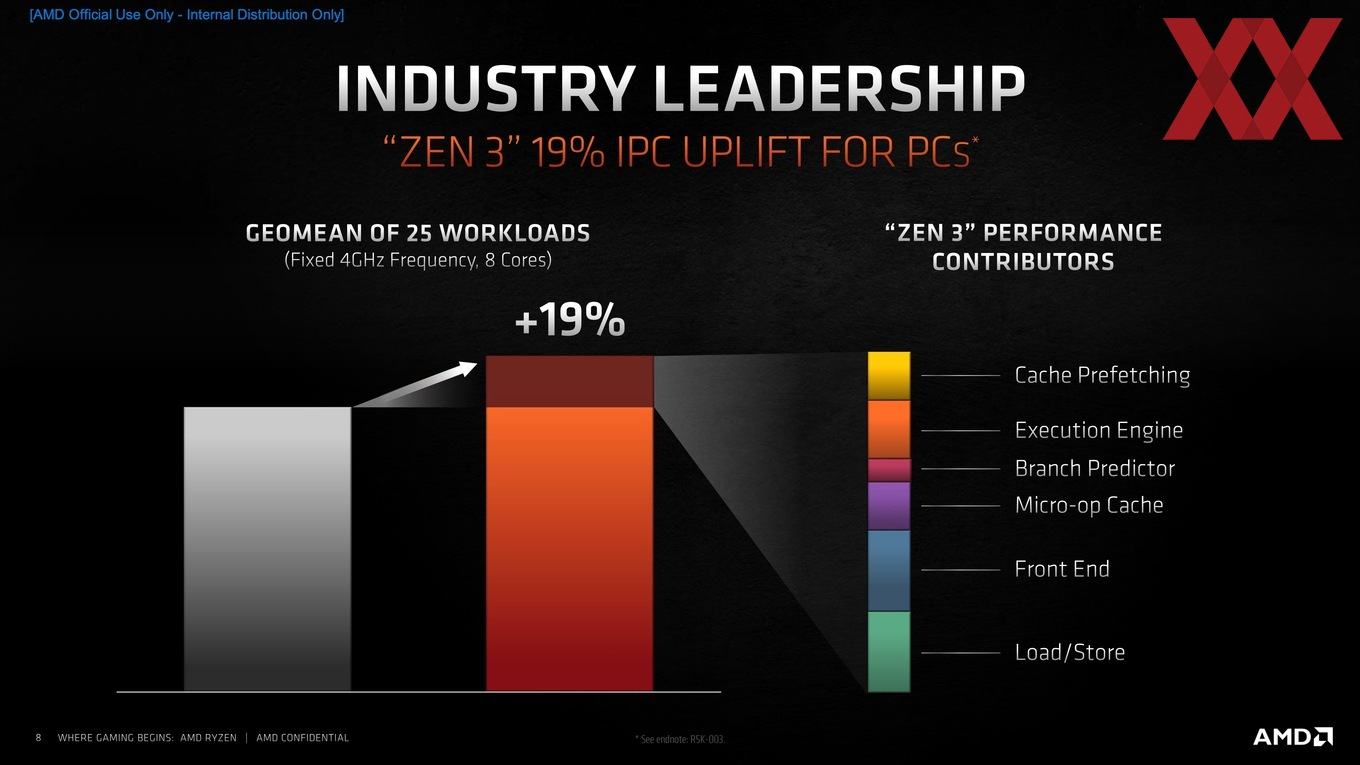

+19 % IPC

Nur durch die Verbesserungen in der Architektur erreicht AMD ein IPC-Plus von 19 %. Über die vergangenen zwei Seiten haben wir diese genauer beschrieben und versucht, deutlich zu machen, was AMD hier für Änderungen in die Zen-3-Architektur hat einfließen lassen.

Die +19 IPC-Leistung ermittelt AMD aus einem Mittel verschiedener Benchmarks bei einem identischen Takt von 4 GHz und acht Kernen für Zen 2 und Zen 3. In der Grafik ist gut zu erkennen, wie AMD die Zugewinne in etwa auf die verschiedenen Bereiche aufteilt. In Kombination aus den Verbesserungen im Cache, den einzelnen Funktionseinheiten, dem Micro-Op-Cache, dem Frontend insgesamt und den Load/Store-Einheiten ergeben sich die Leistungszuwächse von Zen 3. Eine einzelne Maßnahme hätte natürlich nicht den gleichen Effekt, wie er im einzelnen dargestellt wird, da all diese Schritte zusammengreifen müssen, damit der positive Effekt zum Tragen kommt.

Aufgeschlüsselt auf die einzelnen Anwendungen zeigen sich die Vorteile, die sich für die Zen-3-Architektur ergeben. Einige profitieren nur um Bereich von etwa +10 %, andere wiederum deutlich mehr als 20 %. Hier tauchen dann vermehrt Spiele auf und dies ist eben die Kategorie von Anwendungen, die AMD mit Zen 3 in den Fokus rückt.