du sagtest ja das die Bandbreite limitieren würde bei einem 8Modul design

Das habe ich nie gesagt. Ich sagte, der 8-Modul Bulldozer (MCM Orochi) erfordert Quad-Channel, rein hardwareseitig (Board), nicht performanceseitig. Ob Dual-Channel bei einem 8-Modul Bulldozer die Bandbreite limitiert, hängt wie so oft von der jeweiligen Anwendung ab und natürlich von den Speichermodulen.

Da ja der speichercontroler in der CPU sitzt.. Ist es nicht einfach möglich auch quadchannel auf z.B. nem AM3 board zu fahren?? Weil die boards haben ja 4 speicher steckplätze und der speichercontroler ist ja eh in der CPU!

Richtig, das ist möglich. Aber es gibt halt keine AM3 Boards mit Quad-Channel (dürfte bei AM3+ nicht anders werden). Hinzu kommt, dass Server CPUs im LGA Package ausgeliefert werden, Desktop CPUs im PGA Package. Selbst wenn ein AM3 Board Quad-Channel unterstützten würde, müsste AMD erstmal Quad-Channel CPUs im AM3 Package anbieten.

Warum will Undertaker 1 im Bulldozer Thread über den selbst von AMD bestätigten nicht ganz echten DIE Shot Llano sprechen, um dann dies auf Bulldozer zu produzieren? Ist doch Bulldozer eine neue Architektur und Llano ein verbesserter Athlon II.

Wie soll man das verstehen?

Er will mit seinem Unfug halt auch zum x-ten mal AMD Threads zuspammen, damit jeder seine verquere Weltansicht lesen kann. Einmal reicht halt nicht. Ziemlich peinlich und Kindergarten pur.

Undertaker 1

bla bla ... bla bla ... bla bla bla

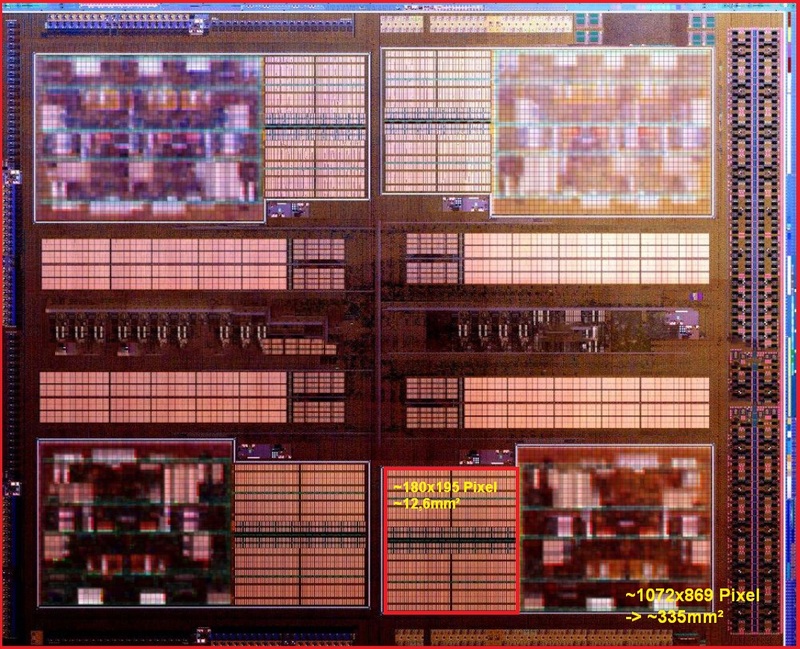

Irrelevant. Es gibt keine gesicherten Informationen, wie viel Fläche pro L2 gebraucht wird. Anhand von Llano lässt sich da überhaupt nichts schlussfolgern. Zudem scheinen die L2 Bereiche auf dem Orochi Die Shot gefaked. Die oberen sind zB deutlich kleiner. 335 mm² ist jedenfalls unrealistisch. Es sollte eher Richtung 300 mm² bzw darunter gehen.

Btw, du musst das nicht permanent wiederholen (zum 8. mal jetzt?). Wir haben deinen Unfug schon beim ersten mal verstanden.

Muss man nicht, nur wie die vergangeheit mit Athlon64 FX, Quad FX usw gezeigt hat will AMD auch in diesem kleinen Marktsegment gerne mitmischen - schließlich gehts da ums Prestige

Athlon FX = AMD Anno 2003

AMD Anno 2010 != AMD Anno 2003

Wenn AMD heutzutage in diesem Bereich mitmischen wöllte, hätte man bereits Magny-Cours als Option für AM3 im Portfolio. Angesichts von Entwicklungen wie Bobcat oder Llano ist doch klar, wohin die Reise bei AMD im Client Markt geht -> Low Power, Mainstream, Performance. High-End gibt es nur bei Servern. Wobei selbst das relativ ist angesichts von IBMs zSeries & Co.

Deine AMD-Diskussion im SB-Thread wurde von dir gestartet - fällt dir etwas Entscheidendes auf?

Deine AMD-Diskussion im SB-Thread wurde von dir gestartet - fällt dir etwas Entscheidendes auf?