Werbung

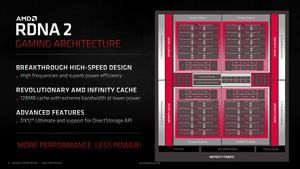

Der Infinity Cache ist mit seiner Kapazität von 128 MB ein vielerlei Hinsicht ein Novum. Man könnte ihn als L3-Cache bezeichnen und im Grunde erfüllt er auch die Funktion einer weiteren Cache-Ebene, die wir bei GPUs in dieser Form bisher aber nicht gesehen haben.

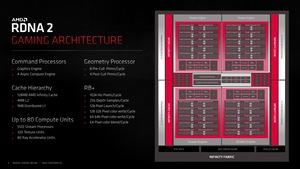

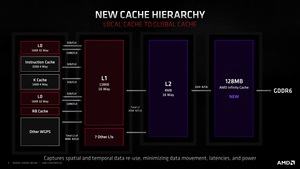

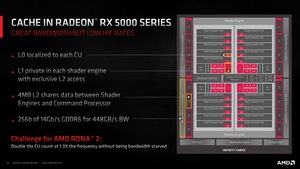

Für die meisten GPUs kommt ein dreistufiges Cache-Design zum Einsatz. Es gibt einen L0-Cache, der exklusive der Compute Unit zur Verfügung steht. Hinzu kommt ein L1-Cache, der wiederum einer Shader Engine zugeteilt wird und ein L2-Cache, der zwischen den Shader Engines und den Command Prozessoren den Datenaustausch ermöglicht. Auf den L2-Cache folgt bei RDNA (und auch vielen anderen GPU-Architekturen) der Grafikspeicher, der über ein Speicherinterface angebunden ist.

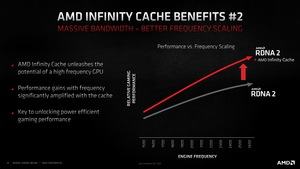

Für Big Navi hat AMD die Anzahl der Shadereinheiten verdoppelt, man wollte aber nicht das Speicherinterface verdoppeln, um die Shader mit Daten füttern zu können. AMD hätte also eigentlich ein 512 Bit breites Speicherinterface für Big Navi benötigt. Ein 512 Bit breites Speicherinterface hätte aber einen gewissen Anteil an der Chipgröße für sich beansprucht und zudem die Leistungsaufnahme nach oben getrieben, sodass man sich auf die Suche nach einer Alternative gemacht hat.

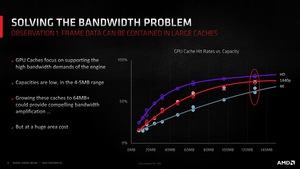

In Performance-Analysen hat sich AMD angeschaut, welchen Einfluss ein großer Cache auf die Leistung hat bzw. welche Datenmengen man hier abfangen kann, indem häufig genutzte Daten anstatt aus dem VRAM aus einem großen Cache bezogen werden. Die Hit Rate, also die Anzahl der erfolgreichen Zugriffe auf Daten, die bereits im Cache liegen, steigt, von den heute typischen 4 bis 6 MB im Endkundenbereich (Radeon und GeForce) ausgehend, auf mehrere Dutzend und schließlich mehr als 100 MB zunächst linear, dann etwas abgeflacht an. Die von AMD gewählten 128 MB sind eine Art Sweet-Spot, der nur noch bei immer höheren Auflösungen weiter nach oben gerückt werden kann. Ein Cache mit mindestens 64 MB wäre die Mindestgröße, die man hätte realisieren wollen.

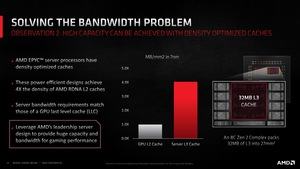

Auch hier hat sich die RTG-Group bei AMD Anleihen aus der Zen-Entwicklung genommen, wo ein 32 MB großer L3-Cache in den CCDs zum Einsatz kommt. Große Caches haben sich auch hier als sinnvoll erwiesen und konnten wirtschaftlich sinnvoll umgesetzt werden. Für Big Navi verwendet AMD ein SRAM, welches auf eine hohe Packdichte optimiert ist. So konnte man die 128 MB des Infinity Cache wirtschaftlich sinnvoll umsetzen.

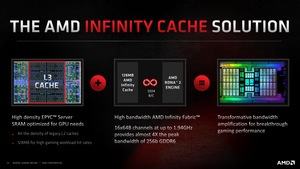

Den Infinity Cache musste AMD natürlich auch entsprechend schnell anbinden, damit dieser seine Funktion erfüllen kann. Insgesamt sind die 128 MB über 16 Kanäle mit jeweils 64 Byte pro Taktzyklus angebunden. Der Infinity Fabric arbeitet mit 1,94 GHz, was dann letztendlich einer Bandbreite von 0,9933 TBit/s entspricht.

Nicht nur die Speicherbandbreite ist deutlich höher, es wird auch für Zugriffe weniger Strom verbraucht. Pro Bit sprechen wir von 7 bis 8 pJ für GDDR6-Zugriffe und von 1,3 pJ für Zugriffe im Infinity Cache. Bei einer Hit Rate von 58 % für Spiele in 4K-Auflösung ergebt sich daraus eine um den Faktor 2,4 effizientere Bandbreite pro Watt für Zugriffe auf den Speicher.

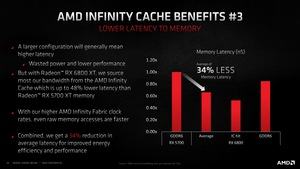

Neben der höheren Bandbreite und der besseren Effizienz ist der Infinity Cache natürlich auch deutlich näher an den eigentlichen Recheneinheiten und hat daher geringere Latenzen aufzuweisen. Diese sind im Vergleich zu GDDR6 um 34 % niedriger, wenn man die Hit Rate mit einbezieht.

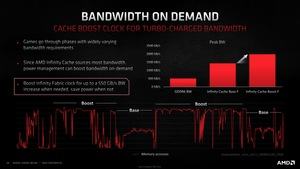

Um die Bandbreite den Anforderungen anpassen zu können, kann der Takt des Infinity Fabrics verändert werden. So können dem Infinity Cache bis zu 550 GB/s an Bandbreite zusätzliche zugewiesen werden – ein Infinity Cache Boost.