Werbung

Auch wenn wir bereits einige Änderungen erwähnt haben – diese sind im Vergleich zu Zen 3 weitaus umfangreicher als gedacht und daher einen gesonderten Blick wert.

Genau wie bei der CPU-Architektur setzen sich die Designer gewisse Ziele, die entsprechend der weiteren Planung auch den Weg vorgeben. Für Zen 4 stand ein gewisses IPC-Plus im Lastenheft, aber auch die Latenzen sollten reduziert werden. Zugleich war geplant, den L2-Cache zu verdoppeln, während der L3-Cache unangetastet blieb. Neben der reinen Leistung war Steigerung der Effizienz eine weitere Maßgabe.

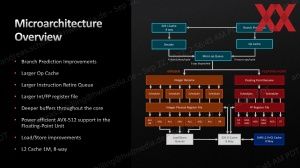

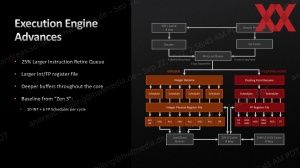

Die Sprungvorhersage ist einer der Punkte, der mit der Zen-4-Architektur überarbeitet und verbessert wurde. Pro Taktzyklus können nun zwei Sprungvorhersagen gemacht werden. Der Op Cache fällt um 68 % größer aus und kann nun neun statt acht Micro-Ops pro Taktzyklus in die Micro-Op Queue liefern. An den Funktionseinheiten für ganzzahlige und Fließkomma-Operationen gibt es keine Änderungen. Die Register Files fallen allerdings größer aus. Die Fließkomma-Einheiten sind unter anderem dazu verantwortlich, die AVX-512-Befehlssätze auszuführen.

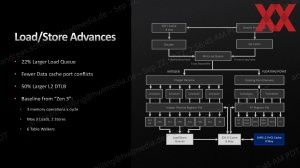

Im Backend gibt es Detailverbesserungen in den Load/Store-Einheiten, die eine um 22 % größere Queue vorzuweisen haben. Am D-Cache wurden Optimierungen durchgeführt, sodass es zu weniger Konflikten bei Zugriffen auf die Daten kommt.

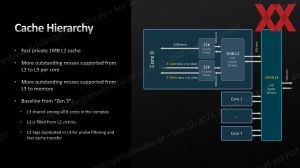

Die Cache-Hierarchie bleibt fast identisch. Der L2-Cache wird auf 1 MB verdoppelt. Der L1-Cache kann weiterhin 32 kB an Instruktionen und Daten fassen. Beide Bereiche des L1-Caches können 32 Byte an Daten pro Taktzyklus mit dem L2-Cache austauschen. Dieser wiederum erreicht ebenfalls 32 Byte an Daten pro Taktzyklus im Austausch mit dem L3-Cache.

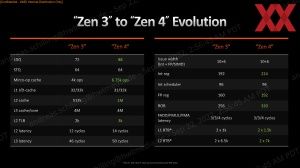

Die eben erwähnten Änderungen in Zahlen ausgedrückt, zeigen die obigen Tabellen. Dort zu sehen sind der größere Micro-Op Cache, L2-Cache, L2 TLB, Integer Register, Fließkomma Register sowie L2 und L2 BTB.

Aber es gibt auch Punkte, in denen Zen 4 auf dem Papier schlechter dasteht, als Zen 3. So vergrößert sich die L2-Latenz von 12 auf 14 Taktzyklen. Beim L3-Cache sind es nun 50 anstatt 46 Taktzyklen.

Ein echtes Highlight soll die Integration von AVX-512- in die Zen-4-Architektur sein. Wie schon in der Einleitung erwähnt, setzt AMD dies in Form einer 256-Bit-Operation um – zweimal ausgeführt ergibt dies 512 Bit. Laut AMD gibt es keinerlei Einfluss auf die Taktfrequenz des Kerns, wenn dieser AVX-512-Befehlssätze ausführt. Dies ist bei den Intel-Prozessoren häufig anders.

Unterstützt werden die AVX-512-Befehlssätze:

- AVX512F

- AVX512DQ

- AVX512_IFMA

- AVX512CD

- AVX512BW

- AVX512VL

- AVX512_VBMI

- AVX512_VBMI2

- GFNI

- AVX512_VNNI

- AVX512_BITALG

- AVX512_VPOPCNTDQ

- AVX512_BF16

Die Stärken von AVX-512 wird AMD wohl erst bei den EPYC-Prozessoren ausspielen können. Für die Ryzen-7000-Prozessoren spielt es nur eine Nebenrolle und dennoch werden wir dedizierte Benchmarks ausführen und das Thema noch genauer beleuchten.